DAC1794-嘨乮壖乯偼幚尰偡傞偺偐丠丂2007.4.5

偙偲偺巒傑傝丠

側偵偘偵BBS偵彂偒崬傫偩撪梕偑偙傟丅

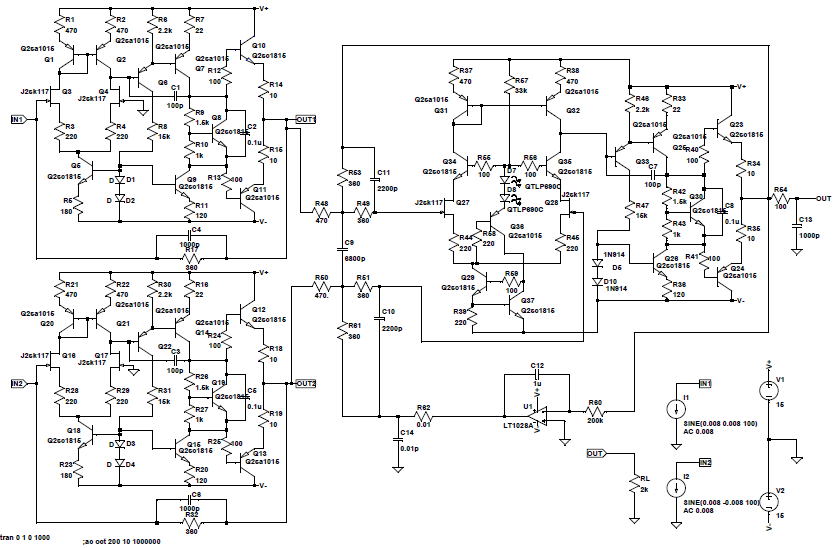

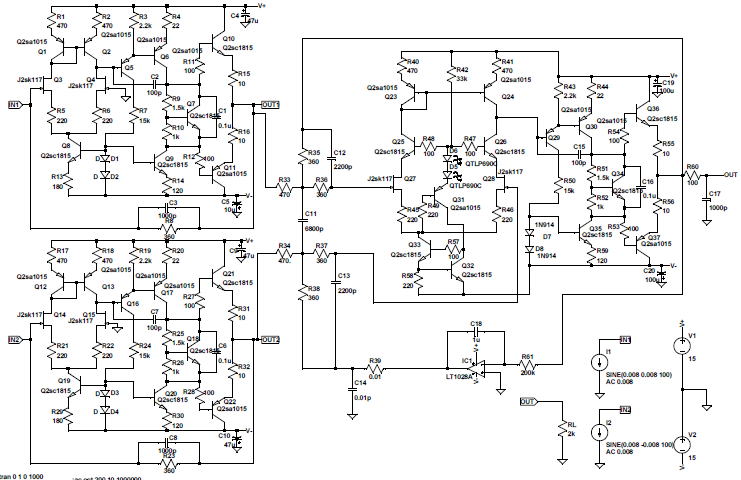

| 丂DAC1794D偵偮偄偰偼丄偪傚偭偲拑栚偭婥傪弌偟偰DAI崬傒偱俀僷儔亅儌僲峔惉乮幚幙偼係僷儔乯側傫偐偵偟偨傜柺敀偄偐側丠偲偼巚偭偨傝偟偰乮徫乯丅栤戣偼俬倁偵棳傟傞揹棳偼嵟戝40mA偵側傞偺偱OP傾儞僾扨懱偱偼偩傔偱丄僶僢僼傽乕傪捛壛偡傞偐偁傞偄偼僨傿僗僋儕乕僩偵偡傞偐丒丒丒偁偁丄峫偊弌偟偨傜戝曄偩乣両両 |

DAC1794偺嵼屔偑柍偔側偭偰丄嵞惢嶌偺偛梫朷傪捀偒傑偟偨偑丄愜妏嶌傞偺側傜儕僯儏乕傾儖偟偨偄両

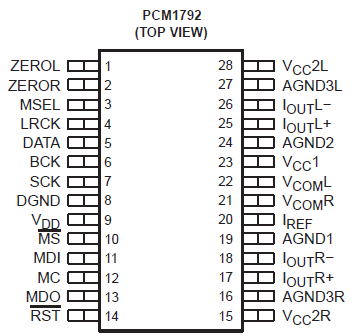

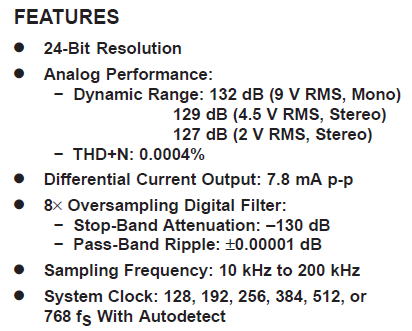

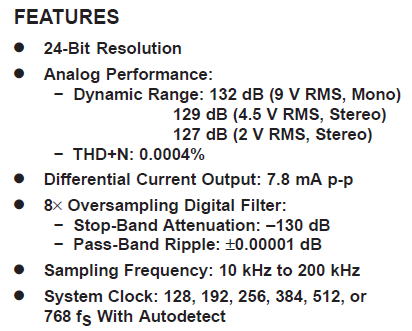

PCM1794偼旕忢偵僐僗僩僷僼僅乕儅儞僗偵桪傟偨DAC-IC偱丄2000墌偪傚偭偲偵傕偐偐傢傜偢丄撪晹偵24Bit偺

DAC偑係屄偼偄偭偰偄偰嵎摦偺僗僥儗僆弌椡偑壜擻偩丅

丂壒偲偟偰傕暘夝擻偵傕桪傟丄偝傜偵儂僢僩側姶偠偑偡傞偺傕摿挜偩偲偍傕偆丅PCM1704偺僋乕儖側壒偲偼屄惈偑堘偆揰傕柺敀偄丅

丂埲慜偵儕儕乕僗偟偨DAC1794D偼傾僫儘僌夞楬偼偡傋偰僆儁傾儞僾傪梡偄偨傕偺偱丄惢嶌忋偺僩儔僽儖偼彮側偄偺偩偑丄

帺嶌偲偟偰偼柺敀傒偵寚偗傞偲偙傠傕偁傞乮僆儁傾儞僾傪庢傝懼偊傜傟傞偲偄偆儊儕僢僩偼偁傞乯丅

愜妏偩偐傜丄弌椡抜傪僨傿僗僋儕乕僩偵偡傟偽椙偄偐側丄偲偼巚偄偮偮傕丄偪傚偭偲僪儔僀價儞僌僼僅乕僗偑偐偐傜側偄丅

偦傫側側偐丄偙傫側彂偒崬傒傕捀偄偨丅

DAI偑DIR9001偱丄DAC偑PCM1792A偺儌僲巊偄偺怴DAC偺婇夋偼偳偆偱偟傚偆偐丠#6525偱偺彂偒崬傒偺敪揥宍偱丅

傾僫儘僌晹偼僼儖僨傿僗僋儕乕僩偱OP傾儞僾偱偼尩偟偄PCM1792A偺揹棳弌椡偱傕崅惛搙偵IV曄姺偟丄

PCM1792A偺惛搙傪懝側傢側偄傛偆偵傾僫儘僌怣崋偵偱偒傞偲尰峴晹昳偱惢嶌偱偒傞僼儔僌僔僢僾婡偵側傞偺偱偼側偄偐偲巚偄傑偡丅

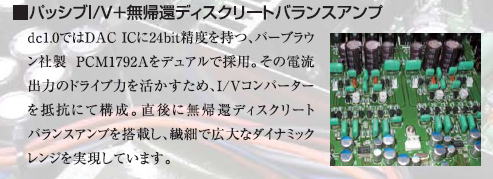

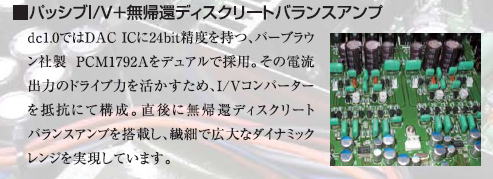

偄傗扨偵丄SOUL NOTE偝傫偺dc1.0偑偡偽傜偟偄惢昳側偺偱丄傾儅僠儏傾偱偳偙傑偱嬤偯偗傞偐偭偰巚偭偨偩偗側傫偱偡偑丒丒丅

http://www.kcsr.co.jp/soulnote/products/dc1.pdf |

側傞傎偳丅悽偺拞偵偼偦傫側惢昳傕偁傞傕傫偩丅URL傪擿偄偰傒傞偲丄偙傫側惢昳僇僞儘僌偑偱偰偒偨丅

僔儞僾儖側柺峔偊偱偡偹丅

偱丄娞怱偺夞楬偼偙傫側愰揱偑偁傞丅

傕偆彮偟鉟楉側幨恀偩偲椙偄偺偱偡偑丒丒丒

僷僢僔僽俬倁傪攧傝偵偟偰偄傞傛偆偩偑丄PCM1792側偳偺弌椡傪僷僢僔僽掞峈偱庴偗偰偟傑偆偲丄

弌椡揹埑偑曄摦偟偰榗傒偑敪惗偡傞壜擻惈偑偁傞傫偠傖側偄偐側丠

傗偭傁傝傾僋僥傿僽俬倁偵偟側偄偲偄偗側偄丄偲傕俛俛俽偱巜揈偑偁偭偨丅

斾妑揑娙扨側夞楬偱偺俬倁偲側傞偲丄偳偆側傞偩傠偆偐丒丒丒丒偙偙偑娞偺傛偆偱偡丅

偱傕丄偙偆偄偭偨巗斕昳偑偁傞偲丄傕偆偪傚偭偲忋傪偄偔傕偺傪埨偔嶌偭偰傒偨偄偲偄偆婥偑僼僣僼僣婲偙偭偰偒傑偡丅

偲側傞偲丄俬倁夞楬懸偪乮by丂俼丏偝傫乯偐側乮徫仌恖擟偣儌乕僪乯丅

俹俠俵侾俈俋俀丂倁俽丂俹俠俵侾俈俋係

偪側傒偵PCM1794偲PCM1792偲偼壗偑堘偆偺偩傠偆丠

巇條彂傪傒偰偄傞偲摿挜帺懱偼摨偠撪梕偩丅偟偐偟丄偙傟偩偗偺惈擻偑愇扨懱偱傞偺偼偡偽傜偟偄傕偺偩丅

偦傟偵偟偰傕俢儗儞僕偑132dB偭偰丄偳偆傗偭偰寁傞傫偩傠偆丠應掕婍帺懱偺俢儗儞僕偑偦傟傛傝椙偄偭偰帠偱偡傛偹丅

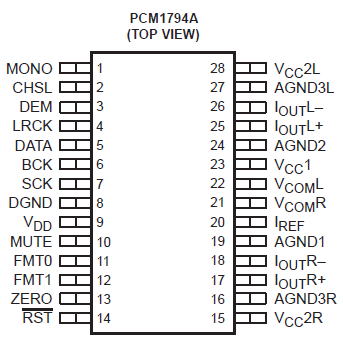

偱丄榖偟偼尦偵栠偭偰1792偲1794偺壗偑堘偆偐偲偄偊偽丄僨傿僕僞儖擖椡晹偑偪偑偆傛偆偱偡丅

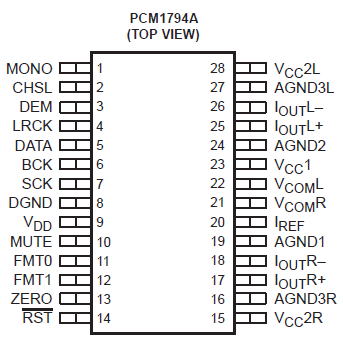

傾僫儘僌弌椡晹乮PIN15乣28)偼傑偭偨偔摨偠偱偡偑丄嵍懁偺僨傿僕僞儖擖椡晹乮Pin1乣侾係乯偑堎側傝傑偡丅

丂

丂

PCM1794A偲PCM1792丅娫堘偄扵偟丠

PCM1792偑Pin11乣13偱俁慄偱偺僜僼僩惂屼傪慜採偵偟偰偄傞偺偵懳偟偰丄PCM1794偑僴乕僪愝掕偺傒偺堘偄偱偡偹丅

傕偪傠傫僜僼僩惂屼偑偱偒傟偽丄怓乆偲儌乕僪摍偑曄峏偱偒傞偺偼柺敀偄偺偱偡偑丄儅僀僐儞偑昁恵偵側傞揰偼

偡偙偟僴乕僪儖偑崅偔側偭偰偟傑偄傑偡丅僔儞僾儖偵嶌傞偵偼PCM1794偑埖偄堈偦偆偱偡丅

偱傕丄僷僞乕儞愝寁偡傞偲偒偼偳偪傜偱傕巊偊傞傛偆偵偟偰偍偗偽丄偁偲偁偲柺敀偄偐側丠

偝偭偦偔俬倁夞楬傪捀偒傑偟偨丅

偦偆偙偆偟偰偄傞娫偵丄俼丏偝傫偐傜俬倁夞楬偺採埬偑偁傝傑偟偨乮偁傝偑偲偆偛偞偄傑偡乯丅

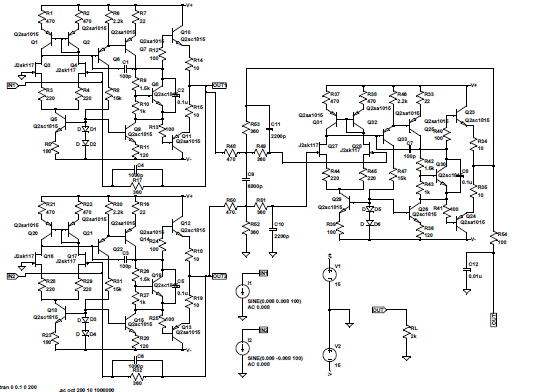

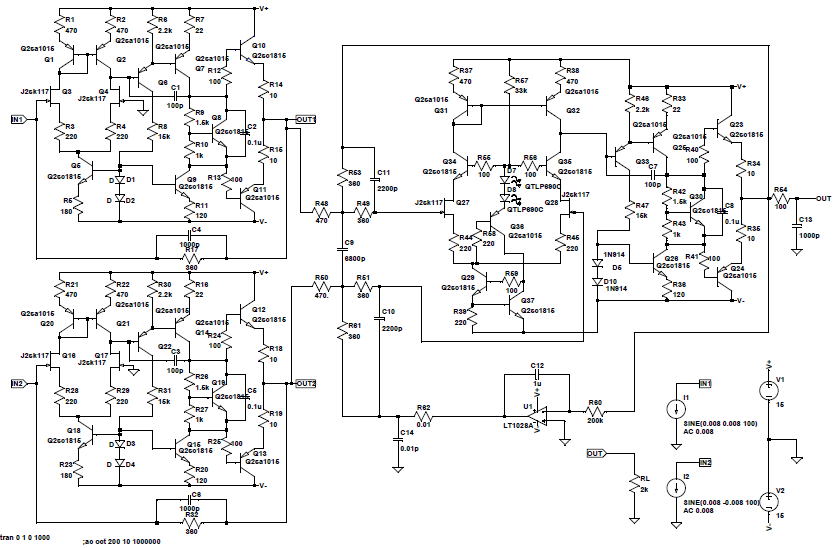

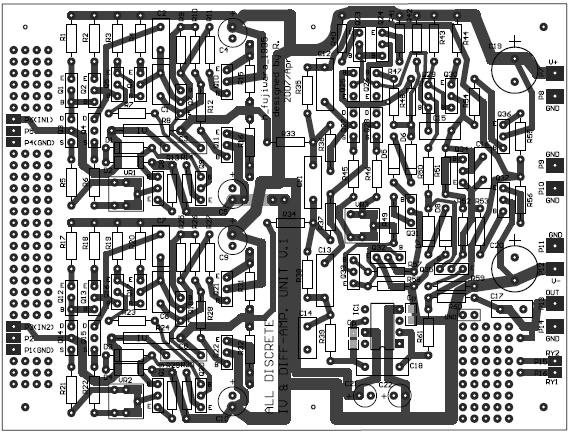

夞楬峔惉偲偟偰偼HPA-2傪彮偟僔儞僾儖偵偟偨傕偺偵側傞傛偆偱偡丅偲偄偆偙偲偼掅榗慱偄偱偟傚偆偐丅

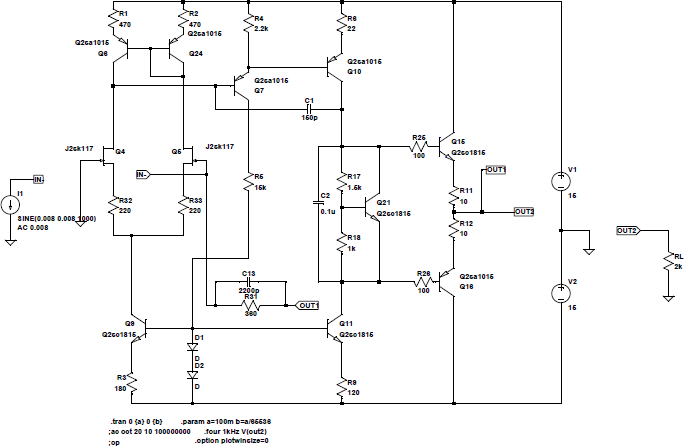

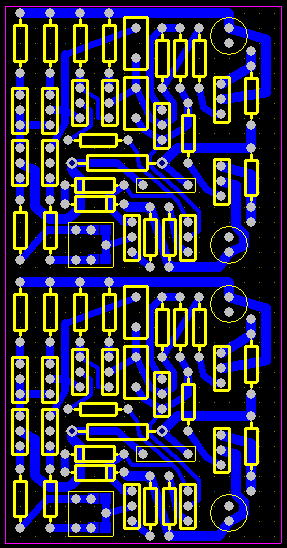

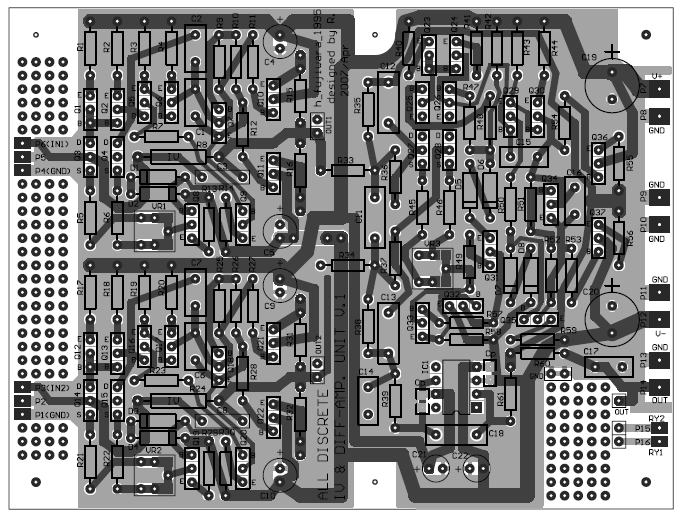

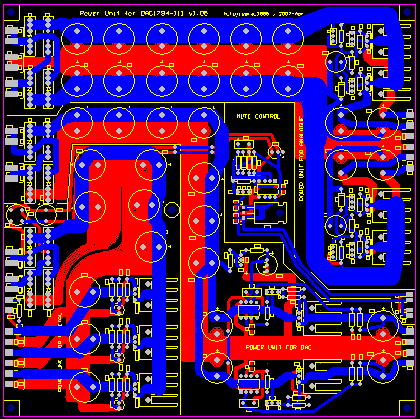

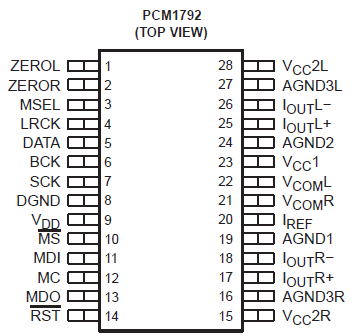

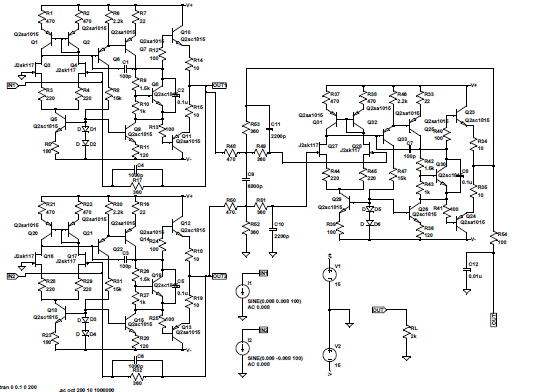

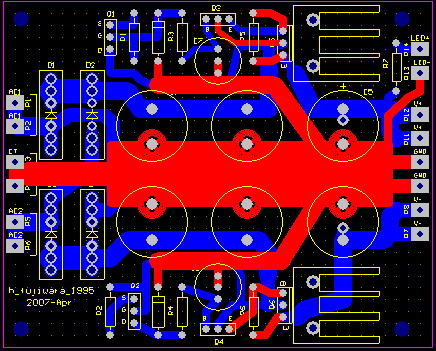

掞峈偑侾係杮丄僩儔儞僕僗僞偑侾侾屄偺峔惉偱偡丅

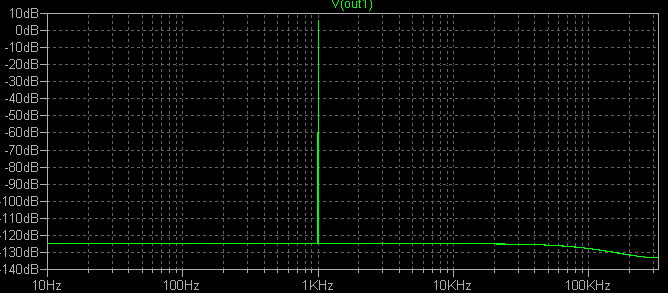

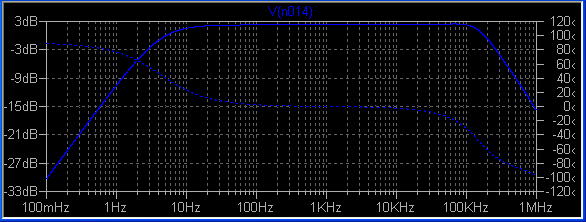

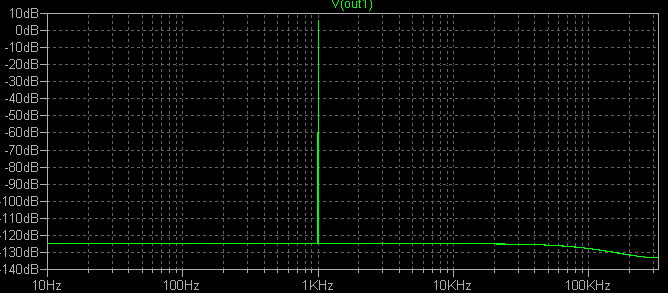

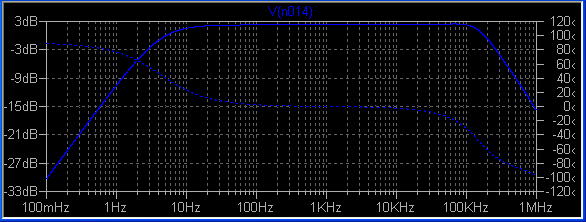

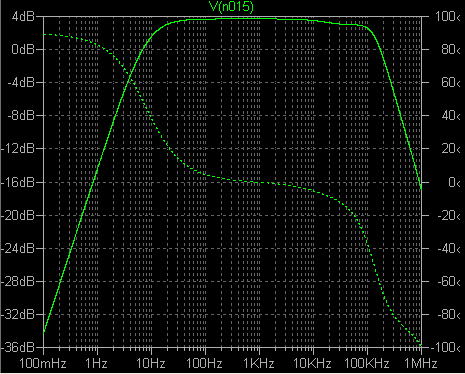

俽俹俬俠俤偱偺榗傒偼偙傫側姶偠丅-125dB偔傜偄偱偟傚偆偐丅

偐側傝偺崅惈擻偑婜懸偱偒傑偡丅

嵎摦崌惉傕摨偠夞楬峔惉偵偡傟偽傛偄偐側丠偦傟偲傕僾儕傾儞僾婎斅偺傛偆側夞楬偵偡傞偐側丠

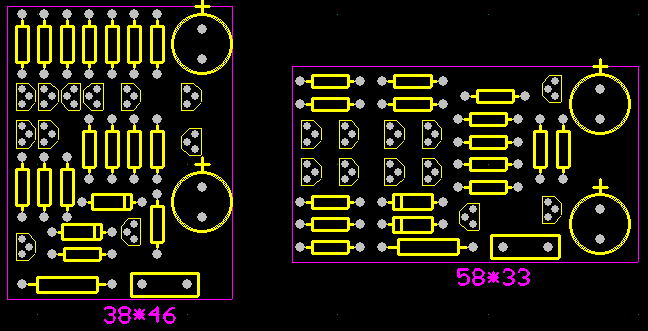

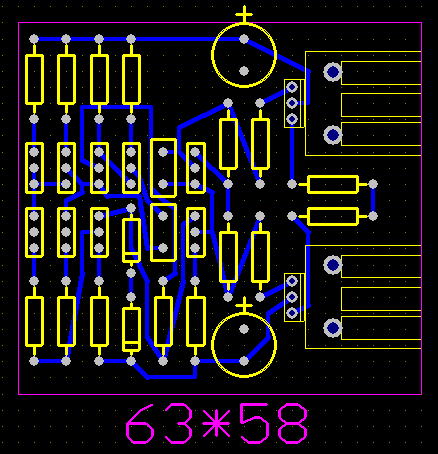

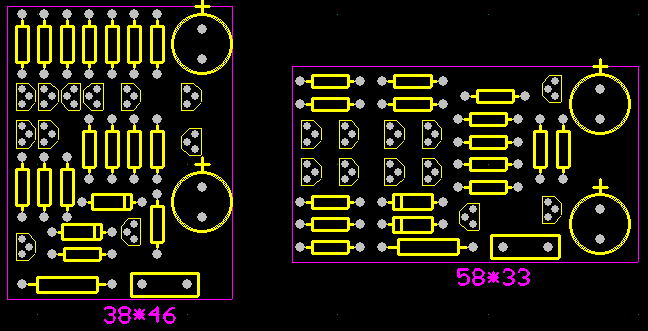

婎斅僒僀僘偼堄奜偲戝偒偄丅

IV夞楬偩偗偱偳偺偔傜偄偺柺愊偵側傝偦偆偐傪尒傞偨傔偵晹昳傪攝抲偟偰傒偨丅

廲挿偵偡傞偐墶挿偵偡傞偐偱攝抲偼堎側傞偑丄IV夞楬偑係屄偼廲偵暲傇偙偲偵側傞偺偱丄婎斅偲偟偰偼墶挿偺曽偑偄偄偩傠偆丅

偦傟偱傕丄僒僀僘偲偟偰偼58亊132mm偵側傞丅偦偟偰丄嵎摦崌惉晹偲DAC晹偑搵嵹偝傟傞偙偲偵側傞偐傜丄慡懱偺婎斅僒僀僘偲偟偰偼丄

200丂亊150mm偔傜偄傪尒崬傫偩曽偑偄偄偩傠偆偐丅偦傟偵DAI晹傕捛壛偡傟偽丒丒丒丒偐側傝戝偒偔側傞壜擻惈偁傞側丒丒丒丒

傗偭傁傝戝偒偔側傝偦偆丅2007.4.8

偲偲偊偽PCM1794偺儌僲弌椡乮俀僷儔乯偩偲嵟戝偱20mA側偺偱丄俙僋儔僗摦嶌傪偝偣傞偵偼廔抜偵偼30mA偔傜偄偺僶僀傾僗揹棳偑昁梫偱偡丅

揹尮揹埑15V偱450mW偺曻擬検偲寢峔側検丅儌僲俀僷儔乮幚幙係僷儔乯偩偲40mA棳傟傞偺偱僶僀傾僗偼50mA偼昁梫偱丄徚旓揹椡傕0.75W丅

偙傝傖曻擬斅偼妋掕偱偡丅偲偄偆偙偲偱曻擬斅傪嵹偣傞僷僞乕儞傕昤偄偰傒傑偟偨丅

偮偄偱側偺偱掞峈偺僒僀僘傕500mil偵偰偟偰丄僩儔儞僕僗僞傕TO-126僷僞乕儞偵曄峏丅傑偡傑偡戝偒偔側偭偰偟傑偄傑偡丅

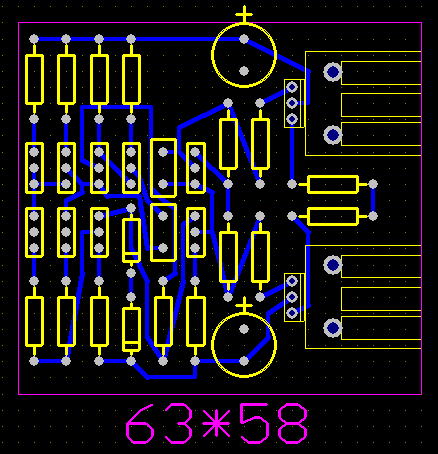

僒僀僘偲偟偰偼63亊58mm両傑偁丄戝偒偄曽偑惢嶌偡傞偲偒偼妝偱偡偗偳偹丅

晹昳僒僀僘傪彫偝偔偟偰枾搙傪忋偘傟偽傗偭傁傝彫偝偔偼側傝傑偡丅

慡懱偺夞楬傕寢峔戝偒偄側乣

偟偐偟丄忋偵昤偄偨僷僞乕儞偑傎傏俁屄暘昁梫偲側傞偲寢峔戝曄偐傕丅

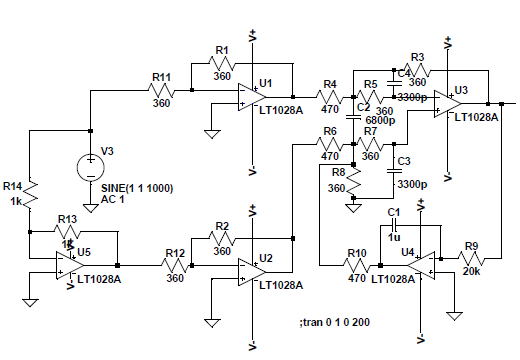

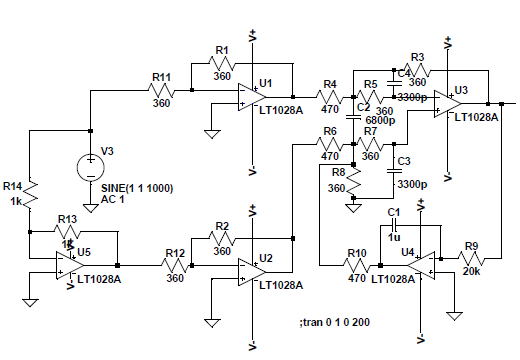

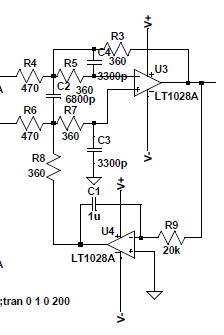

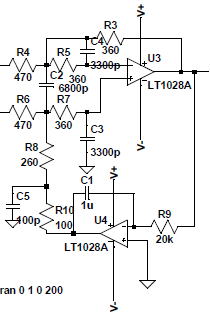

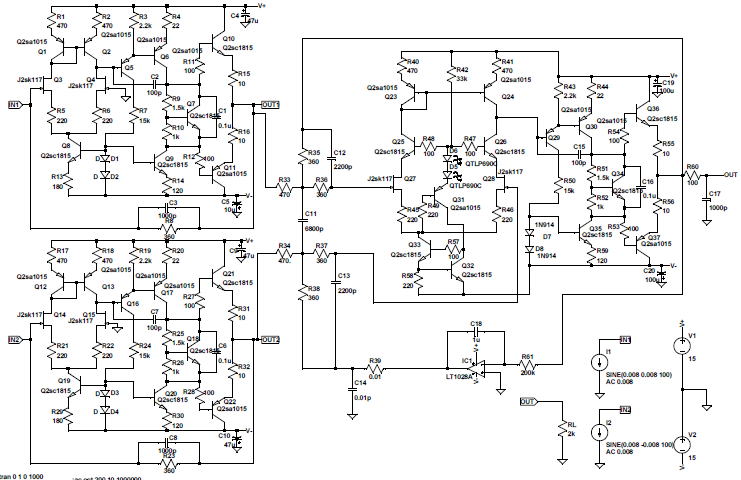

傾僫儘僌僼傿儖僞晹偺夞楬傕娷傔偰R.偝傫偐傜偄偨偩偒傑偟偨乮偪傚偭偲彂偒捈偟偰偄傑偡乯丅

僋儕僢僋偡傞偲戝偒偔偡傞偲奼戝偟傑偡丅

仈偙偺晹暘偩偗敳偒弌偟偰婎斅偵偡傟偽丄DAC1704-4D偺夵憿偵傕巊偊偦偆丅

傗偭傁傝俢俠僒乕儃偄傞偐側丠2007.4.10

夞楬婯柾偑戝偒偔側傞偺偼傛偄偲偟偰傕丄挷惍偑暋嶨偩偭偨傝偡傞偺偼偄傗側偺偱丄

弌椡偵DC僒乕儃偼昁梫偐傕偟傟傑偣傫丅忋恾偺夞楬偵DC僒乕儃夞楬傪擖傟傞偲丄

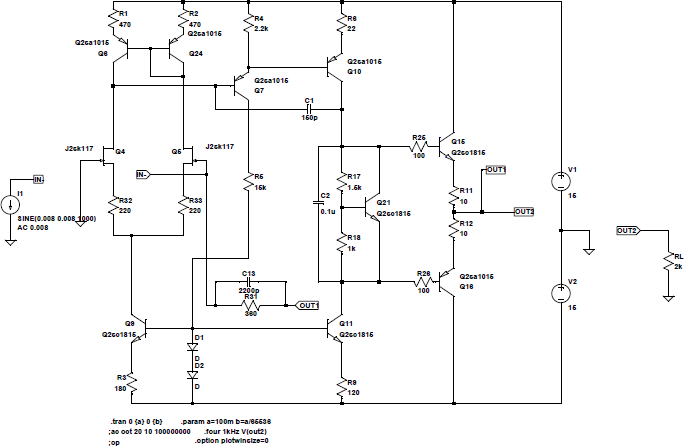

SPICE偑忋庤偔摦偐側偄偺偱丄傾儞僾晹偼俷俹傾儞僾偵抲偒姺偊偰寁嶼偝偣偰傒傑偟偨丅

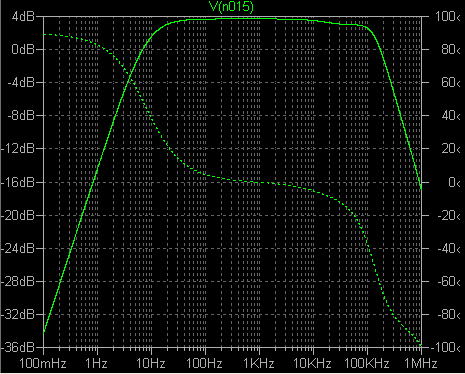

偙傫側姶偠偵側傝傑偡偑丄NOSDAC3偲傎偲傫偳摨偠偱偡丅

DC僒乕儃傪晅偗壛偊傞丅

廃攇悢摿惈偼偙傫側姶偠偱偡偑丄傕偆彮偟儘乕僇僢僩偺廃攇悢偼崅偔偰傕傛偄偐傕偟傟傑偣傫丅

f摿偱尵偊偽丄俁Hz乣300倠俫倸偔傜偄偱偟傚偆偐丠

偦傠偦傠傾僫儘僌夞楬傕幭媗傑偭偰偒偨偐側丠

傑偩傑偩廋惓偼偮偯偒偦偆偱偡丅丂2007.4.14

| 6651 |

DC僒乕儃 |

R. - 2007/04/11 22:57 - |

巹傕帡偨傛偆側峔惉偵偟傛偆偲専摙偟偰傑偟偨偑丄椻惷偵峫偊傞偲偙偺曽幃偱戝忎晇偱偟傚偆偐丠

DC僒乕儃懁偺OP傾儞僾偺弌椡偼壒惡懷堟偱偼婎杮揑偵傾乕僗偝傟偰偄傞傛偆側摦嶌偵側傞偺偱丄嵎摦崌惉偑傾儞僶儔儞僗偵側偭偨傝偟傑偣傫偐丠

僎僀儞摿惈偩偗尒偰偄傞偲惓忢偵摦嶌偡傞傛偆尒偊偨傝偟傑偡偹丅

杮幙揑側懳嶔偱偼側偄偱偡偑丄IV曄姺偵DC僒乕儃傪妡偗傞偺傕椙偄偐側偁偲巚偄傑偟偨丅

IV曄姺傾儞僾偺亄擖椡傪180僆乕儉偱傾乕僗偵愙懕偟丄弌椡偐傜DC僒乕儃妡偗丄600僆乕儉偔傜偄偱IV曄姺傾儞僾偺亄擖椡懁偵DC婣娨傪妡偗傑偡丅

IV曄姺傾儞僾偺弌椡偺僗僀儞僌偑妝偵側傝偦偆偱偡偟丄僄儈僼僅儘偺僩儔儞僕僗僞乕偺懝幐偑PNP偲NPN偱懙偄傑偡丅

娞怱偺DC僆僼僙僢僩偼嵎摦崌惉晹暘偵埶懚偟傑偡偑丄FET偺儁傾庢傝偡傟偽丄柍挷惍偱傕戝偟偨僆僼僙僢僩偑偱側偄傛偆側婥偑偟傑偡丅 |

傫丒丒丒丒俬倁夞楬偵DC僒乕儃傪偐偗傞偲俷俹傾儞僾偑俀夞楬暘憹偊偰偟傑偄傑偡偹丅幚憰偱偒傞偱偟傚偆偐丒丒丒丒

| 6652 |

re:6651 DC僒乕儃 |

TAMA - 2007/04/11 23:20 - |

偳偆傕TAMA偱偡

R.偝傫丂偼偠傔傑偟偰

懡暘丂慺恖峫偊偩偲巚偆偺偱偡偑丂巚偄偒偭偰幙栤偟偰偟傑偆偺偱偡偑丂DC僒乕儃偺OP傾儞僾偺弌椡揹埑傪丂嵎摦崌惉偺丂+擖椡懁偲GND傪宷偄偱偄傞掞峈偺GND偺戙傢傝偵愙懕偟偨傜丂嵎摦摦嶌偺僶儔儞僗傪曐偪側偑傜丂摦嶌僙儞僞乕傪僆僼僙僢僩偡傞偲偄偆摦嶌偵偱偒側偄偺偱偟傚偆偐丠 |

偦偆偱偡偹丅僔儞僾儖偵壓恾偺傛偆偵側傝傑偡偹丅

DC僒乕儃弌椡偺愙懕愭傪偡偙偟曄峏丅

偝傜偵偙傫側堄尒傕偄偨偩偒傑偟偨丅

| 6658 |

re:6651,6652 DC僒乕儃 |

hi_kawa - 2007/04/12 15:15

- |

俢俠僒乕儃偺僆儁傾儞僾偼斾妑揑僲僀僘偑懡偔弌傑偡丅偙偺僲僀僘偱俽乛俶偵塭嬁偡傞壜擻惈偑偁傝傑偡丅

偪側傒偵侾倳俥偺僐儞僨儞僒偼俀俆侽倠僆乕儉偺掞峈偲摨偠擬嶨壒偑弌傑偡丅僆儁傾儞僾偺僼傿乕僪僶僢僋偵憓擖偝傟偰偄傞偺偱丄僆儁傾儞僾偺弌椡偵偼偦偺擬嶨壒偑偦偺傑傑弌偰偒傑偡丅

偦偺堊丄僆儁傾儞僾偺弌椡偵俠俼僼傿儖僞傪憓擖偟偨傎偆偑偄偄偲巚偄傑偡丅

椺偲偟偰丄俇俇俆俀偺宍偱嵎摦崌惉偺丂+擖椡懁偲GND傪宷偄偱偄傞掞峈偺GND偺戙傢傝偵愙懕偟偨僆儁傾儞僾偺弌椡偵掞峈傪擖傟傑偡丅

偝傜偵偦偺掞峈傪僐儞僨儞僒偱俧俶俢偵棊偲偟丄僆儁傾儞僾偺弌椡偵掞峈傪憓擖偟偰俠俼僼傿儖僞傪峔惉偟偨曽偑偄偄偲巚偄傑偡丅偦偺嵺偺埨掕惈偼懡彮峫椂偟偨傎偆偑偄偄偲巚偄傑偡偑丄懡暘戝忎晇偲巚偄傑偡丅 |

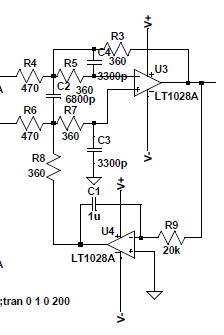

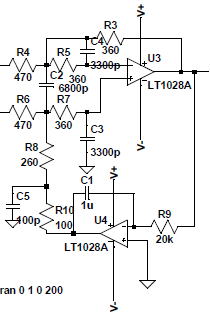

偪傚偆偳偙傫側姶偠偱偡偹丅俼俇偲俼俉偺愙懕揰偵傕僐儞僨儞僒傪擖傟偨曽偑傛偄傛偆偱偡偑丄偦偆偡傞偲嵎摦僶儔儞僗偑曵傟偰偟傑偆偺偱丄

偙傟偼旔偗傑偟傚偆丅

廃攇悢摿惈傪傒偰傒傑偟傚偆丅C5傪彮偟戝偒傔偱0.1uF偵偡傞偲偙傫側姶偠偵側傝傑偡丅

崅堟懁偱偺尭悐偑俀抜峔偊偵偁傫偭偰丄偪傚偆偳俀偮偺僴僀僷僗僼傿儖僞傪捠偟偨傛偆偵側傝傑偟偨丅

偡側傢偪C5傪捛壛偡傞偙偲偱丄怣崋偺儘乕僷僗僼傿儖僞乕偺夞楬偵塭嬁偑偱偰偄傞偙偲偵側傝傑偡偹丅

嵎摦僶儔儞僗偑曵傟傞傛偆側婥偑偡傞偺偱丄嵦梡偼偳偆偟傑偟傚偆丅

崅堟偺僲僀僘傪庢傞偩偗側傜1000pF掱搙偵偡傟偽塭嬁偼偡偔側偦偆偱偡丅

俠俆傪偮偗傞偮偗側偄偐偼幚憰帪偵慖戰偱偒傑偡偐傜僷僞乕儞偼巆偟偰偍偄偰傕偄偄偐側丠

俠俆亖0.1uF偺偲偒偺倖摿

| 6659 |

re:6651,6652 俢俠僒乕儃懕偒亄 |

hi_kawa - 2007/04/12 16:24

- |

(拞棯乯

傑偨丄俬亅倁曄姺傾儞僾偲堘偄丄嵎摦崌惉傾儞僾偼擖椡俥俤俿偺揹埵偑怳傜傟傞偺偱丄傂偢傒偺敪惗尨場偵側傞壜擻惈偑偁傝傑偡丅嵎摦崌惉傾儞僾偩偗偱傕丄弶抜偺峔惉傪僇僗僐乕僪愙懕偵偟偰壓偝偄丅

(拞棯乯 |

偳傫偳傫夞楬偑戝偒偔側偭偰偄偒偦偆乮偲偄偭偰傕僐僗僩偼傎偲傫偳曄傢傜側偄偺偱偡偑丒丒丒丒亄侾侽侽墌傾僢僾丠乯丅

偙偙偼娙扨偵HPA-2偺掕悢傪偦偺傑傑帩偭偰偔傟偽偄偄偐側丠

HP俙-2偺擖椡抜

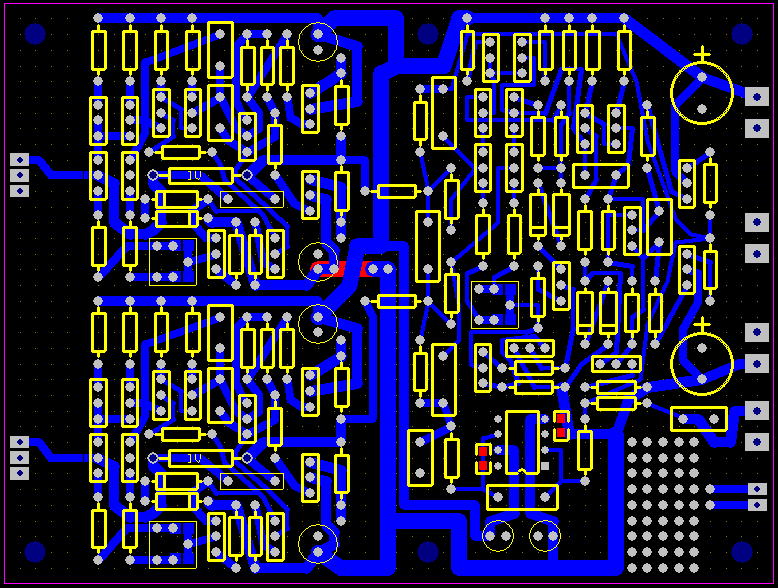

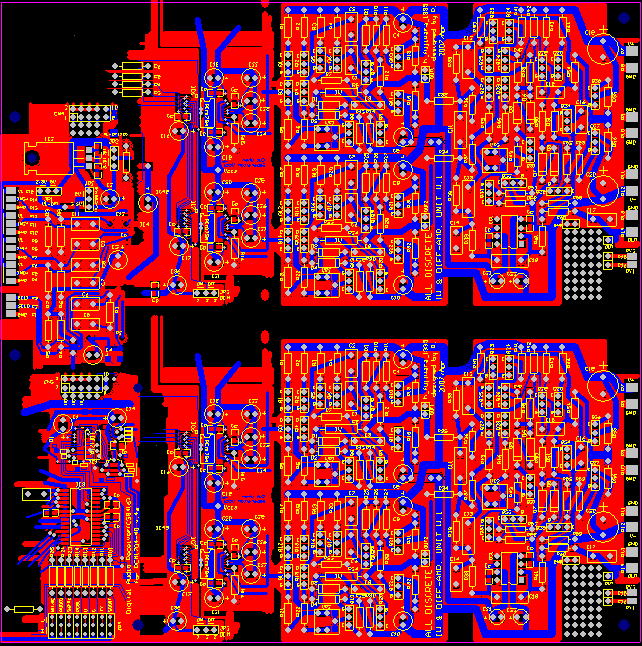

慡懱傪彂偒捈偟偰偙傫側姶偠偵側傝傑偟偨丅

乮僋儕僢僋偡傞偲PDF僼傽僀儖偑奐偒傑偡乯

SwCAD嘨梡偺僼傽僀儖

SPICE僜僼僩偺俢俴偼偙偙偐傜丅仺 http://www.linear-tech.co.jp/designtools/software/switchercad.jsp

巊偊傞偲曋棙偱偡傛丅

揹尮夞楬偼偳偆偡傞偐丠暘棧偟傑偟偨丅

傾乕僩儚乕僋奐巒両丅

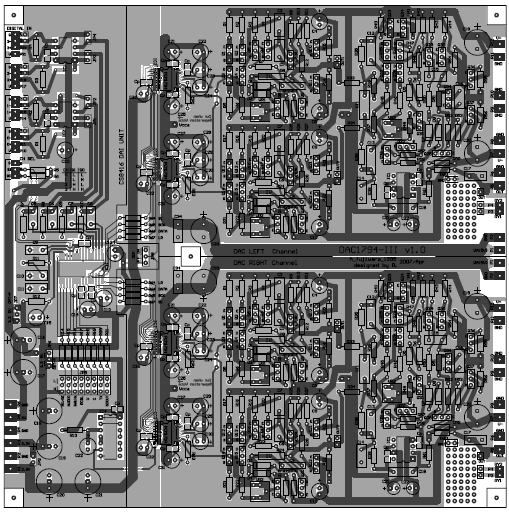

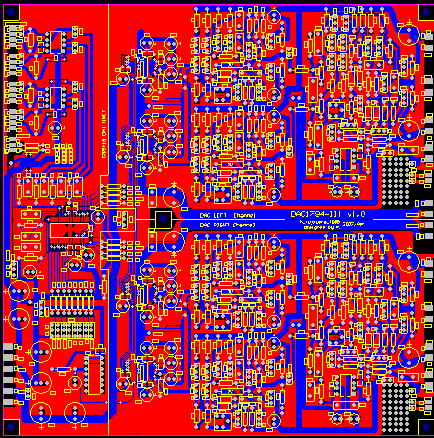

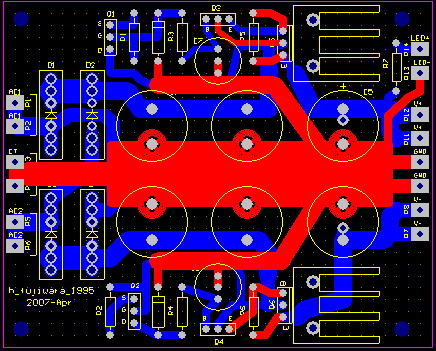

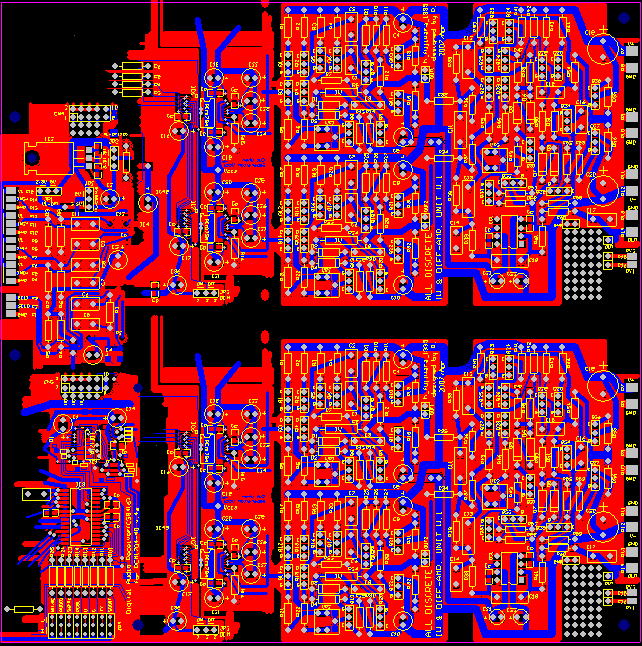

傑偢偼俀夞楬暘偺俬倁夞楬偱偡丅

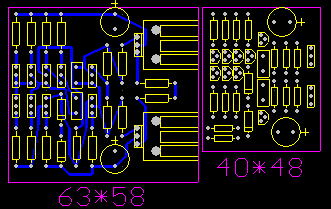

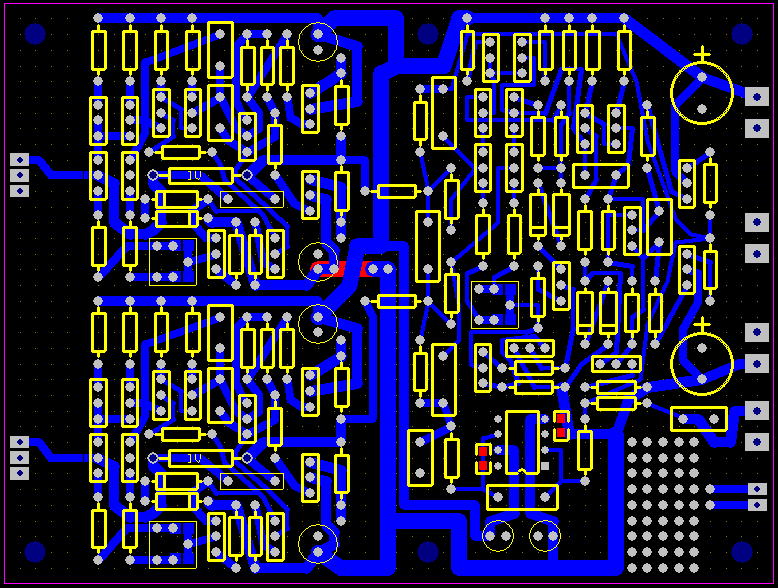

俬倁傪俀夞楬偲嵎摦憹暆亄LPF傪崌懱丅傑偢偼晹昳攝抲傪寛傔偰丄攝慄偑偱偒傞偐妋擣偟偰傒偨丅

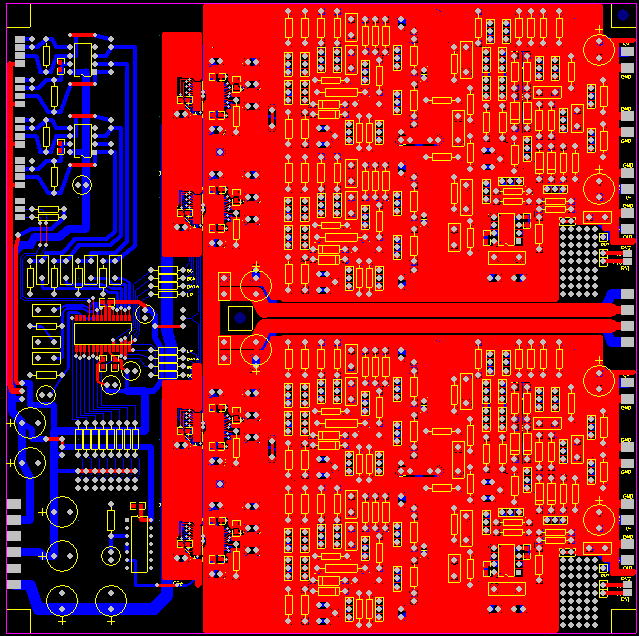

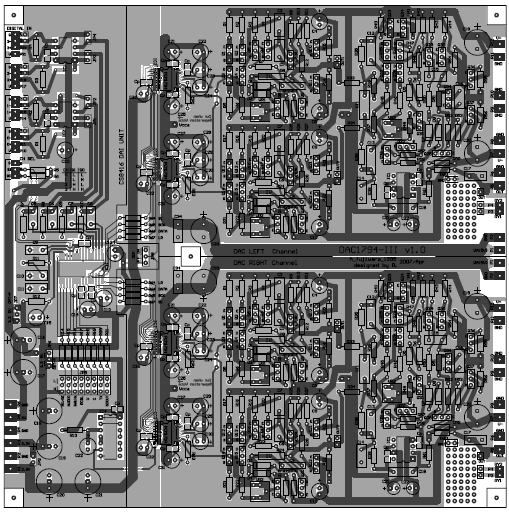

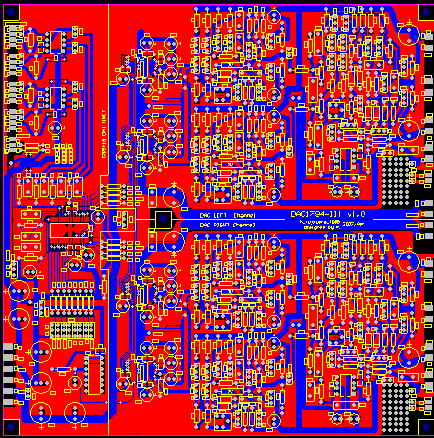

嵍懁偵柍懯側僗儁乕僗偑懡偄偗偳丄偪傚偆偳DAC1704-4D偺忋偵傾僪僆儞偱偒傞僒僀僘偵偡傞偨傔偱偡丅

偟偐偟晹昳悢懡偄側乣丅僩儔儞僕僗僞37屄偲掞峈亄僟僀僆乕僪偱栺俈侽屄偱偡偐傜偹丅

俹俠俵1794傪擖傟偨偲偒偵丄ASRC傗DAC1794D偺婎斅偲摨偠僒僀僘偵廂傑傝偒傜側偄偩傠偆側丒丒丒丒丒丒

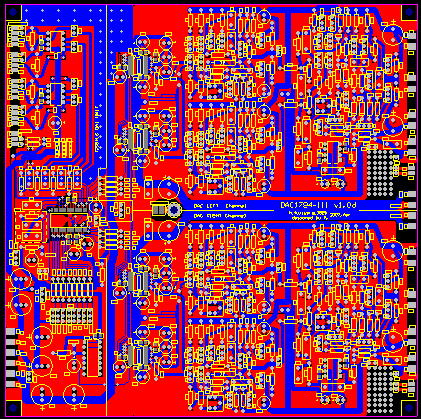

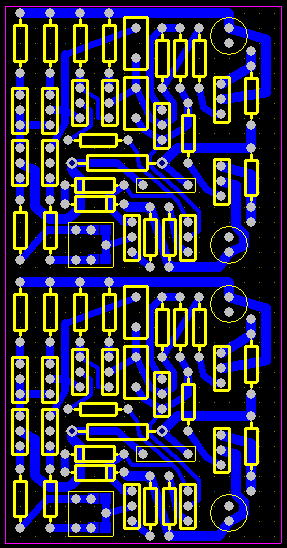

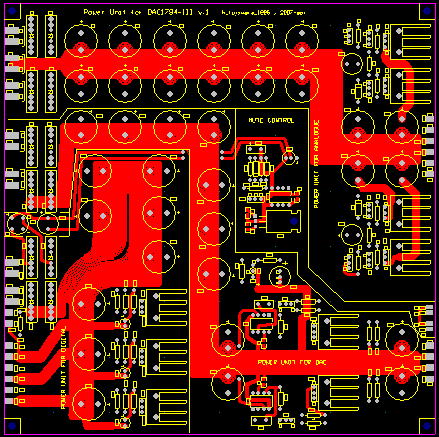

僒僀僘偼侾俀俆亊俋係倣倣丅DAC1704-4D偲晹暘揑偵庢傝晅偗僱僕僺僢僠傪崌傢偣偨丅

晹昳斣崋偲擖弌椡抂巕偺斣崋傪擖傟傞偲偩偄傇偦傟傜偟偔側偭偰偒傑偟偨丅

偙偺抜奒偱丄夞楬恾偺晹昳斣崋傪偮偗捈偟傑偟傚偆丅偦偆偟側偄偲丄攝慄偺僠僃僢僋偑偱偒傑偣傫丅

夞楬恾傕晹昳斣崋傪怳傝捈偟傑偟偨丅偝偰丄攝慄偺僠僃僢僋傪偟偰偄偒傑偟傚偆丅

杮摉偼夞楬恾偲俹俠俛僜僼僩偑堦懱側傜丄儃僞儞堦敪偱姰椆偡傞偲偙偲偱偡偑丄

側偵傇傫僀儗僊儏儔乕側巊偄曽傪偟偰偄傞柺偑偁傞偺偱丄戝曄側偲偙傠偱偡丅

晹昳斣崋傪怳傝捈偟

偝偰丄戝懱僷僞乕儞傕俷俲偦偆側偺偱嵟屻偺巇忋偘偵儀僞揾偭偰巇忋偘傑偡丅

偙傫側姶偠偱姰惉偱偡丅

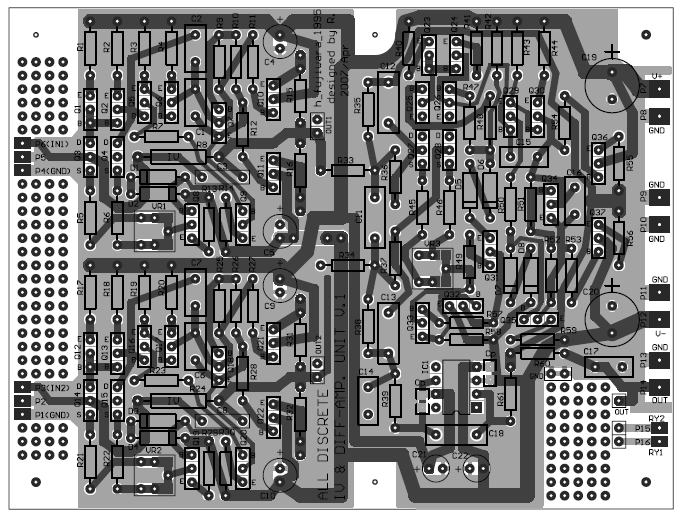

屄暿偺僷僞乕儞偺條巕偼偙偙偵偁傝傑偡丅

僷僞乕儞慡懱

敿揷柺乮亄僔儖僋乯僷僞乕儞

晹昳柺乮亄僔儖僋乯僷僞乕儞

僔儖僋僷僞乕儞

偙偺婎斅偼嵎摦弌椡偺俢俙俠傪庴偗傞偺偵揔偟偰偄傞偺偩偗偳丄偙傟扨懱偱梸偟偄恖偄傞偺偐側丠偪傚偭偲怱攝丅

DAC1704-4D偲偼愙懕偟堈偄婎斅偺戝偒偝偵偼偟偰偄傞偺偩偗偳丒丒丒丒丒

傗偭傁傝PCM1794傕搵嵹偟偨僷僞乕儞偺惢嶌偵偐偐傜偹偽両

DAC1794-3偺僷僞乕儞専摙

婎斅偺僒僀僘偼侾俋俉亊198mm偺惓曽宍傪峫偊偰傒傑偟傚偆丅偙傟偼揹尮婎斅傕摨偠戝偒偝偵偡傞偮傕傝側偺偱丄

揹尮婎斅倲偲俢俙俠婎斅偑惓曽宍偱摨堦僒僀僘偩偲丄怓乆側岦偒偱俀奒寶偰偵偱偒傞偐傜偱偡丅

栤戣偼198mm巐曽偵廂傑傞偐偳偆偐偱偡偑丄IV&LPF傪俀夞楬暘偲PCM1794丄偦偟偰俠俽8416俢俙俬偺僷僞乕儞傪揔摉偵攝抲偟偰傒傑偟偨丅

埬奜梋桾偑偁傝偦偆偱偡丅

丂偝偰192kHz傑偱偮偐偊傞俠俽8416傪偮偐偆偐丄偁傞偄偼96kHz傑偱偩偗偳崅惈擻DIR9001傪偮偐偆偐偼擸傑偟偄慖戰偱偡丅

198mm巐曽偺婎斅偵壖攝抲丅

PCM1794偺傾僫儘僌懁偺攝慄傑偱偼姰椆丅俢俙俬偼俠俽8416傪憐掕偟偰攝慄傪専摙拞丅

崱擔偺嶌嬈偼偙偙傑偱偐側乮2007.4.22乯丅

仈俫俹偺梕検偑偩傫偩傫怱嵶偔側偭偰偒傑偟偨丒丒丒丒丒

晹昳偺攝抲偼偙傫側偲偙傠偱偟傚偆丅2007.4.28

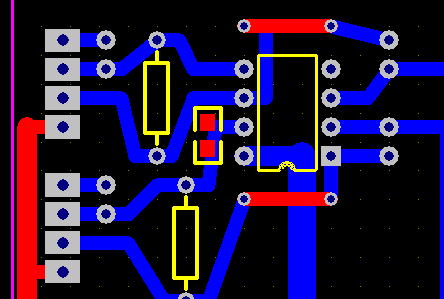

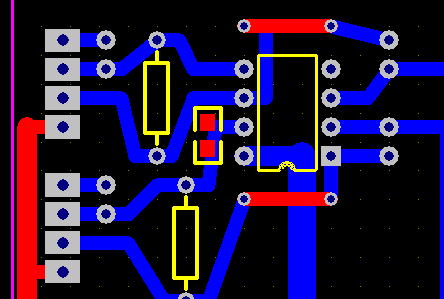

俢俙I夞傝偺晹昳傪攝抲偟偰僷僞乕儞傪昤偄偰傒傑偟傚偆丅儀僞偼嵟屻偺巇忋偘偱偡偑丄

DAI廃曈偼斾妑揑僗儁乕僗偵梋桾偑偁傝攝慄偑埬奜妝偱偟偨丅

俽俶俈俆侾俆俈傕幚憰偱偒傞傛偆偵偟偰傒傑偟偨丅

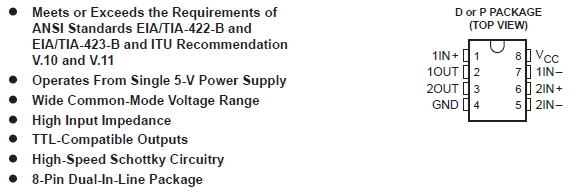

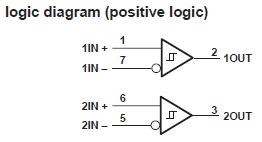

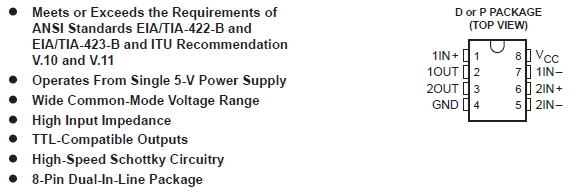

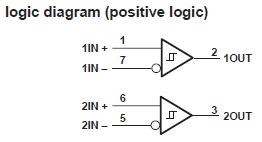

僨傿僕僞儖擖椡偵偮偄偰偼RS422儗僔乕僶偱偁傞SN75157傕偮偐偊傞傛偆偵偟偰傒傑偟偨丅

偱傕丄偁傑傝尒偐偗側偄俬俠側偺偱丄僗儖乕偱偒傞傛偆偵僷僞乕儞偼岺晇偟偰偄傑偡丅

偲偄偭偰傕丄僔儖僋傪昤偐側偄偲壗偑側傫偩偐傢偐傜側偄偱偡偹丅

SN57157傕偮偐偊傞傛偆偵偟偨僷僞乕儞丅

SN75157偺摿挜傪僨乕僞僔乕僩偐傜揮婰偟偰傒傑偟偨丅

5V扨堦偱俀夞楬擖傝偲偄偆偺偑巊偄傗偡偦偆偱偡丅

DIGI-KEY偱仐227墌偱偡偹丅崅偄偺偐埨偄偺偐丒丒丒丒

74HCU04偑@30墌偔傜偄偩偲偄偆偙偲傪峫偊傞偲丒丒丒丒暋嶨丅

偲傝偁偊偢姰惉宍両

傑偩僷僞乕儞僠僃僢僋傗丄慄偺堷偒夞偟偺廋惓側偳偑巆偭偰偄傞偗偳丄偙傫側姶偠偵側傝偦偆偱偡丅

戝偒偔曄傢傞偙偲偼側偄偱偟傚偆丅

乮僋儕僢僋偡傞偲戝偒偔側傝傑偡乯丅

偟偽傜偔偟偰偙傫側僐儊儞僩傪偄偨偩偒傑偟偨丅側傞傎偳丄俢俙俬偺傾僫儘僌晹偼廳梫偱偡偹丅僷僞乕儞傪廋惓偟傑偟傚偆丅

偲偄偭偰傕偡偱偵庤傪擖傟傞偲偙傠偑擄偟偄偲偙傠傕偁傞偺偱丄偡傋偰偵懳墳偱偒傞傢偗偱偼側偄揰偑偮傜偄偲偙傠偱偡丅

| 6811 |

DAC1794-3偺僷僞乕儞俀 |

R. - 2007/04/29 01:50 - |

CS8416偺儖乕僾僼傿儖僞乕偺慺巕C10丄C11偺岦偒傪180亱曄偊偰傾乕僗懁偑CS8416偺AG偲嬤偔側傞傛偆偵攝抲偟

AG丄C10丄C11偺傾乕僗僷僞乕儞偵僨僕僞儖僲僀僘偑夞傝偙傑側偄傛偆偵愗傝崬傒傪擖傟偰

傾乕僗僷僞乕儞傪暘棧偟偰偼偳偆偱偟傚偆偐丠

僨僕僞儖傾乕僗偲偺愙懕偼CS8416捈壓偺7僺儞丄22僺儞偺娫偱愙懕偡傞偲傛偄偺偱偼側偄偐偲巚偄傑偡丅 |

| 6810 |

DAC1794-3偺僷僞乕儞 |

R. - 2007/04/29 01:24 - |

CS8416偺僨乕僞僔乕僩偵傕彂偄偰偁傞傛偆偵VA偵嫙媼偝傟傞揹尮揹埑偺儘乕僲僀僘壔偑

僕僢僞乕掅尭偺廳梫側億僀儞僩偵側傝偦偆偱偡丅

堦岺晇偲偄偆偙偲偱丄C12偺揹尮擖椡偺庤慜偵僼僃儔僀僩價乕僘偲偐傪憓擖偱偒傞傛偆偵僷僞乕儞傪

捛壛偡傞偺偼偳偆偱偟傚偆偐丠

僨僕僞儖揹尮懁偺僲僀僘偺夞傝崬傒偑掅尭偝傟傞偲巚偄傑偡丅

戝偟偨揹棳傪徚旓偡傞傢偗偱傕側偄偲巚偆偺偱丄100僆乕儉偔傜偄偺掞峈傪擖傟偰傕椙偄偐傕偟傟傑偣傫丅

C12偵偼10mm宎偺擔杮働儈僐儞PSA偲偐巊梡偱偒傞偲偐側傝僲僀僘掅尭偵岠壥偑偁傞偐傕丠

LM317偺揹尮婎斅偐傜CS8416偺僨僕僞儖偲傾僫儘僌揹尮偵暿乆偺攝慄偱媼揹偡傞偲偄偆椡媄傕偁傝傑偡偹丅

|

|

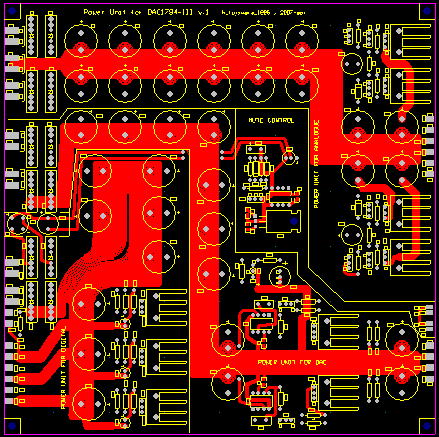

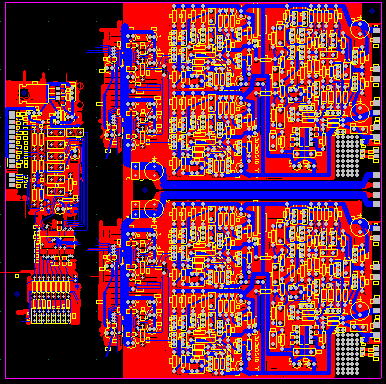

揹尮婎斅傕姰惉偟傛偆傗偔慡懱憸偑傒偊偰偒傑偟偨両

傑偩偙傑偐偄僠僃僢僋偼廫暘偱偼側偄偱偡偑丄慡懱僷僞乕儞偑偱偒偰偒傑偟偨丅

| 丂丂DAC1794-III丂杮懱 |

丂丂DAC1794-III丂揹尮晹 |

|

|

慡懱

晹昳柺

敿揷柺

僔儖僋 |

1794-P4-all乮慡懱乯丂係乛俁侽峏怴 |

| 峏怴婰榐丂2007.4.29丂1794-3B |

峏怴婰榐丂2007.4.29丂1794-p4

峏怴婰榐丂2007.4.29丂1794-p4

婎斅偑戝偒偄偺偱丄曐帩偺偨傔偺僱僕寠傪DAC婎斅偲摨偠埵抲偵捛壛 |

峏怴婰榐丂2007.4.30丂1794-3C

丒僔儍乕僔傾乕僗梡偺儔儞僪捛壛

丒摨幉擖椡偺僈乕僪傾乕僗捛壛

丒PCM1794偺GND愙懕曄峏

丒PLL僼傿儖僞乕偺傾乕僗僗儕僢僩暆曄峏

慡懱乮係乛俁侽峏怴乯

敿揷柺乮係乛俁侽峏怴乯 |

|

偼傗偗傟偽楢媥柧偗偵帋嶌偵弌偣傞偱偟傚偆丅

偟偐偟丄晹昳揰悢懡偄側乣丅DAC8D乮PCM61P斉)偲摨偠僒僀僘偺婎斅偩偗偳丄偙偪傜偺曽偑偐側傝暋嶨両

傎傫偲偆偵摦偔偺偐怱攝偵側偭偰偒傑偟偨乮徫乯丅

偮偄偱丠

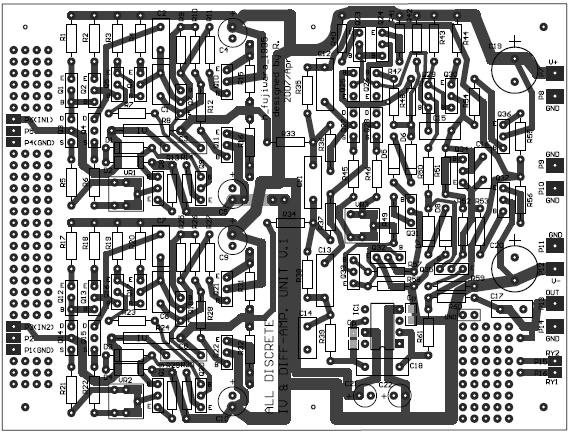

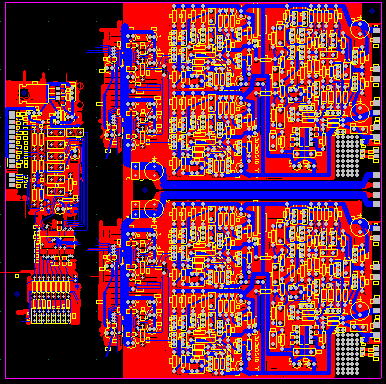

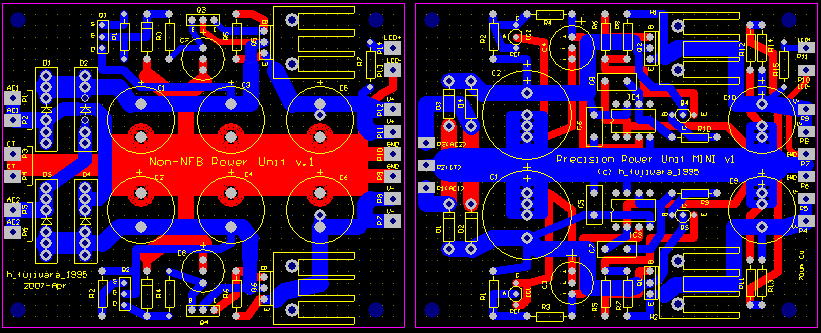

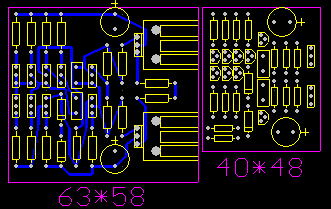

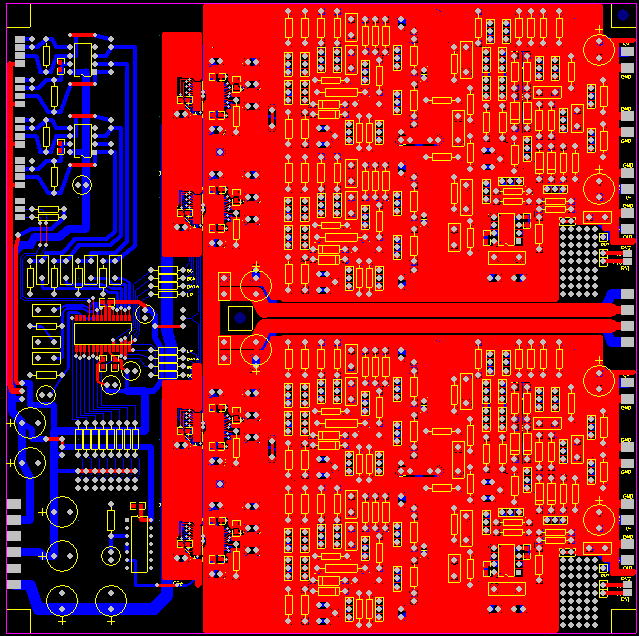

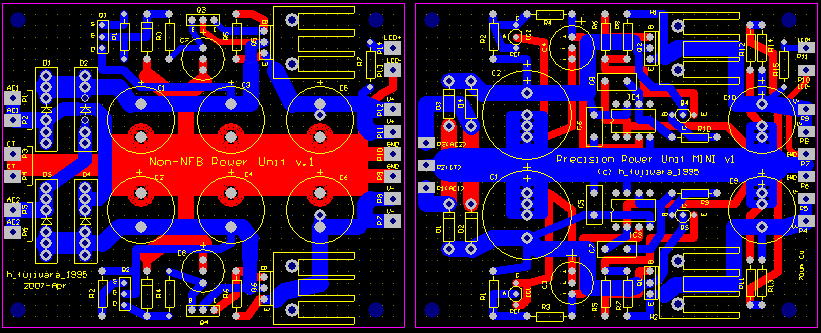

Non-NFB僞僀僾偺揹尮晹傪敳偒弌偟偰揹尮婎斅偺傾乕僩儚乕僋傪昤偄偰傒傑偟偨乮嵍懁乯丅

塃懁偼僨傿僗僋儕mini揹尮婎斅偱OP傾儞僾傪偮偐偭偨NFB桳傝偺傕偺偱偡丅

偳偪傜傕摨偠僒僀僘丄摨偠僱僕僺僢僠偱偡偺偱抲偒姺偊偑壜擻偱偡丅

揹埑偺埨掕惈偐傜偄偊偽丄埑搢揑偵僨傿僗僋儕mini揹尮婎斅偺傎偆偑傛偄偺偱偡偑丄

Non-NFB僞僀僾傕掅僲僀僘偵摿挜偑偁傝丄偦傟偧傟僉儍儔偑傑偭偨偔偪偑偄傑偡丅

偳偪傜偑傛偄偲偐偱偼側偔丄揔嵽揔強偑廳梫偱偡偹丅

晹昳揰悢偺偡偔側偝偱偄偊偽NON-NFB僞僀僾偵孯攝偑偁偑傝傑偡丅

NO俶-NFB僞僀僾偺揹尮婎斅丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂NFB桳傝偺僨傿僗僋儕mini揹尮婎斅

| 6827 |

re:偮偄偱丠 |

R. - 2007/04/30 20:34 - |

僸儘偝傫

NO俶-NFB僞僀僾偺揹尮婎斅偺僷僞乕儞偱偡偑丄C3丄C4傛傝弌椡懁偺晹暘偐傜婎弨揹埑傪

嶌惉偡傞D傪愙懕偟偨曽偑椙偄偱偡丅

C3丄C4偲惍棳D娫偵偼僠儍乕僕揹棳偵傛傞戝偒傔偺儕僢僾儖偑忔傝傑偡偺偱丄

偦傟傛傝弌椡懁偺傾乕僗晹暘偱婎弨揹埑傪庢傝弌偝側偄偲僩儔僽儖偺尨場偵側傝傗偡偄偱偡丅

DAC1794-3偺僷僞乕儞偼僶僢僠儕偱偡偹丅偁偲彮偟偩偗梫朷偱偡丅

CS8416偺傾僫儘僌晹偺僗儕僢僩偱偡偑丄

傕偆彮偟暆峀偔庢偭偰傕傜偆偲丄僗僩儗乕偵傛傞寢崌偑彫偝偔偱偒偦偆偱偡丅

偦傟偲丄DAC晹暘偱偡偑丄DG偲AG偺僗儕僢僩偺愙懕晹暘偼奺PCM1794偺DG偲AG娫偺

奺4売強偱偲傞偺偼偳偆偱偟傚偆偐丠

僗儕僢僩娫妘傕傕偆彮偟偁偗傜傟傞偲椙偄偐偲巚偄傑偡丅

杮扞傪嫏偭偰偄偨傜丄僩儔儞僕僗僞媄弍偺2005擭6寧崋偵傾僉儏僼僃乕僘偺媄弍幰偺曽偑

PCM1796傪椺偵僷僞乕儞愝寁偺億僀儞僩傪夝愢偝傟偰偄傞偺傪尒偮偗傑偟偨丅嶲峫偵側傞偲巚偄傑偡丅

偍帩偪偱偡偐丠

|

|

偲偄偆偛巜揈偺尦丄偠傖偭偐傫廋惓偟傑偟偨丅

側傫偲側偔晹昳柺僷僞乕儞乮愒乯偑僞僐偺傛偆偵尒偊傞偺偼婥偺偣偄丠乮

DAC婎斅偵偮偄偰傕廋惓偟傑偟偨丅廋惓僷僞乕儞偼偪傚偭偲忋偵偁傝傑偡偑丄偙偙偵傕僐僺儁丅

偄傠偄傠傒偰偄偨傜丄僐儞僨儞僒偺嬌惈乮亄乯僔儖僋娫堘偄側偳偑偄傠偄傠偁傝傑偟偨丅

嵟廔斉両2007.5.2

偄傠偄傠偲儕僋僄僗僩偑偁傝傑偟偨丅

| 6849 |

re:6848 re:6847 |

ma - 2007/05/02 19:37 - |

OMCK System Clock Mode 傪巊偆応崌偲丄巊傢側偄応崌偺

愗傝懼偊梡偵CS8416偺儕僙僢僩偑娙扨偵偱偒傞傛偆偵

儕僙僢僩梡偺僕儍儞僷乕億僗僩傕偁傞偲彆偐傝傑偡丅

|

| 6848 |

re:6847 |

ma - 2007/05/02 18:33 - |

偦偙偱丄OMCK偑CS8416偺壓偱DGND偵愙懕偝傟偰偄傞偺傪

SDOUT側偳偺 pull-up

pull-down慖戰偺傛偆側姶偠偱丄

僷僞乕儞僇僢僩仌奜晹偐傜偺怣崋擖椡偑偟傗偡偄傛偆側

僷僞乕儞傪捛壛偟偰偄偨偩偗傑偣傫偱偟傚偆偐丅

2pin偺僐僱僋僞偑庢傝晅偗偱偒傞傛偆偵側偭偰偄傞偲

偁傝偑偨偄偱偡丅

偦傟偲丄OLRCK 偲 DGND 傕

2pin僐僱僋僞偱丄

庢傝偩偣傞傛偆側僷僞乕儞傪 C12 偺椬偵偱傕

梡堄偟偰捀偗傞偲偨偡偐傝傑偡丅

偙偺俀偮偑偁傟偽丄奜晅偗偱僋儘僢僋儌僕儏乕儖傪

梡堄偟偰OMCK偵擖傟偰丄OLRCK傪 Word Clock偲偟偰

棙梡偡傟偽丄巹偑峫偊偰偄偨偙偲偑幚尰偱偒偦偆偱偡偺偱丅

傛傠偟偔偍婅偄偟傑偡丅

|

|

忋偺僐儊儞僩偩偗傒傞偲傛偔傢偐傜側偄偲巚偄傑偡偑丄CS8416傪奜晹僋儘僢僋偱摦偐偟偰WORD丂CLOCK傪奜偵庢傝弌偦偆偲偄偆傕偺偱偡丅奜晹僋儘僢僋偺岠壥偼傛偔傢偐傜側偄偲偙傠偑偁傝傑偡偑丄偙傟偵偮偄偰偼ma偝傫偵儗億乕僩傪偍婅偄偟傑偟傚偆丅

僷僞乕儞偺曄峏偼寢峔柺搢偱偟偨偑丄偙傫側姶偠偵側傝傑偟偨丅

偙傟偑嫲傜偔嵟廔斉偱偡丅壗夞尒捈偟偰傕娫堘偆偲偙傠偼娫堘偆偟丄摜傫愗傝偑戝愗偱偡丅

偙傟偑偍偦傜偔嵟廔斉両

屻曇傊偮偯偔両

乮偮偯偔乯

丂

丂