�d����H�͂ǂ����邩�H

�d���͂ǂ̉�H�ł�������ǁA�Ƃ��ɂc�`�b�̏ꍇ�̓f�B�W�^����H�p�ɂ͍����x�Ȃ��̂����������B

�Ƃ����̂́A�d�����ϓ������ON/OFF�̂������l���U���̂ŁA�W�b�^��������\�������邱�Ƃ��\�z�����B

| 6657 | �VDAC�d�� | ���� - 2007/04/12 14:50 - |

| ����̂������P�V�X�SDAC�̂��߂̃��M�����[�^�[��V�J�����Ă͂ǂ��ł��傤���B

���S�f�B�X�N���[�g��dac x 2 analog x 2 digital x 1���炢�̂��ꖇ��Ղł���悢�Ǝv���̂ł����B�������O��Ɋ��S�f�B�X�N���[�g�͂���Ă���̂ł����ƊȈՂȃo�[�W�����ŁB����͂��肷�����Ƃ������܂� |

||

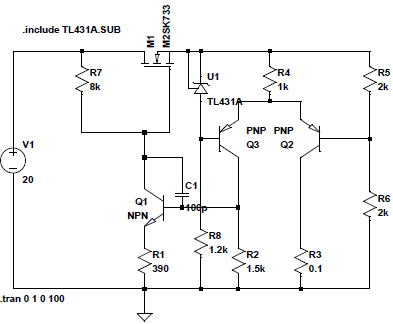

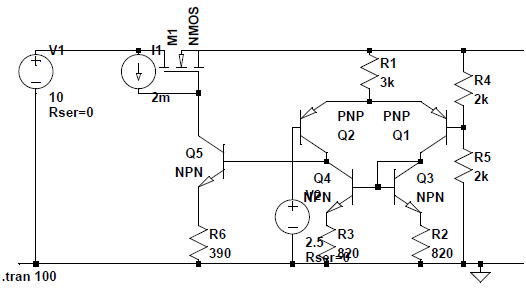

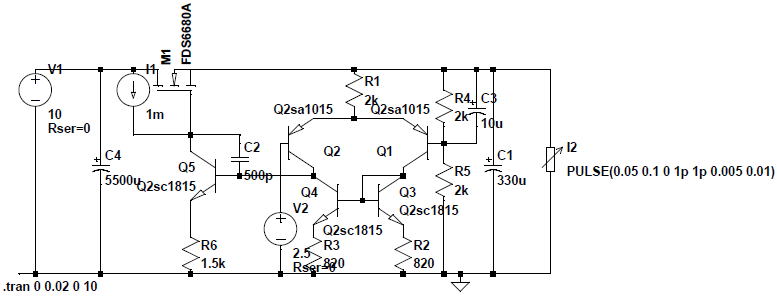

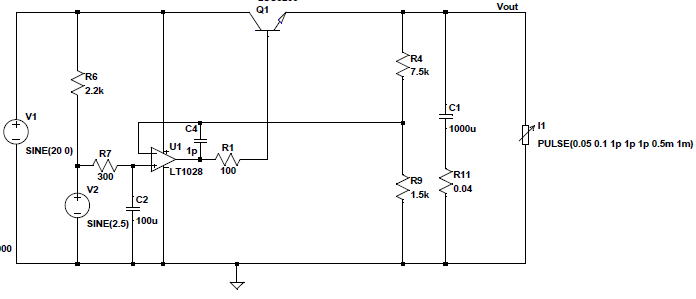

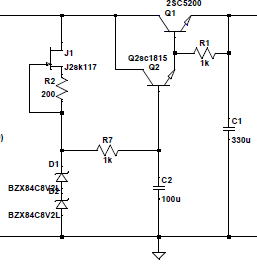

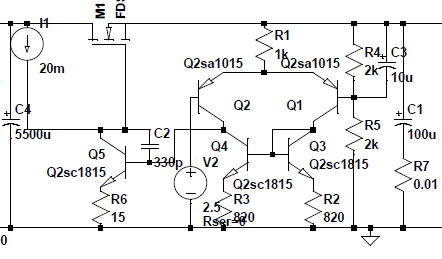

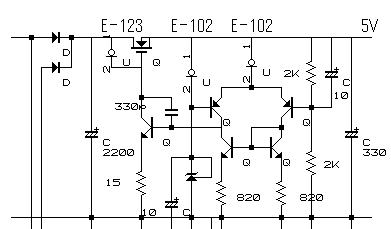

��L�̏������݂ɍ��킹�ĉ�H�}�������������B

|

���тł��B

����ȉ�H�͂ǂ��ł��傤���B����ł��R�[�q���M�����[�^���炢�̐��\�͂���Ǝv���܂��B

mos�̋߂��̃_�C�I�[�h�͒�d���_�C�I�[�h�̊ԈႢ�ł�

|

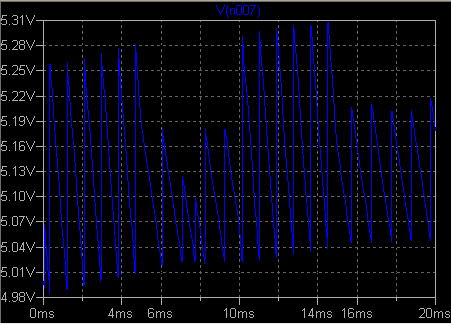

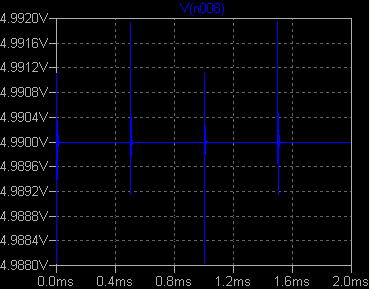

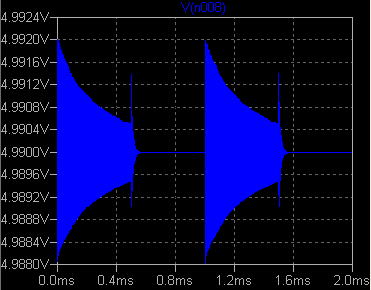

| ���тł��Bspice�f�[�^����܂��B ��͂���Ƃ킩��Ǝv���܂����A1Khz���̔��U������܂��B ���܂��}���邱�Ƃ��ł��Ȃ��̂ŊF�l�̒m�b���肽���Ǝv���܂��B �ȂɂƂ���낵�����肢���܂��B |

�Ƃ��������Ŕ��U���Ă��܂��B�b�Q�e�ʂ������Ď��g�����ς�����悤�ł����A���ɐU�����傫���Ȃ����悤�ł��B

������������Ԃ��Ȃ��A�q�D����Ώ��Ă����[���ő����Ă��܂����B

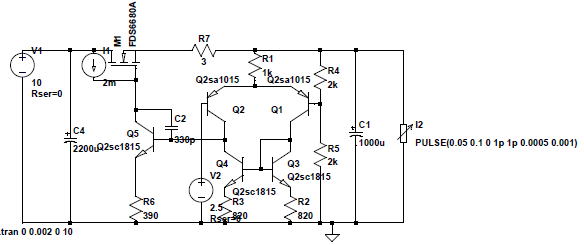

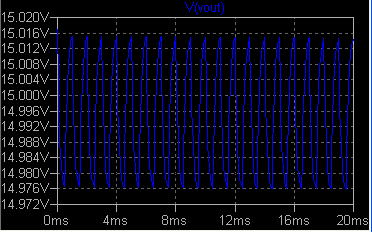

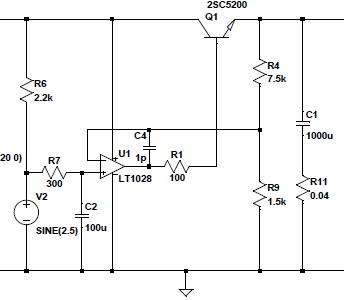

| ���艻�d���̐v�̃Z�I���[����s���� ����FET�̏o��R�Əo��C��RC��H�ŁA�������g���ł̃Q�C���� ���Ƃ��Ă��K�v������܂��B ���̂��߁AR7��lj����AC1��1000uF���x�܂ő傫������K�v������܂��B C1��ESR��0.04�I�[���Ƃ��ė���`�����Ă��܂����A�I�[�f�B�I�p�d���R���� �g�p����Ƃ�������ESR���傫���Ȃ�̂ŁA���萫��]�����Ă����K�v������܂��B R7��d�����o�p�Ƃ��ė��p���ĕی��H���`������̂��ǂ����Ǝv���܂��B �o��MOS��Gm�ɂ���Ē萔������K�v������AC1�̗e�ʂ�ESR�ɂ���� ���萫���ቺ���₷���̂ŁA�㋉�҂łȂ��ƒ���������Ǝv���܂��B |

�ŁA�����ς�������Ƃ����Ɖ��̉�H�ɂ���悤�ɂq�V���lj�����Ă��܂��B

�q�D����ɂ��C����

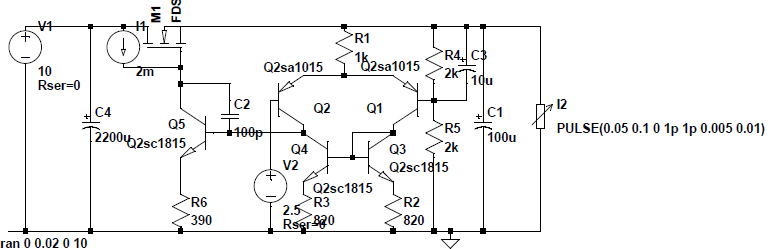

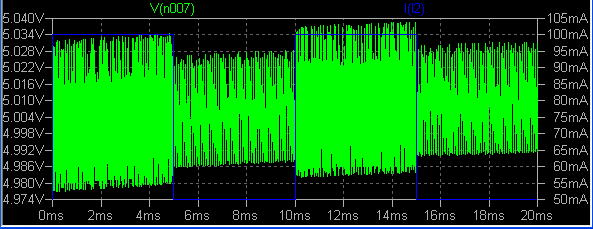

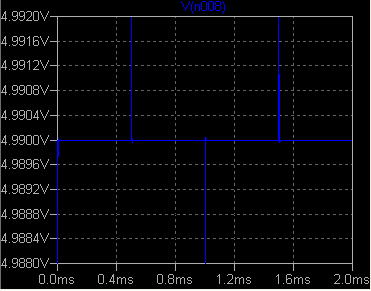

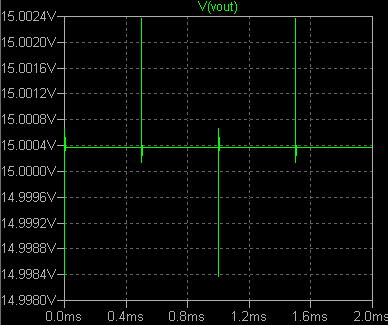

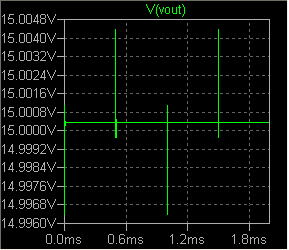

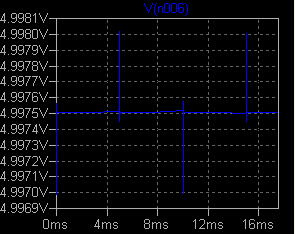

�V�~�����[�V�����̌��ʂ͂��̒ʂ�A2mV�̂Ђ�������܂����A���肵���o�͂ɂȂ��Ă��܂��B

�@�@�@�@�@�@�@�@�@�@R7=3��

����������ɂR���̒�R���͂���̂͂�����ƒ�R������܂��i�ʟ����H�j

�ŁA���̒�R�l�������������Ă݂܂��傤�B

�@�@�@�@�@�@�@�@�@R7=0.5���@�@�@�@�@�@�@�@�@�@�@�@�@�@�@�@�@�@�@�@�@�@�@�@�@�@�@�@�@�@�@�@�@�@�@�@�@�@R7=0.1��

�q�V���������Ȃ�ƂЂ��̐U���͂����܂����A�_���s���O�������Ȃ�悤�ł��B�����锭�U��Ԃɋ߂Â��Ă���

�Ƃ������Ƃł��ˁB

����́A�q�D�������Ă���悤�ɁA���̉�H�퐔�Ƃ̂��˂����ŊȒP�ɕω�����̂Œ萔�����͌��\�ނ������������B

�f�B�X�N���d���̊ȗ��ł�����ȁH

�������O��R.�����Ă̂������AMINI�f�B�X�N���d���̊ȗ��ŁBTR,��R�̐������Ȃ��Ȃ��Ă��܂��B

�V�~�����[�V�����̌��ʂ͂���Ȋ����B2mV���炢�̂Ђ��͂���܂����A���ϓd���͈��肵�Ă��܂��B

|

||||||

�Ƃ������Ƃł��B������ŁA��x���ꂼ����r���Ă݂܂��傤�B

�R�Ҕ�r�I

| No-NFB ���b�v���t�B���^�[ (R.����j |

���b�v���t�B���^with��d��ZiD�Ƃ����\���B�V���v���ł��B |

���ׂɑ��郌�M�����[�V�����͂��܂�悭����܂���B ���b�v������40mVpp���炢����܂��B |

| OPA-FB (R.����j |

��H�̓V���v���ł��B |

���ׂɑ��郌�M�����[�V�����͗ǍD�ł��B |

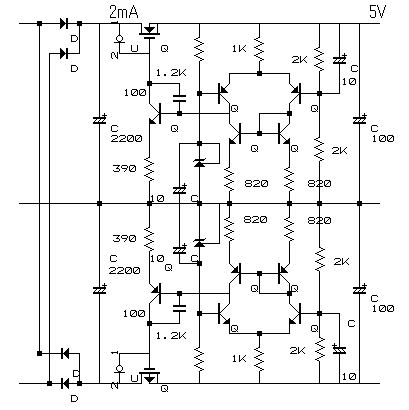

| TR-FB �i����j |

�f�B�X�N���[�g�\���Ȃ̂ʼn�H�͂�╡�G�ł��B |

���ׂɑ��郌�M�����[�V�����͗ǍD�ł��B |

���i���𐔂��Ă݂܂��傤�B

�����R���f���T�������������H�݂̂̔�r�ł��B

| No-NFB ���b�v���t�B���^�[ (R.����j |

�g�����W�X�^�@�R ��R�@�R �_�C�I�[�h�@�Q �R���f���T�P |

�������i���@�X�� |

| OPA-FB (R.����j |

�g�����W�X�^�@�P �n�o�A���v�@�@�P ��R�@�T �_�C�I�[�h�@�P �R���f���T�Q |

�������i���@�P�P�� �iOP�A���v�͂Q���Z�j |

| TR-FB �i����j |

�g�����W�X�^�@�U ��R�@�T �_�C�I�[�h�@4 �R���f���T3 |

�����i���@�P�W�� |

�Ƃ��������ł��ˁB�f�B�X�N���[�g�ɂ���ƁA��͂蕔�i�_���������܂��B

�ǂꂪ�����Ƃ������Ƃ��ł͂Ȃ��A��������Ĕ�r���Ă����Ɠ��̒��������ł��܂��B

No-NFB�̓��b�v���͑����̂ł����A���́I

���ꂪ��ԁA�m�C�Y�����Ȃ��悤�ł��B

�q�D����uPLL��H�̐v�Ɖ��p�v�ɍڂ��Ă���d������̃m�C�Y�f�[�^�������Ă��炢�܂������A����Ȓl�炵���ł��B

�d������̃m�C�Y(f=1kHz�ł̑��Δ�r�j

| �m�i�l�V�W�P�T�` �i�R�[�q���M�����[�^�j |

�O���a |

| �m�i�l�V9�P�T�` �i�R�[�q���M�����[�^�j |

+7dB |

| �m�i�l�R�P�V �iADJ�[�q�ɂb�����j |

+5dB |

| �m�i�l�R�P�V �iADJ�[�q�ɂb�L��@47uF�j |

-15dB |

| ���b�v���t�B���^�[ (No-NFB) |

-48dB |

���b�v���t�B���^�[����ׂ��ł��BFB���������������A���v�ł́A�d���ϓ��͂��܂�W�Ȃ��̂�

���b�v���t�B���^�[��H���悳�����ł��B����f�B�W�^����H�͓d���ϓ�������ƃW�b�^��������̂�

FB�������������x�d�����K�v�Ȃ�ł��傤�B����ɁA���b�v���t�B���^�[�ł͓d���̒��������ɂ����ł����ˁB

���ꂾ������ƁA�A�i���O���͒P�����b�v���t�B���^�[(No-NFB)���g�������Ȃ��Ă��܂������ł��B

�d���̕��j����I2007.4.28

��L�̌������ʂ���ADAC1794-�V�̓d�����̍\���͉��L�̂悤�ɂ��邱�Ƃɂ��邱�Ƃɂ��܂����B

| DAC1794-�V�̓d���\�� | |||

| �ꏊ | �\�� | �K�v��H�� | ���l |

| �f�B�W�^���� �i�c�`�h�APCM1794�̃f�B�W�^�����j |

LM317����������d����H �iADJ�ւ̃R���f�������Ē�m�C�Y���j |

�{�T�u�~�P �{�R�D�R�u�~�Q |

�d�����x�D�� �i��H�̓V���v���Ɂj |

| DAC���A�i���O �iPCM1794�̃A�i���O�d���j |

OPA��������FB��H �imini�f�B�X�N���Ɠ����j |

�{�T�u�~�Q | �d�����x�D�� |

| �A�i���O�� �i�h�u���k�o�e�j |

���A�ғd�� | �����P�T�u �~�Q�n�� |

��m�C�Y�D�� |

����ł����āA�Ƃ肠�������i���̂邩�ǂ��������Ă݂܂��傤�B

�R���f���T�̋ɐ��Ƃ��܂��܂��ԈႢ������܂����A�Ȃ�Ƃ��K�v�ȉ�H���͊�̏�Ɏ����ł������ł��B

����͓d�����MUTE��H�����ڂ��܂����B

�Ƃ肠�������i���ڂ邩���s�I���v�̂悤�ł��B�����قƂ�NJ����H

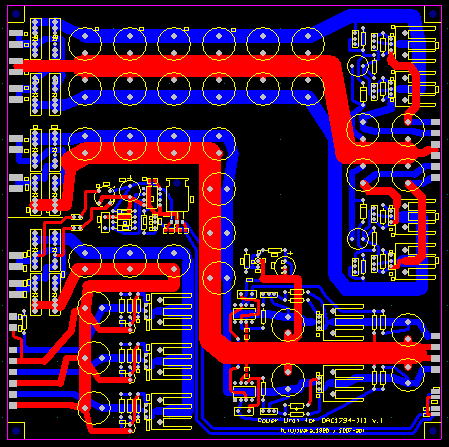

�m�F���₷���悤��PDF�t�@�C���ɗ��Ƃ��܂����B

�S��

���c��

���i��

�V���N

���������q�D����̃`�F�b�N�����܂����B

|

||||||

|

||||||

�Ȃ�قǁA�A�[�X�͂P�n���Ŗʐς��������Ƃ������Ƃł��ˁB�ł��R���f���T�̎����������炷�̂ɂ͏�����R������̂ŁA

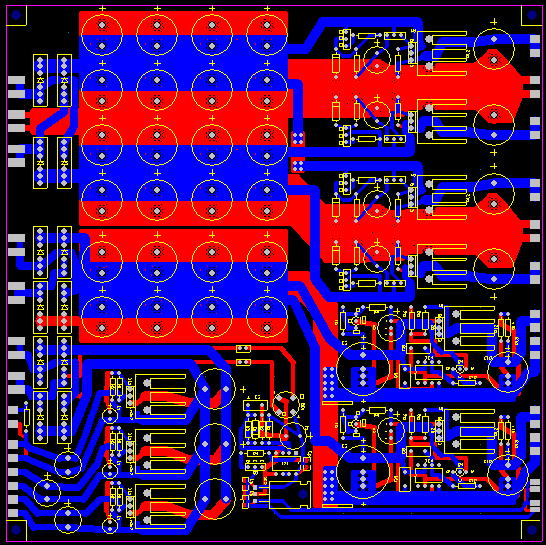

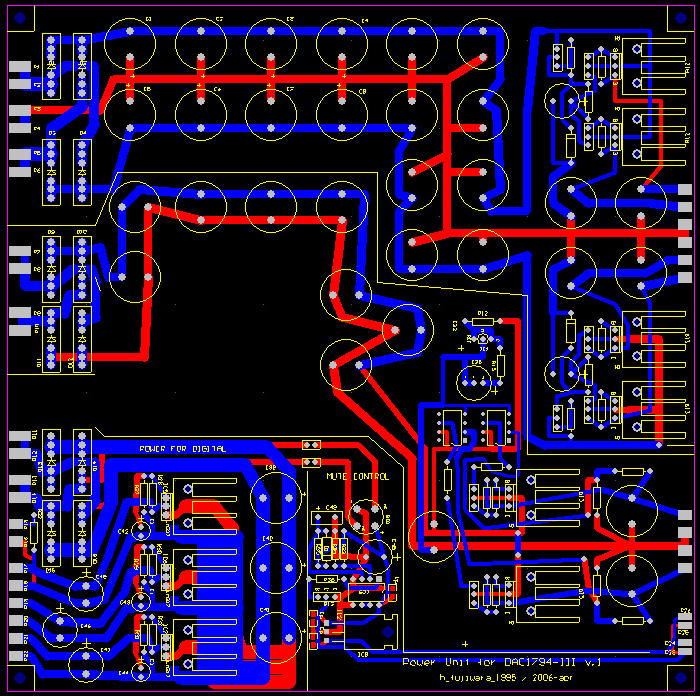

�啝�Ƀp�^�[�����������܂����B�܂��͕��i��z�u�������āA�p�^�[���Ă��l���Ă݂܂����B

������H�Ȃ̂ɁA��d�������ʂɂ��邾���ŁA�����]�T���ł��܂����B

�Ƃ������A�������Ċ����p�^�[���̃J�b�g�A���h�y�[�X�g�ł����̂��_���������H

���i�z�u�����蒼���B�ł������ԃX�b�L�����Ă��܂����B

����ɔz�u���������B

R.���烁�[�����������܂����B

|

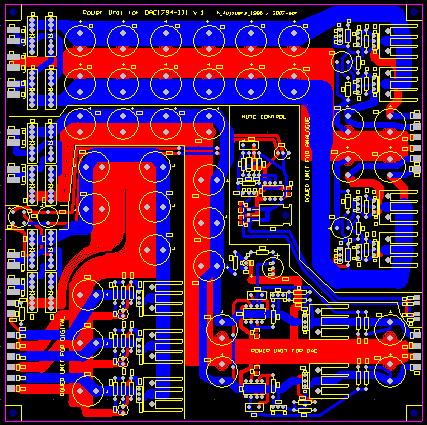

�d����H�̃p�^�[���ł����A���������炢�̂ʼn摜�ɂ��đ���܂��B �A�i���O���̕����R������ƁALM317�̏o�̓R������̈����� �ύX���Ă��܂��B |

�������܂��B

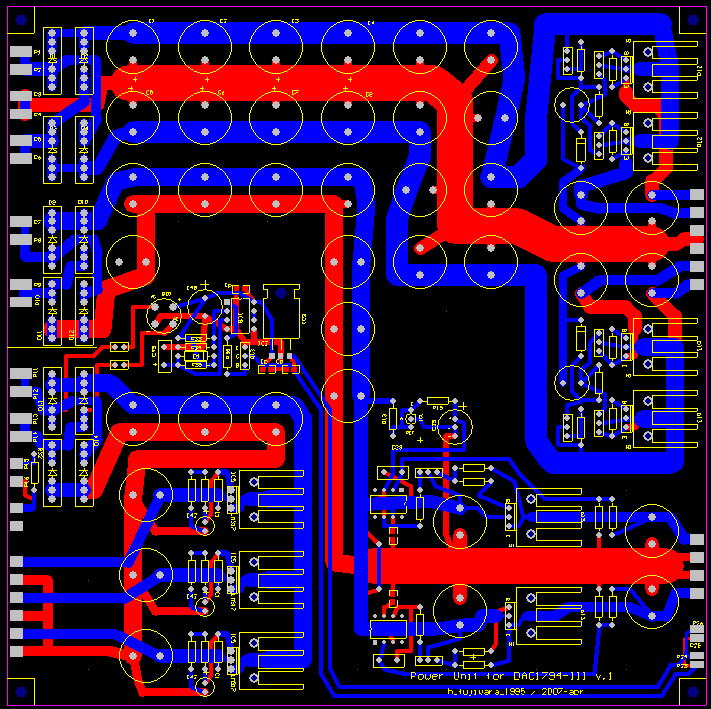

�����āA�ēx�������B���Ȃ�X�y�[�X������܂����A�܂������ł��傤�B

���}���x�[�X�ɂ��Ďd�グ�Ă����܂��傤�B

�������������C�A�E�g�͂���ł��܂肩�ȁH

GND����400mil�i10mm�j�ł����A�قƂ�ǃx�^�Ɠ����Ȃ̂ł����ɕ��i�c�Â�����̂͑�ςł��B

�Ƃ��ɕ��̍L���p�^�[���̂Ƃ���̓T�[�}�������h�ɕύX���K�v�ł��B

����������������Ă݂܂��傤�B

�ύX�_��MUTE��H���ړ����Ă��̃X�y�[�X�Ƀf�W�^����H�p�̕����R���f���T���Q�lj��B

MUTE��H����������ɂ��邽�߁A�m�C�Y���܂��Ȃ��悤��MUTE��H�p�̕�����H�݂̂����[�Ɉړ��B

OPA�g�p�̓d�����̃R���f���T�̔z�u��ύX�B

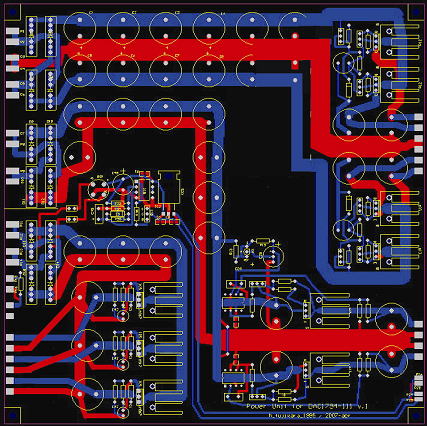

����ȂƂ��납�ȁH

�Ƃ肠���������H

�ŏI�`�F�b�N�͂��Ă��܂A�Ƃ肠���������ł��B

�ȍ~�͂܂��A�uDAC1794D-3�͎������邩�H�v�ɂ��ǂ�܂��B