ちょっとTea Time!? JFE2140って? 2023.3.29

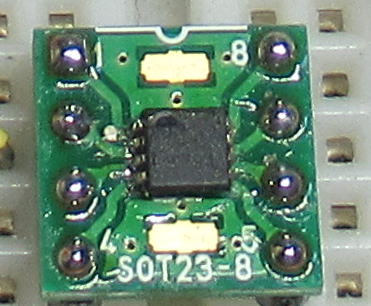

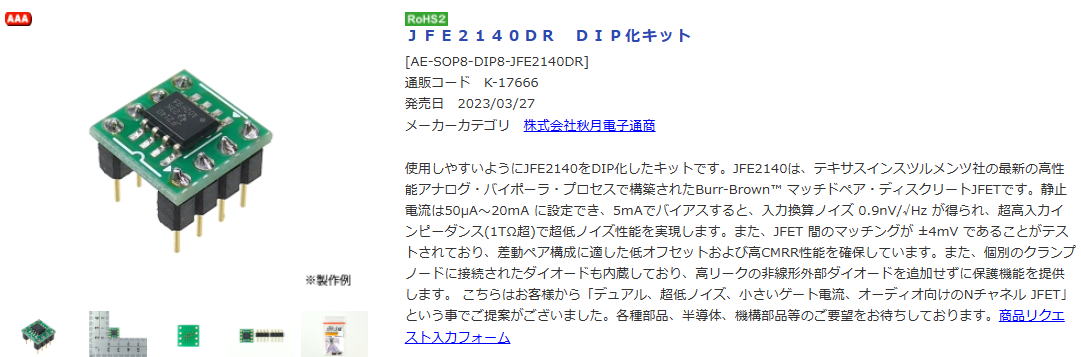

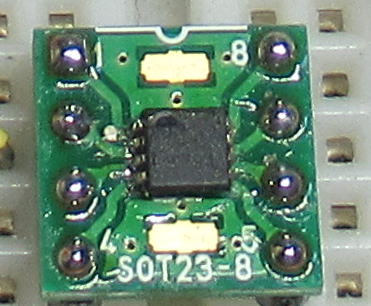

なにやらJFEという某鉄鋼メーカみたいな名前の素子をつかったDIP化キットが秋月ででていた.

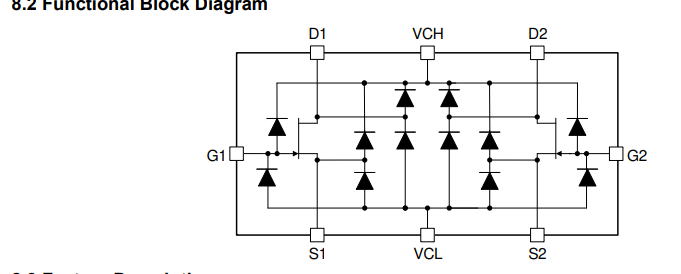

中身はどうやらDUAL FETらしい.

面白いは、FETのGDSにすべてクランピングダイオードがついている点.

おそらく、低電圧でつかうことを想定して保護用に入れてあるのかな?

なによりも、ペアマッチがとってあるのがいいかもです.

FETのペアリングも結構面倒ですしね.

こんなものが秋月からでていました.

データシートはこれ. → jfe2140.pdf

秋月のサイトにあるかと思ったらメーカサイトを参照してほしいとのこと.

ひょっとしてメーカから自社のHPに掲載するのはやめて欲しいといわれているのかな?

アップデートができないため嫌がられるのかもですね.

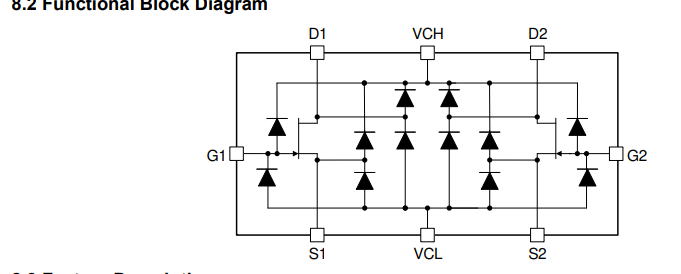

等価回路はこんな感じらしいです. GDSすべてにクランプダイオードがついています.

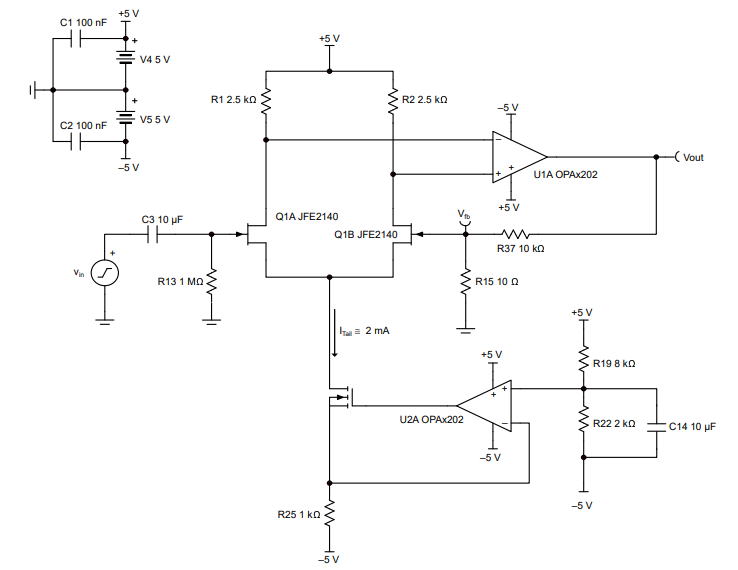

評価ボードもある様子

この素子様に評価ボードもあるようです.

評価ボードのデータシートはこれです → slpu010.pdf

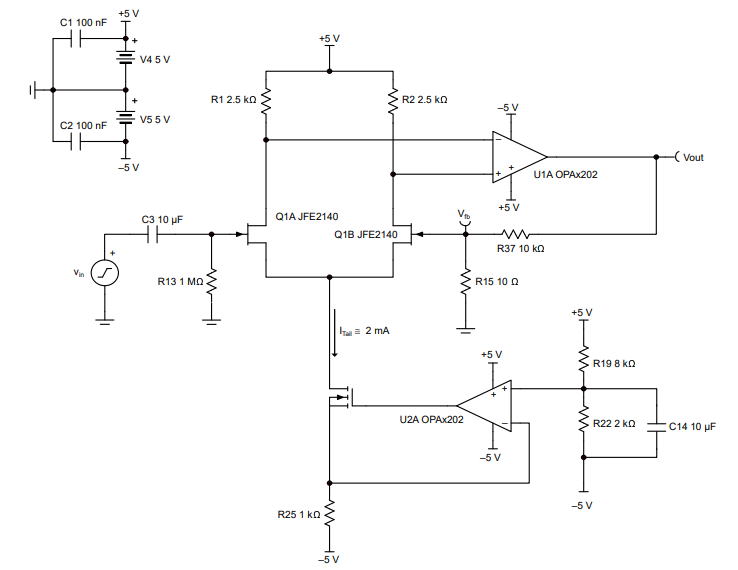

評価ボードの回路はシンプルで、60dBのアンプになっています.

初段をJFE2140で受けて、あとはOPアンプで増幅です.

ただ、アンプの回路としては初段が重要なので、そこにこの高精度なFETをつかうことに大きな意味がありますね.

回路をみて面白いとおもったのは、FETの駆動の定電流回路にOPアンプが使われています.

この部分はトランジスタ1個で済ます場合が多いのですが、OPアンプを使った負帰還による

定電流回路にしたほうが、電流の安定性がいいのかもしれません.

こんな評価ボードもあるようです.

評価ボードの回路はシンプルです. 60dBのアンプになっています. FETの定電流回路はOPアンプが使われています.

とりあえず

1個買ってみましょう. A12アンプの初段につかってみてみても面白いかもです.

週末にでも遊んでみましょう.

とりあえず買ってみました.

とりあえず、その2 2023.4.2

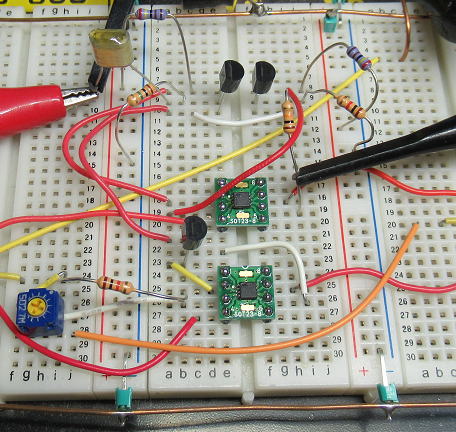

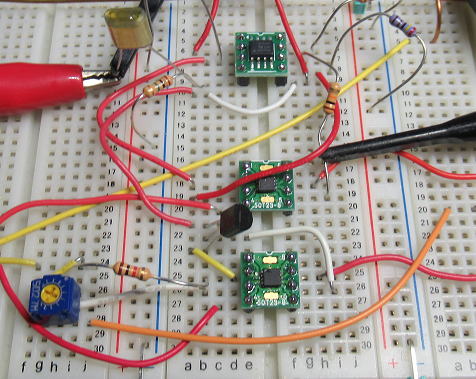

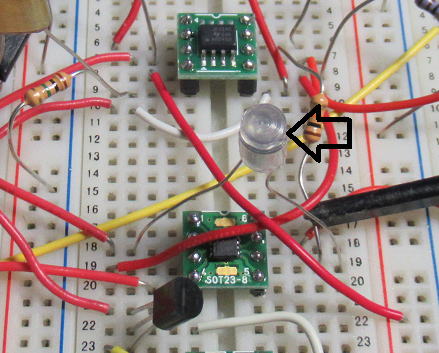

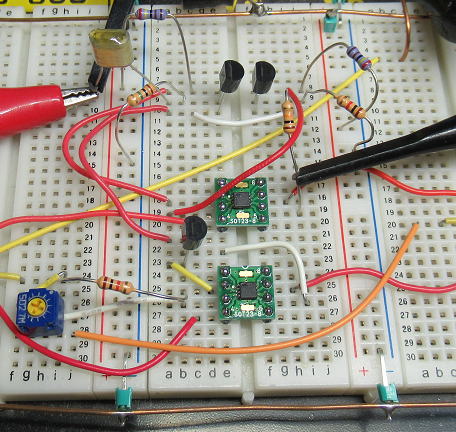

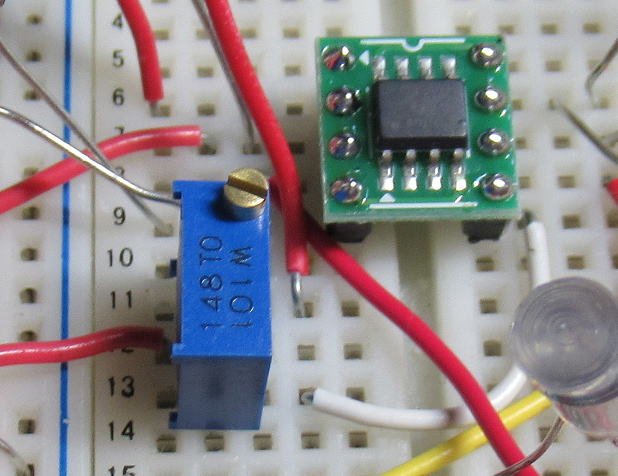

とりあえず先の回路図でブレッドボードで動かしてみることにしました。

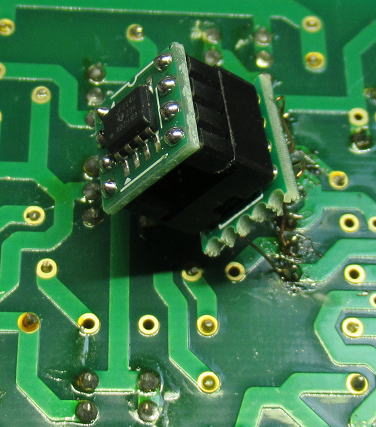

OPアンプは±5Vで動作するものが必要なので、OPA727を使いました。これはDIPパッケージがないので

変換基板をつかっています。OPA727はRail to Railで動作し、かつ性能がいい割に安価なので計測用途には

結構重宝しそうなOPアンプです。

で、最初に動かすときにいきなりJFE2140を壊してしまう可能性も考えて、2SK246GRで組んで動作を確認です。

動作確認の目的もありますが、ペアリングもせずに選んで2つでどのくらいオフセットが生じるかの確認でもあります。

まずは2SK246GRをつかって回路の動作確認です。

OPA727ですが、変換基板を間違えてしまったのでピンをすこし内側に曲げてとりつけています。

2SK246のペアリングなしだと、オフセット大きいなあ〜

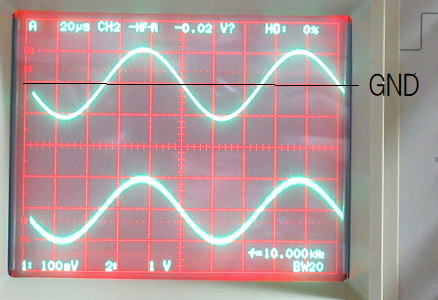

まずは電源を入れてみました。とりあえず問題なく動作はしているようです。

なお、回路としてはゲインを10倍(10kΩと1kΩ)にしています。正確には11倍ですが。

オフセットについてはかなり大きいです。 約500mVでています。本来はオフセット調整

用のVRがあるので、それで調整するのですが、現在はなにもありません。

そのため2SK246の特性のバラつきに加えて、抵抗(一応1%を使っている)の誤差が

効いてきています。まあ、抵抗の誤差よりFETのバラつきの方が支配的でしょう。

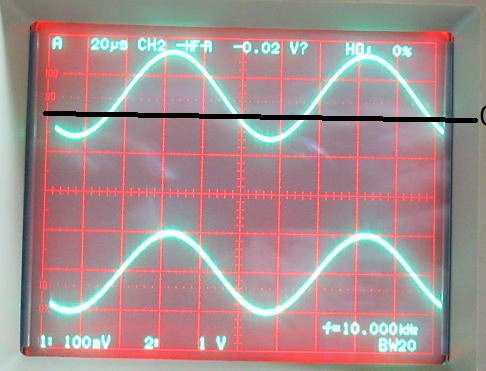

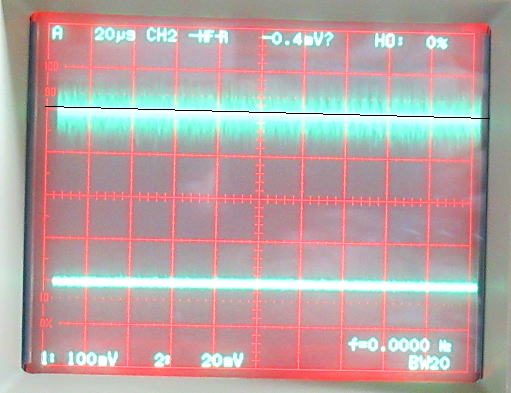

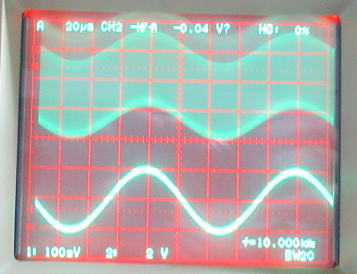

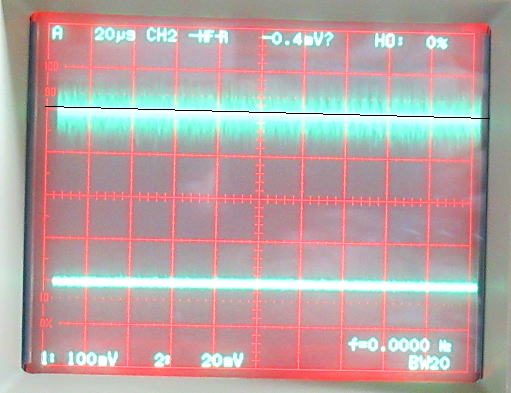

下(1):入力 上(2):出力 オフセットは約500mVでています。

今度はJFE2140に差し替え

回路が動くことも確認できたのでJFE2140に差し替えです。 差し替えといっても、

ピンレイアウトが違うのですこしブレッドボードでの配線も変更です。

さて、JFE2140に差し替えて電源を入れたら、出力が発振していました。

まあ、FETによって発振することはよくあることなので、適当な容量のコンデンサを

発振止めに追加です。

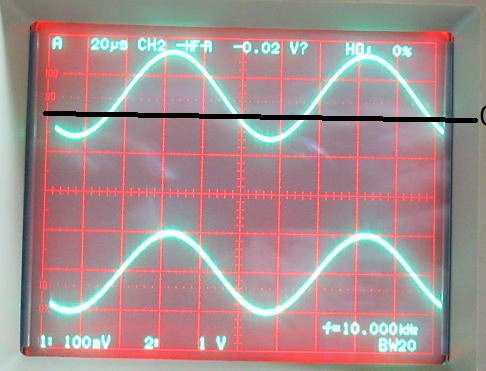

発振もとまって出力波形を見てみると、ほとんどオフセットも無いようです。

やはりマッチングがとれているFETだといいですね。JFE2140じゃ2SK246の2個より

かなりお高いですが、10数個程度の値段なので、ペアリングする苦労と余ってしまう

FETを考えると、最初からJFE2140をつかうのも妥当かもしれません。

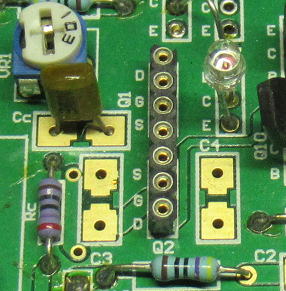

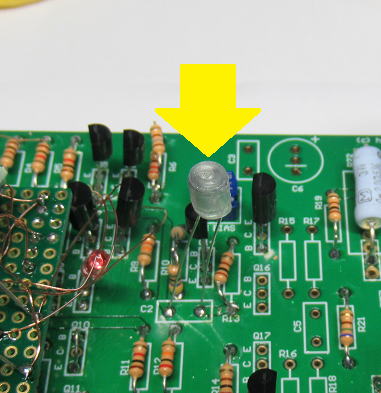

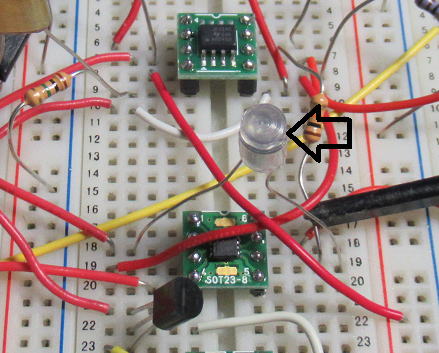

JFE2140(一番上に写っているデバイスです)に差し替えました

そのままだと発振してしまいました。

発振防止に47pFのコンデンサをOPアンプの負入力と出力の間に挿入です。

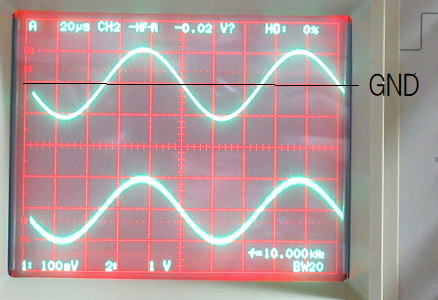

発振も止まりました。オフセットもほとんどないようです。

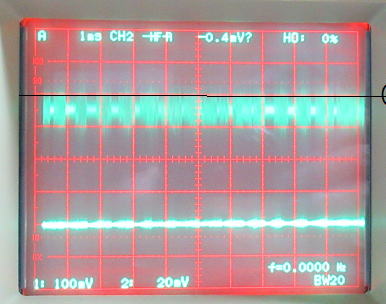

どのくらいのオフセットかな?

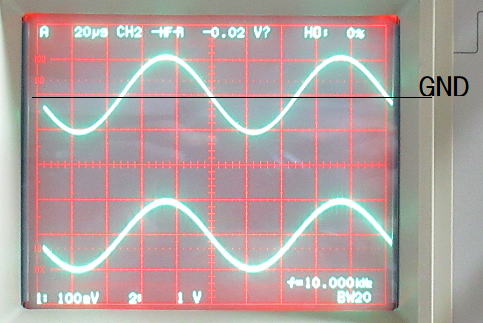

すこし、オフセットを細かくみてみることにします。入力をGNDに接続して

出力を観測しますが、およそ10mV程度のオフセットがでているようです。

ゲインが10倍ですからFETとしては1mVのオフセットでしょうか。かなり小さいですね。

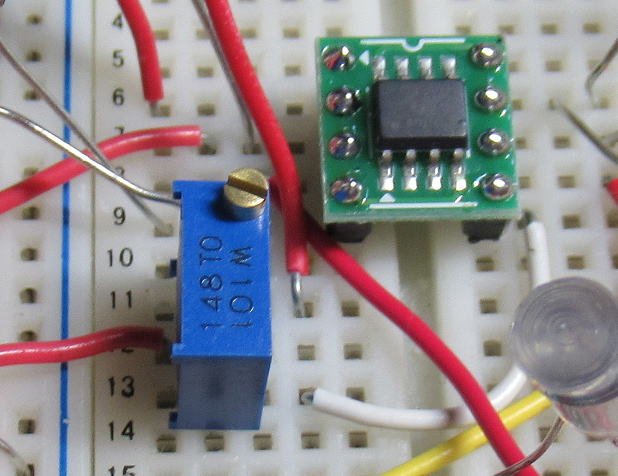

一応オフセットを取るために2つのソース間に100Ωの半固定抵抗を入れてみると、

ちょっと回すだけで簡単にオフセットゼロとなりました。 安定性も良さそうです。

下(1):入力 上(2):出力 オフセットは約10mVのようです。

オフセット調整のVRも取りつけてみました。

VRで容易にオフセットゼロになります。

Renew A12A基板に乗せてみましょう! 2023.4.3

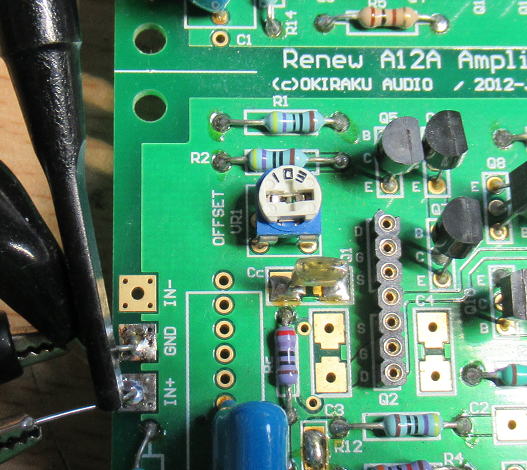

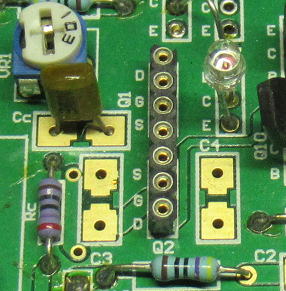

テストに使ったRenewA12A基板があるので、それにJFE2140を搭載してみましょう。

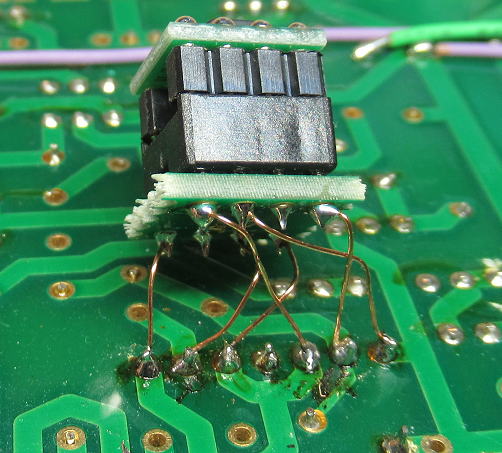

この基板は色々なFETが試せるようにソケットがついているのですが、これに直接接続(半田付け)

すると、あとあと使えなくなってしまうので、基板の裏側に接続です。

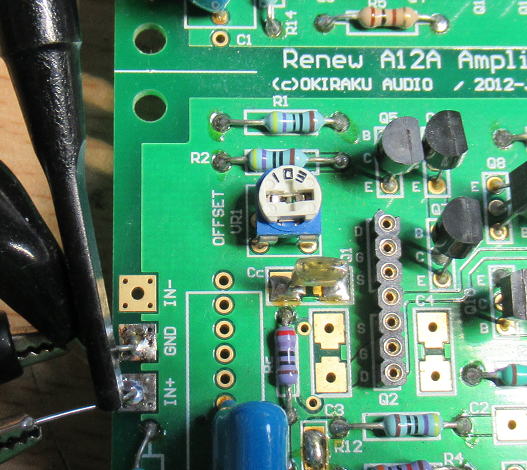

そして、電源を入れる前にオフセット調整用のVRは中点位置にセットしておきます。

で、おもむろに電源ON. 波形が問題なく観測できました。

オフセットもほとんどでていないようです。

やっぱり、ペアFETをつかうと便利ですね。

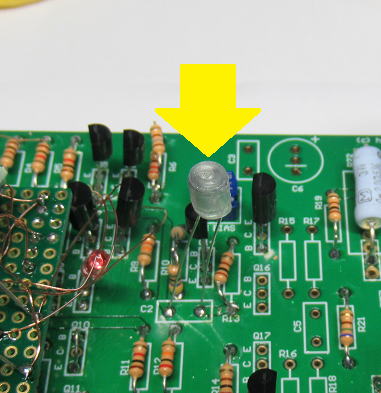

このソケットを埋めたくなかったので、裏側にJFE2140を取り付けです。

こんな感じで取り付けです。

反対側の様子です。

オフセット調整用のVRは中点位置にセットです。

無調整ですが、ほとんどオフセットものっていないです。

やっぱりペアFETは便利ですね。

さてさて、これからどうしようか?

JFE2140が使えるようなパワーアンプ基板があってもいいかな〜という気がしてきました。

ただ、A12の回路をそのままだと電源電圧を30VくらいまであげるとFETの耐圧を超えてしまうのです、

初段にはカスコード接続が必要です。 一度、回路をSPICEしてみるかな〜。

#ああ、週末の締め切りの原稿が全然できていないよお〜(焦

#現実逃避ばっかりだあ〜。

パワーアンプの回路を書いてみる 2023.4.4

#さらなる現実逃避が続きます(笑。

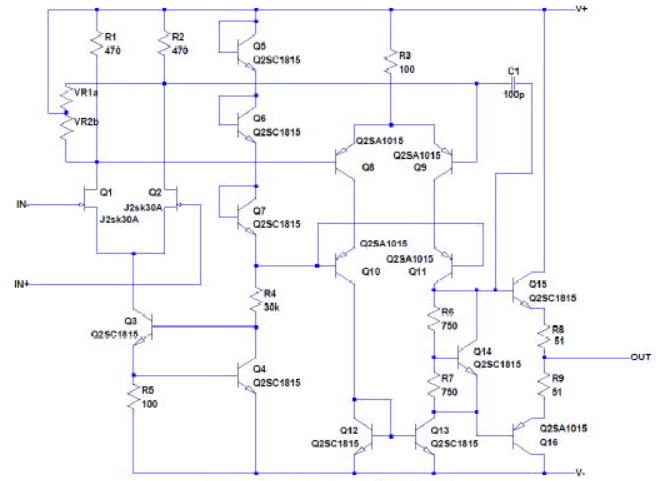

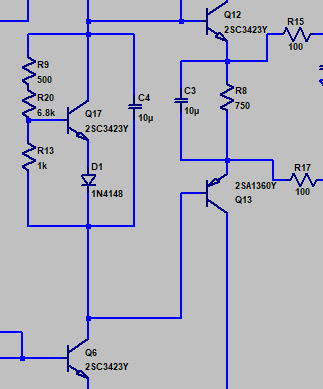

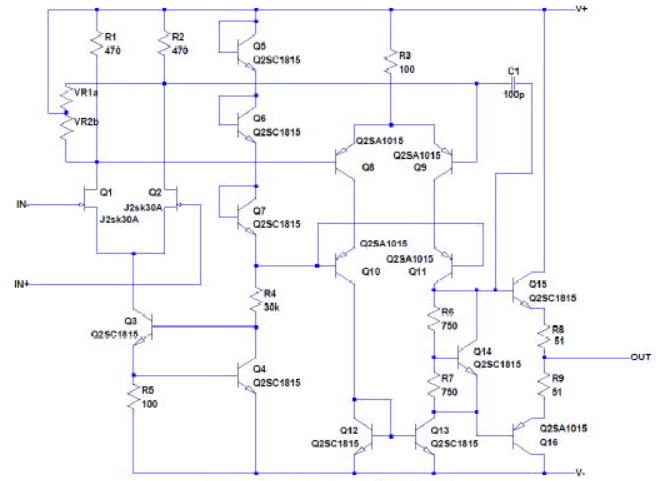

さて、A12回路をベースにしてパワーアンプの回路を書いてみました。

A12をベースといっても、結局のところ2段の標準的な回路になっています。

FETの耐圧を考えて、初段はカスコードをつけて、あとカレントミラーもオマケでつけました。

A12アンプの回路です。これをパワーアンプ用に修正です。

こんな風に書いてみました。

一度バラックで組んでみるかな?

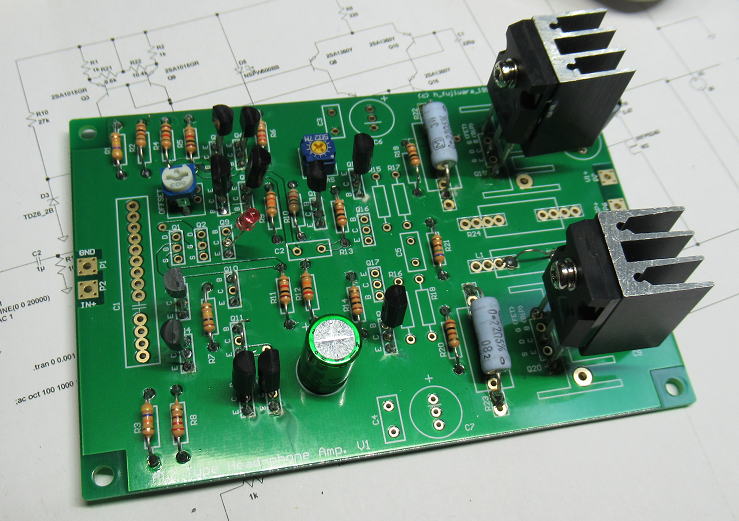

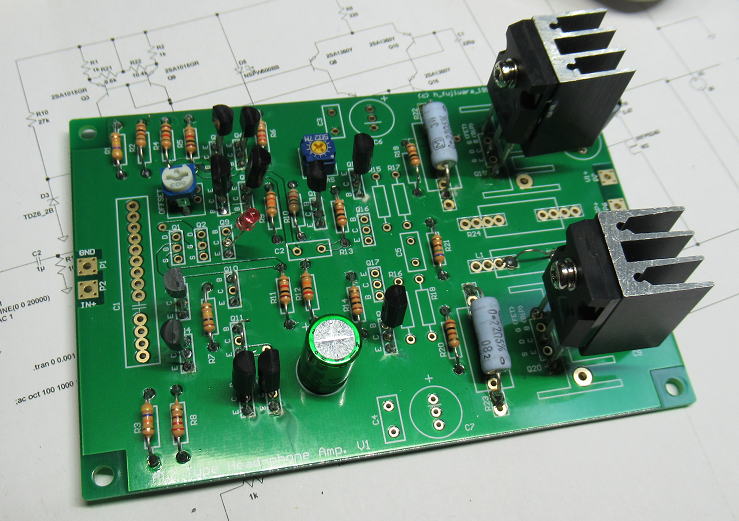

A12-HPAをベースに組んでみました 2023.4.20

アンプの更新も一息ついたので、こちらにもとりかかりました。

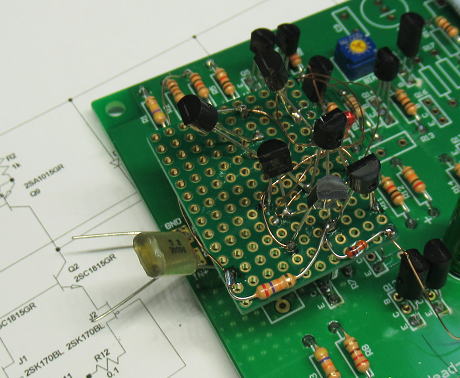

検討している回路はA12-HPAの入力段をすこし変更しただけなので、A12-HPA基板をベースにして、

試してみることにしました。

入力段にはカレントミラーとカスコード回路が追加されているので、A12-HPA基板をそのままつかうわけにはいきません。

ということで、入力段は別基板に実装するとして、それ以外をA12-HPA基板で作成です。そして、入力段は延長した

基板上に作成です。最初に動作確認のため2SK246BLをつかって組み立ててチェックしました。

入力段以外は同じなので部品を実装です。横着して過負荷防止回路は未実装です。

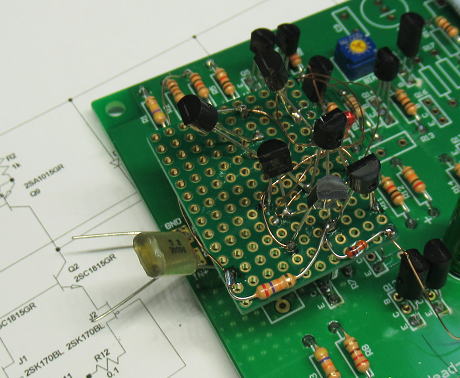

入力段にはカレントミラーとカスコード回路が入るので別基板で作成です。

まず最初は2SK246BLをつかっての動作確認です。

2SK246をつかっての動作確認完了です。

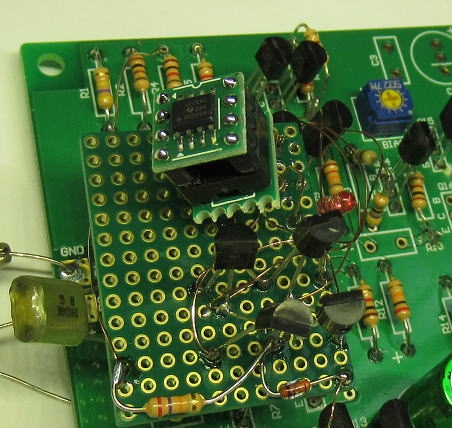

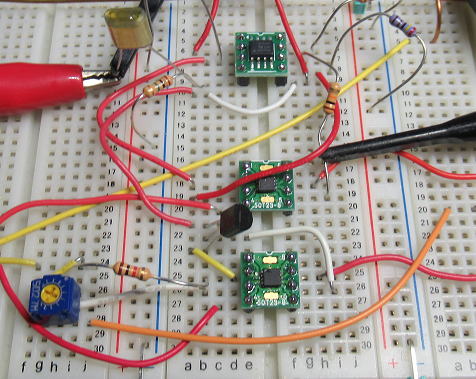

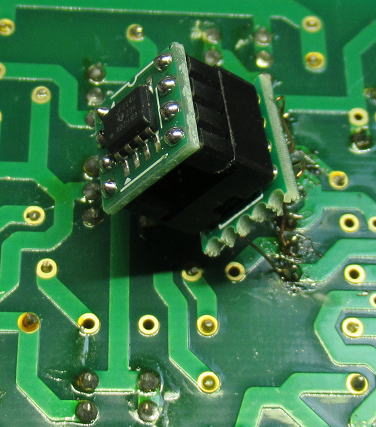

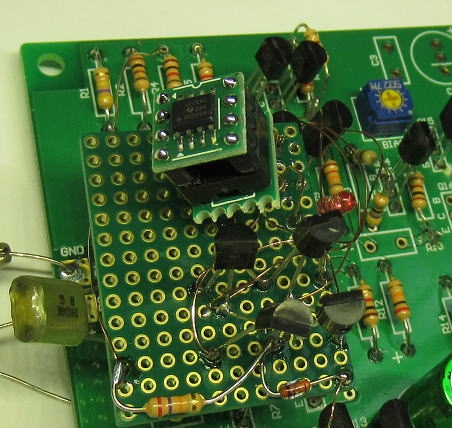

今度はJFE2140に入れ替えてみましょう

2SK246での動作確認ができたので、今度はJFE2140に入れ替えての動作確認です。

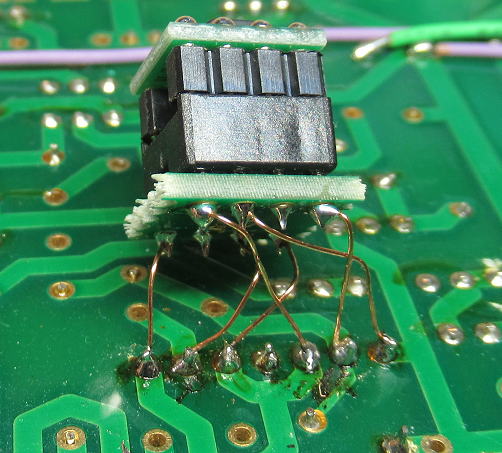

2SK246のときは発振防止用のコンデンサはなしだったのですが、JFE2140に入れ替えて

電源をONにしたところいきなり発振したので、1箇所にコンデンサを追加しました。

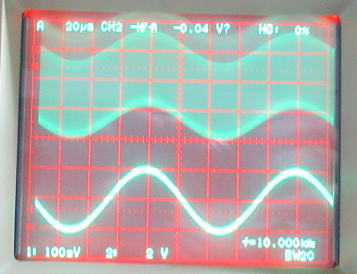

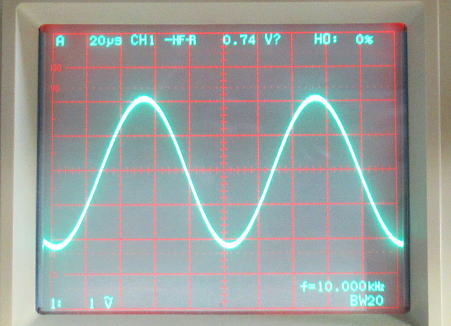

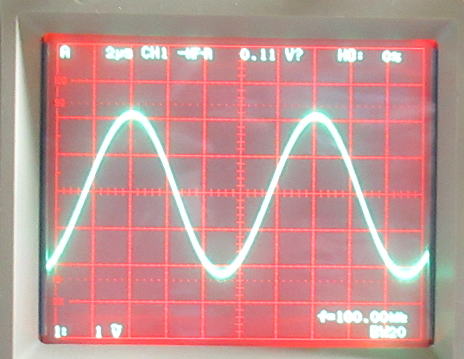

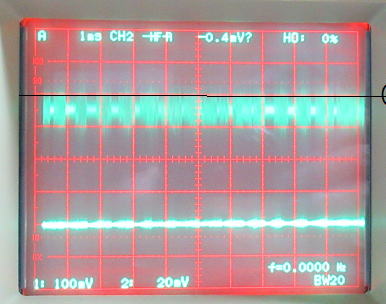

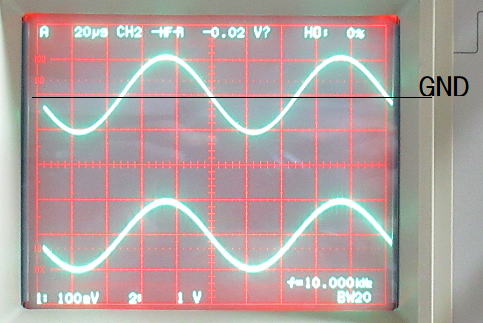

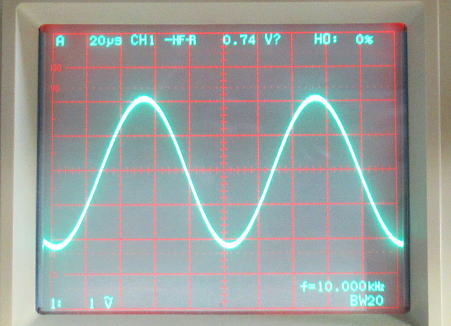

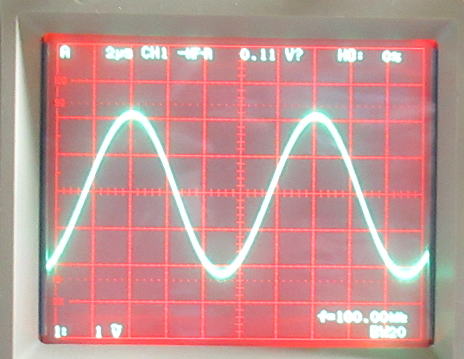

あらめて電源を入れると発振もとまり、綺麗な波形がでてきました。

周波数特性も問題ないようです。 電源電圧は実験用電源なので±24Vで動かしています。

さらに高い電圧でも試してみましょう。

2SK246の替わりにJFE2140に入れ替えてみました。

発振したので、コンデンサを追加です。貧乏性なのでリード線は長いままです(笑

綺麗な波形がでました。周波数特性も良好です(図は100kHz)

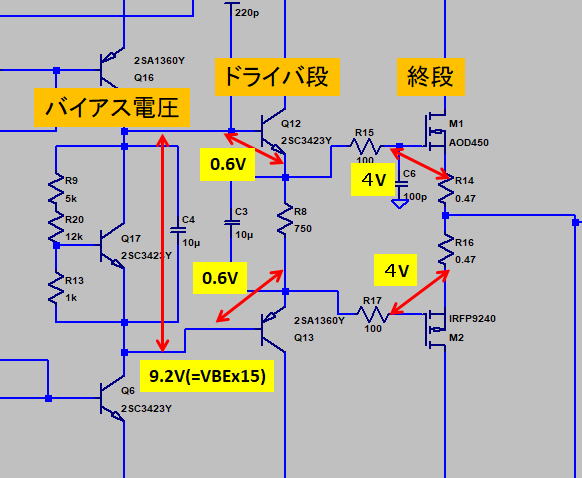

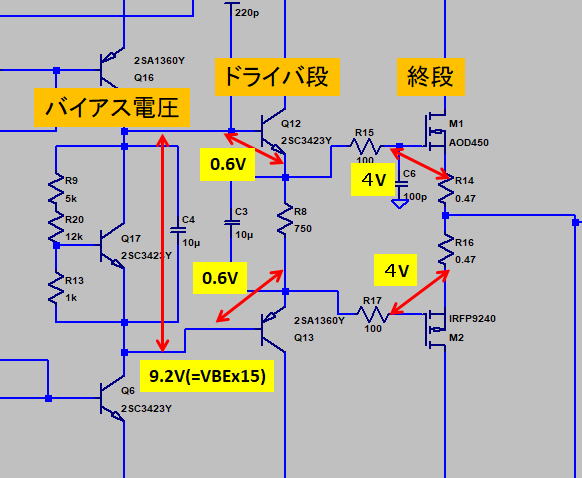

ちょっとバイアス電圧に関する検討 2023.4.21

アンプをAB級で動かすには出力ゼロ電位の時にも終段に幾ばくかの電流を流す必要があります。

そのために、終段のVGSには一定電圧をかける必要があり、そのために必要なのがバイアス電圧です。

でも、これってMOSFETの場合だとVGS電圧が高いので、バイポーラトランジスタに比べて

かなり高い電圧が必要です。そこで、いまさらではありますが、バイアス電圧の発生回路を

再度検討です。

検討の主眼は、バイアス発生TRとMOSFETを熱結合させることを前提とした場合に、

温度の影響を小さくしてバイアス電流を一定化させるか、という点です。

ちなみに、小生の場合はMOSFETでは熱暴走が起きにくいので、熱結合はしていません。

冷えた状態でのバイス電流から、増えた電流で平衡するので、最初は比較的小さい電流(数10mA)に設定しています。

終段MOSFETにバイアス電流を流すたまには大きなバイアス電圧が必要です。

しかしバイアス発生TRの発生電圧が大きいので、MOSFETを熱結合させ場合は、

過度にバイアス電流を下げてしまうことが懸念されます。まあ、安全側ですが・・・・。

MOSFETとは−ゲートしきい値電圧、ID-VGS特性と温度特性 | トランジスタとは−分類と特徴 | TechWeb (rohm.co.jp)

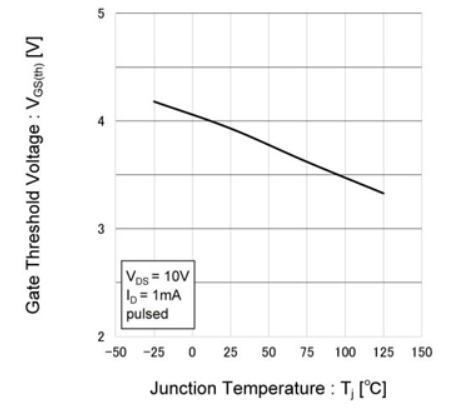

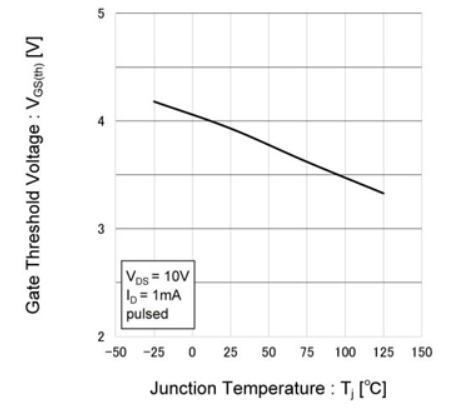

上図のグラフからみるとMOSFETのON時のVGSの温度計数は-5.6mV/℃です。

となると、N-chとP-chの両方あるわけですから合わせて-11,2mV/℃になります。

すなわち、アイドル電流を常に一定にしたい場合は、MOSFETの温度が1℃あがったときには

MOSFETのゲート間電圧を11.2mVだけ下げればいいのですが、一般にバイポーラトランジスタの

VBEの温度係数は -2mV/℃なので、バイアス回路でVBEを倍率15倍にしていれば、

バイアス電圧回路の温度係数はは2mV/℃ x 15 = -30mV/℃になります。

すなわち、先の回路だと1℃あたり30mVも下がってしまいます。

これは下げ過ぎな感があります。たとえば大音量で音楽を鳴らして、MOSFETが加熱した状態ではアイドル電流が大きく

下がってゼロになる可能もでてくるかもしれません。

本来はバイアス回路での温度計数はMOSFETの温度係数11.2mVとドライバ段の温度計数4mVを足した15.2mVを少し

上回る場合にすべきなのかもしれません。となると、バイアス電圧回路での倍率は15.2/2=7.6倍を少し上前る程度

でしょう。上図の回路では15倍程度の回路になっていますから、バイアス電圧回路で発生させる電圧の半分程度は別に

電圧をかさ上げして、倍率を半分程度にしたほうが良さそうです。

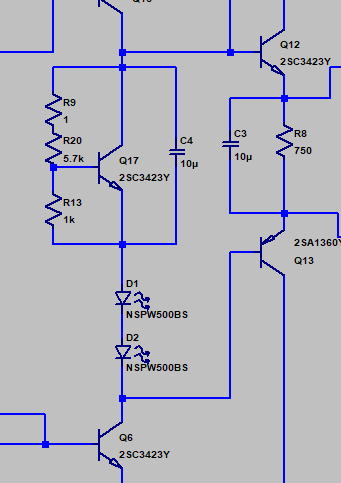

9.2Vの半分ですから4.6Vになるので、ちょうどLED(赤:VF=2.2V程度)の2個分です。ということで、

バイアス電圧回路にはLEDが2個直列に入れるのがいいのかもしれません。あるいは

バイアス回路トランジスタのエミッタにダイオードを追加して見かけのVBEを1.2V程度の倍にあげるのも

いいかもです。これでも、実質的に倍率は半分になります。

部品点数的にはダイオードを追加するほが簡単かなあ〜。ただ、調整のやりやすさではLEDを使う方がいいかもです。

どうせなら、どちらも使えるようにしておくのが色々と遊べるかもしれません。

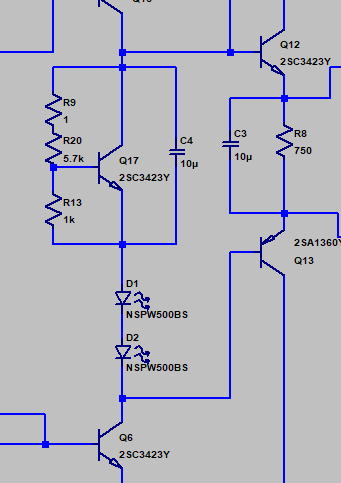

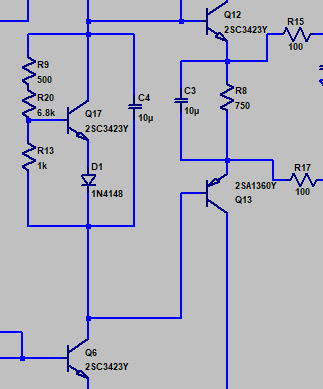

バイアス回路にLEDを2個追加して電圧をかさ上げするパターン。

バイアス回路にダイオードを追加して電圧をかさ上げするパターン。

ただ、先に述べたように個人的にはMOSFETの場合は熱結合は不要かな〜と思っています。

というのもMOSFETのON抵抗は正の温度係数なので熱暴走はありません。

これは概ねVGSが5V以上の場合ですが、たとえ5V以下であっても、エミッタ抵抗

があるので、電流増加でVGSが下がる度合が大きいですからアイドル電流の暴走は

抑制される方向になります。

しかし、ここまできたら基板を作ってみたくなりました。

Tea Time!?から卒業するかな?

基板を描いてみることにしました.

(Tea Time!?はおしまい)