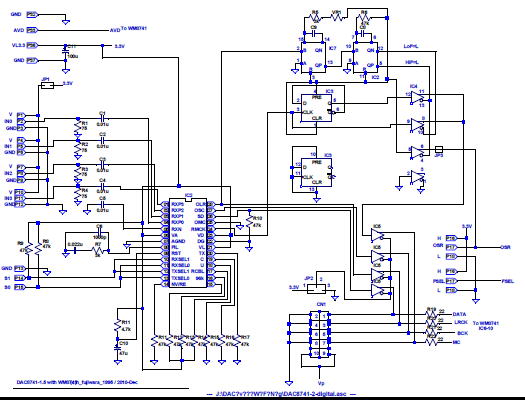

DAC8741-2検討記(続編) 2010.12.29

前編はこちら。

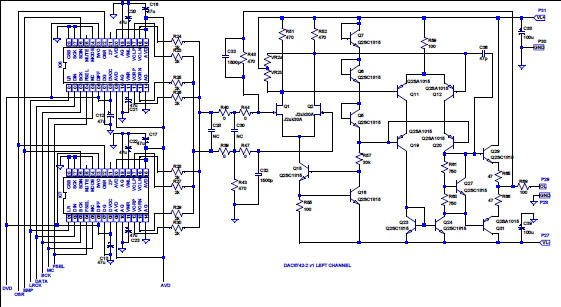

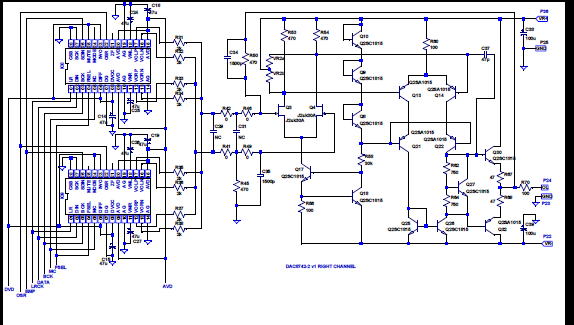

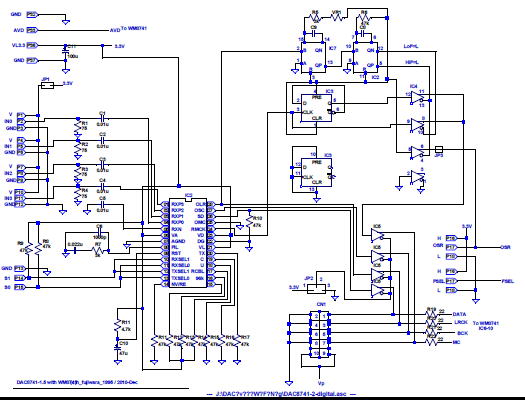

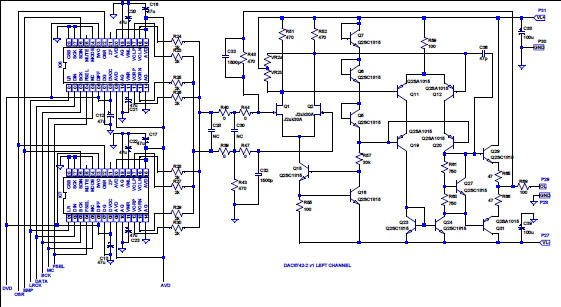

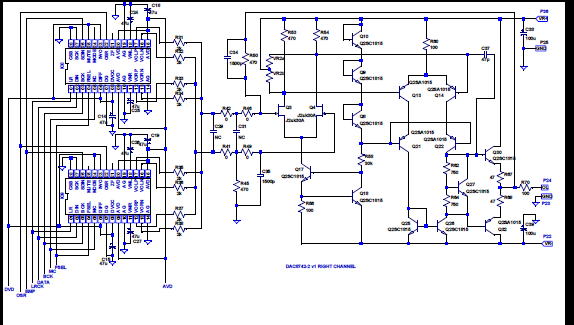

やっと重い腰をあげて回路図を描いてみました。間違いがあるかもしれませんが、

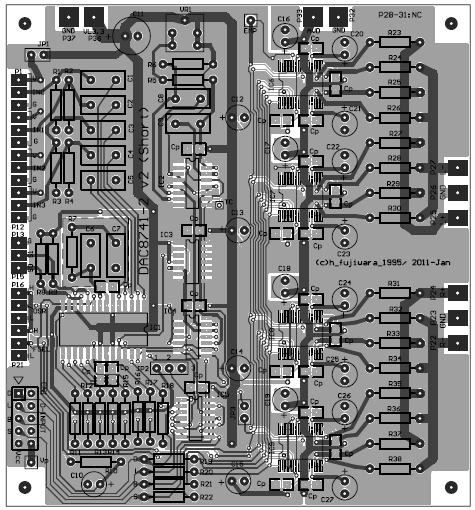

こんな感じです。それぞれクリックするとPDFが立ち上がります。

ディジタル部

DAC部 Lチャンネル

DAC部 Rチャンネル

メモリーバッファーとの接続

DAC基板のCN1端子をつかってメモリーバッファーとの接続を確認してみました。

メモリーバッファは2種類用意しています。

1つは無改造のもの。これのシステムクロックは128fs固定です。

もう一つはシステムクロックfsを可変にしているものです。

ちょうど下のようなシステムクロックになります。

|

メモリ-バッファー |

| fs |

オリジナル

システムクロック

(128fs) |

改造後 |

| 44.1kHz |

5.6448MHz |

16.934MHz(384fs) |

| 48kHz |

6.144MHz |

24.576MHz(512fs) |

| 96kHz |

12.288MHz |

24.576MHz(256fs) |

| 192kHz |

24.576MHz |

24.576MHz(128fs) |

本来WM8741は44.1kHzおよび48kHzでは128fsはサポートしていないのですが、

以前の実験では動くようなので、無改造のメモリーバッファーも確認してみることにしました。

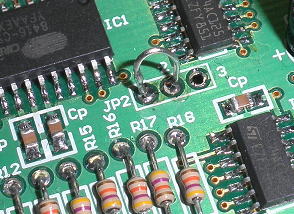

メモリーバッファーと接続するには

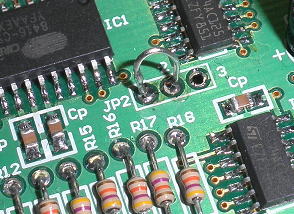

DAC基板側のジャンパーの変更が必要です。JP3はサンプルレートを外部で切り替えるために

必要なので開放にします。JP2については1−2間を接続してCN1からの入力を受け入れます。

JP3は開放に設定 JP2は1−2間を接続

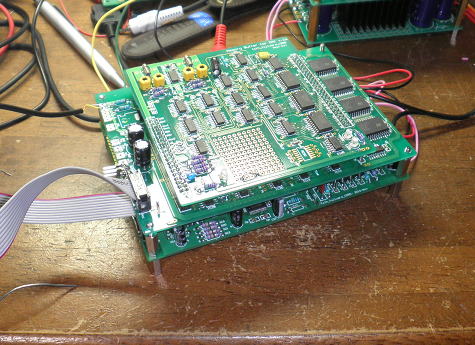

メモリーバッファーとDAC基板との接続は10Pのフラットケーブルでおこないます。

メモリーバッファーは5Vで動作しますが、DAC基板のデジタルは3.3Vなので

電圧差があるので若干心配ですが、まあやっちゃエーということで確認しています(あくまでも自己責任で)。

あとでメモリーバッファーが3.3Vで動作するかも確認してみましょう。

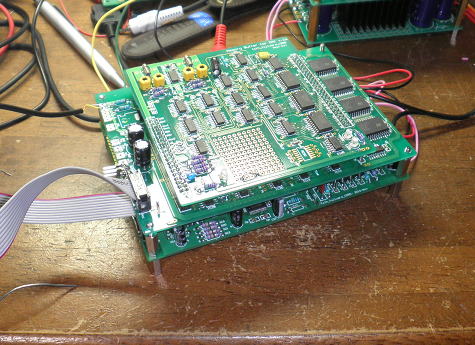

メモリーバッファーとDAC基板との接続

OSR(基板端子P17)に設定

DAC基板端子P17(OSR)の設定をどのように変えれば動くか表にしてみました。

192kHzのときのみP17をHigh(P16へ接続)すればいいようです。

|

メモリ-バッファー |

|

| fs |

オリジナル版

システムクロック

(128fs) |

P17(OSR)の設定 |

| 44.1kHz |

5.6448MHz |

無接続 |

| 48kHz |

6.144MHz |

無接続 |

| 96kHz |

12.288MHz |

無接続 |

| 192kHz |

24.576MHz |

H(P16に接続) |

|

メモリ-バッファー |

|

| fs |

改造後 |

P17(OSR)の設定 |

| 44.1kHz |

16.934MHz(384fs) |

無接続 |

| 48kHz |

24.576MHz(512fs) |

無接続 |

| 96kHz |

24.576MHz(256fs) |

無接続 |

| 192kHz |

24.576MHz(128fs) |

H(P16に接続) |

メモリーバッファーは3.3Vで動くか?

ためにしメモリーバッファーが3.3V電源で動くかためしてみました。

メモリーバッファーには3.3Vの3端子レギュレータが載っていますが、これのIN-OUT間はショートさせておきます。

結果からいうと96kHzまでは動きましたが、192kHzでは動作が安定しないようです。

もともとメモリーなども5V動作を基本としていますが、電圧が落ちた分だけ速度が落ちたのでしょう。

メモリーバッファーは5Vで動作させた方がよいようです。

気になるはメモリーバッファーとDAC基板の電圧差ですが、

IC5を74AC125から74LVC125あたりに換装しておいた方が精神的にはいいかもです。

まあ、これは部品を購入したときにでも取り替えてみましょう。

消費電流は?

どのくらいか測ってみました。DAC基板単体での値です。

| DAC基板の消費電流 |

|

44.1kHz |

48kHz |

96kHz |

192kHz |

| デジタル電源3.3V |

97mA |

102mA |

197mA |

220mA |

| DACアナログ5V |

183mA |

186mA |

210mA |

210mA |

| アナログ+15V |

29mA |

29mA |

29mA |

29mA |

| アナログ−15V |

34mA |

34mA |

34mA |

34mA |

ディジタル電源3.3Vは周波数があがると電流が増えます。

DACアナログ電源も周波数につれて若干あがります。

いづれもこのDAC基板は意外で電流を消費しますので、電源の放熱板は余裕のあるものが必要でしょう。

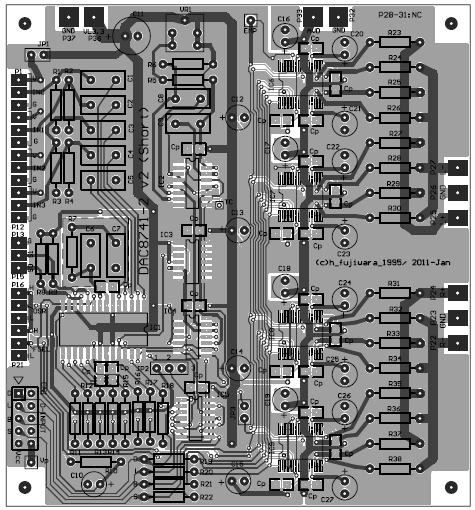

こんなものもリクエストあるようで・・・・

アナログ回路を除いた部分です。一応描いてみましたが・・・・

(いきなり続編につづく)