AK557XのADCを調べてみる!の巻き 2023.2.5

(ことの発端)

一つのBBSへの投稿から、ちょっと調べてみようという気が起きてきました。

(中略)

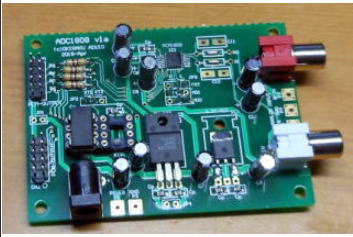

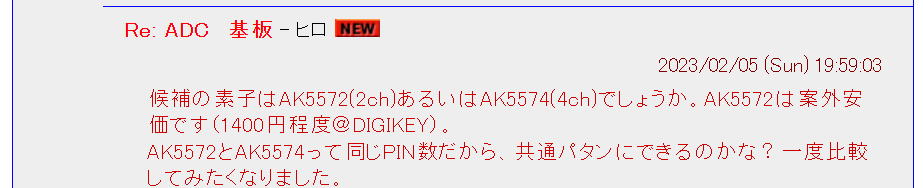

今のADC専用基板のラインアップはADC1808のみ

ところで今のADCのラインアップはどうなっているのかな?と思って改めてHPを見返してみると、

ADC専用のものはADC1808(一応ADC1808-miniもあるが)1機種のみのようです。

これはTI社のPCM1808をつかったもので、24Bit96kHzでのサンプルリングです。

なにより、PCM1808が秋月で180円で買えるのお財布に優しいです。

ADC1808が現在唯一のADC専用基板になっています。

変換素子はPCM1808で秋月で180円で購入できます。

本来はADC5397があって、これがスペック的(32Bit768kHz)にも抜群にいいのですが、

なんせADCの要のAK5397がありません。 基板をリリースした翌年に旭化成の工場が

焼失してしまって、生産が止まってそのままディスコンになってしまいました。

ほぼディスコン状態のADC5397です。基板はあるんだけど素子が無い(泣。

もうAK5397は入手は不可能な状態です。

その他のADCを内蔵した基板は

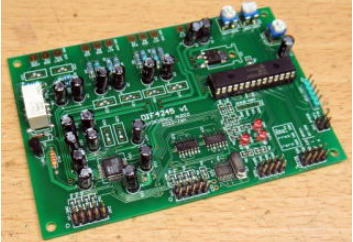

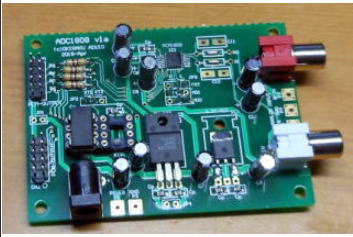

DIF4245はシーラスロジックのCS4245をつかったADC/DAC基板で、これは

24Bit192kHzのサンプリング仕様です。ADC1808よりちょっとだけスペックが高いです。

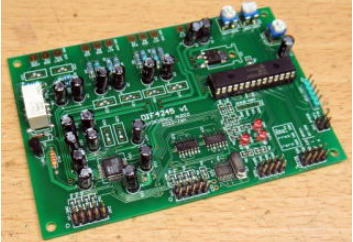

最近ではRenewSRC4137もADCの機能があります。これはDAIであるPCM9211に24Bit96kHzの

ADCを内蔵しているためです。

まあ、96kHz24Bitのスペックがあれば通常使う分には十分のような気もしますが、

やっぱりオーディオって気は心でもあるので(なんのこっちゃ)、あるのなら最高のスペックの

ものを使ってみたいですね。

DIF4245です。24Bit192kHzのADCを内蔵しています。

Renew SRC4137です。基本機能はASRCですが、DAIにADCを内蔵しています(24Bit96kHz)

AKMのADCを調べてみる!

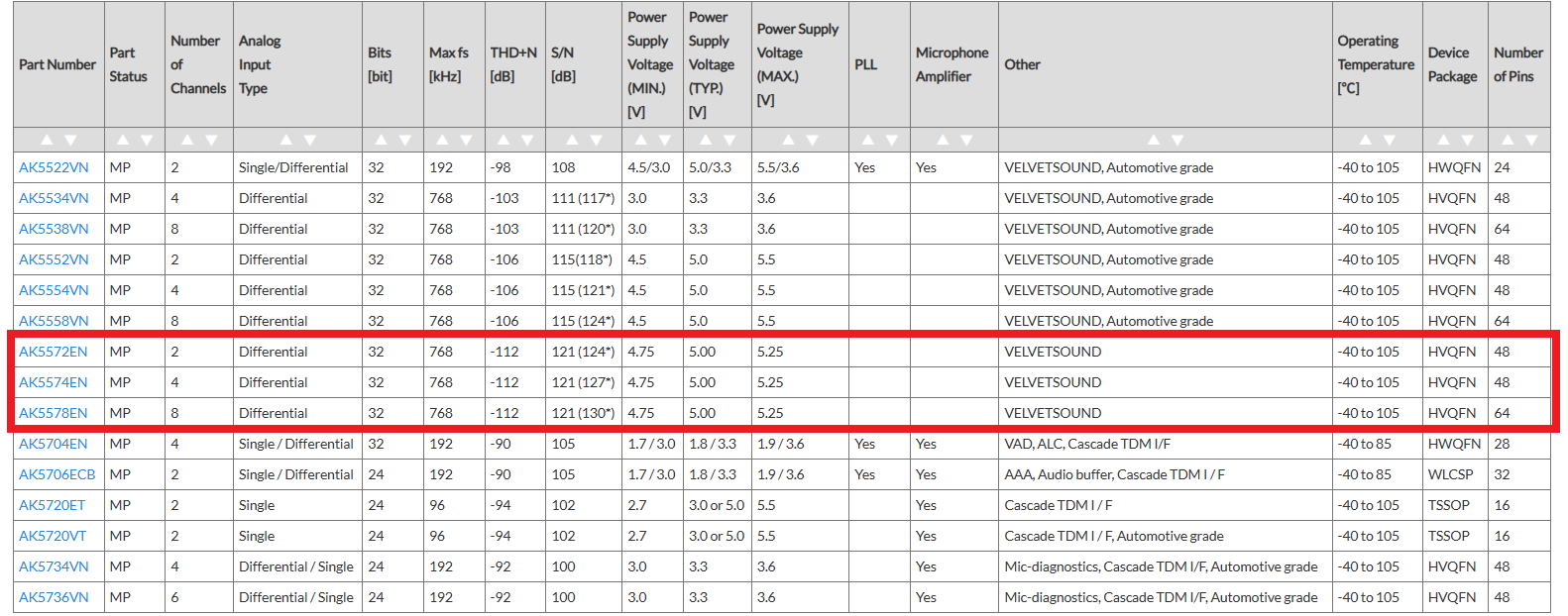

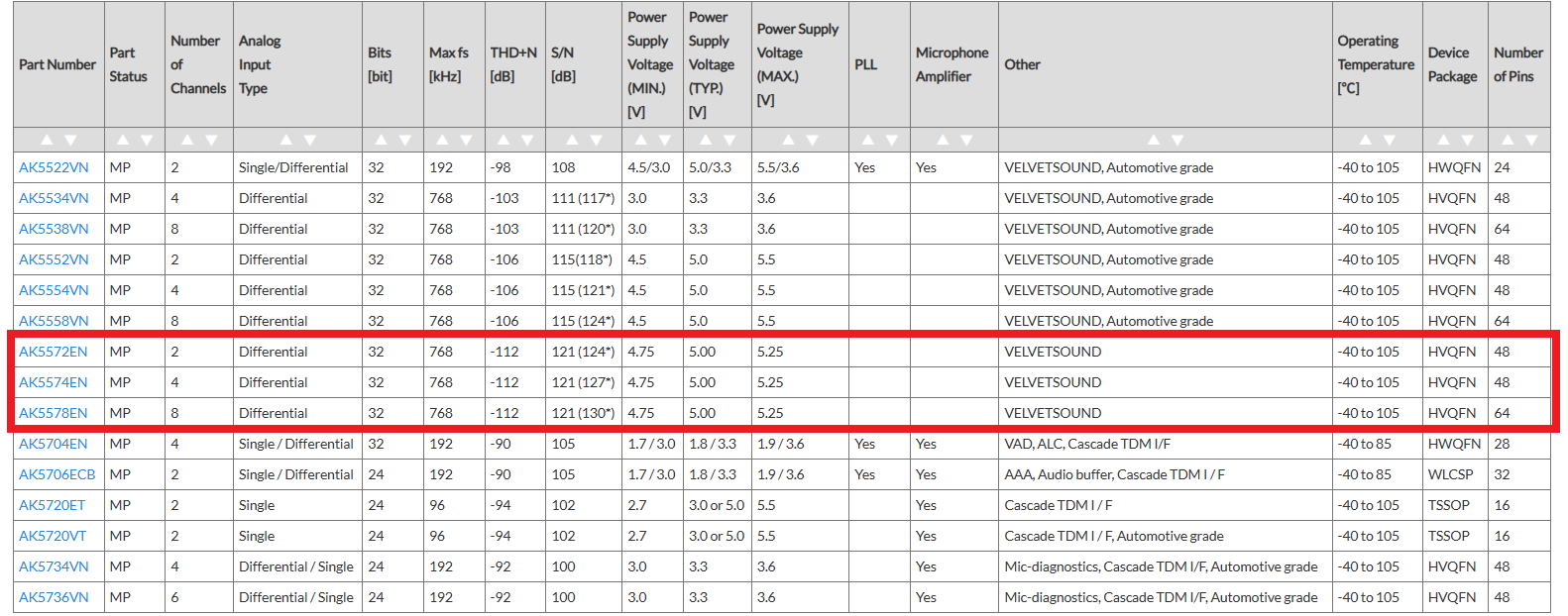

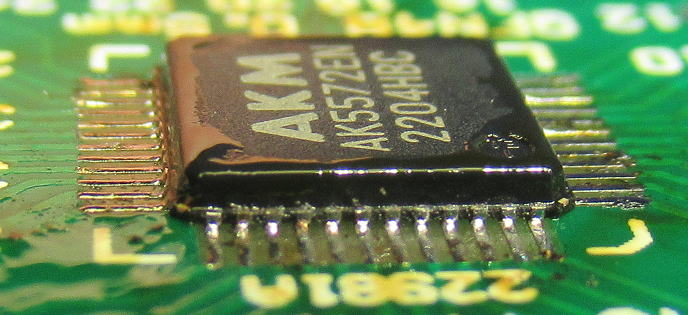

そこで、旭化成に絞っていますが現状のADCのラインアップをみてみました。 中でもスペックが高いのはAK5572,AK5574,AK5578です。

32Bit768kHzのサンプリングでS/Nも121dBあります。ちなみに、型番の末尾の数字はチャンネル数でAK5572が2ch、AK5574が4ch、そして

AK5578が8chです。 まあ、8chのADCなんて使わないだろうな〜。

で、下表をみていて自動車用途のADCがかなりあります。 これってどういった用途なんだろう?

まあ、AMやFMなんかはアナログ信号だから、それのためにADCして、あとはディジタルで音質調整をするということなのかな?

いづれにしても、オーディオ用途のなかでもステレオに限るなら2chのAK5572でいいような気がします。

旭化成のADCのラインアップです。 AK5572,5574,5578あたりがスペックが高いです。 使うなら2chのAK5572でしょうね。

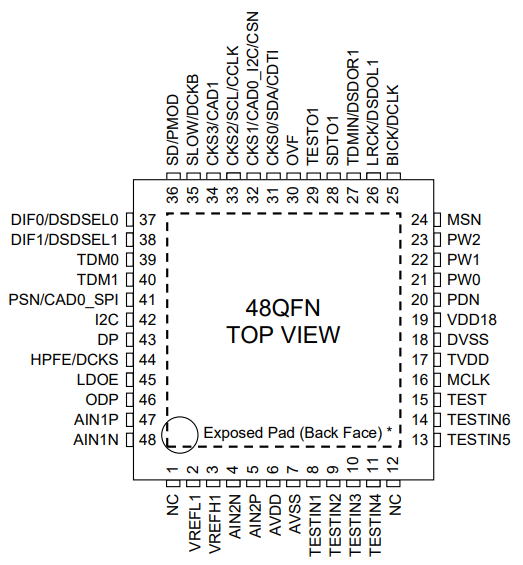

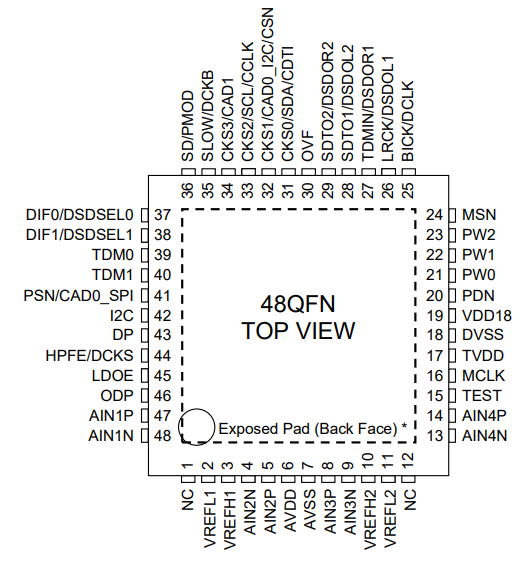

AK5572とAK5574の違いは?

使用するなら、2chのAK5572でいいのでしょう。 DEGIKEYでも@1400円程度と比較的安価です。

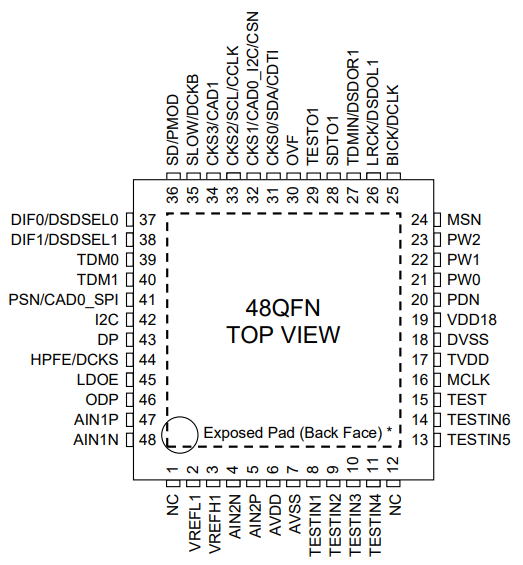

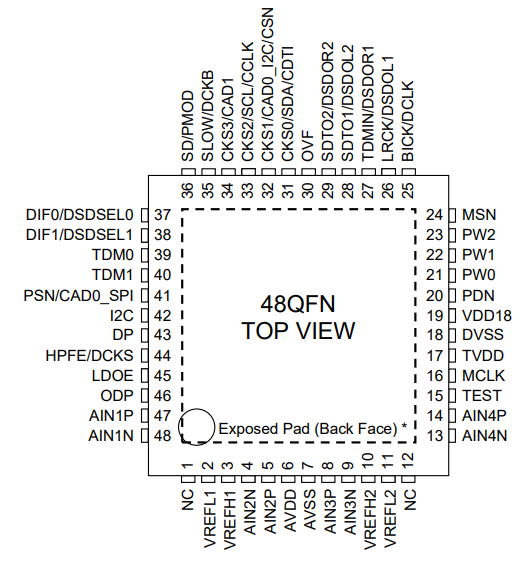

でも、AK5574とパッケージが同じところをみると、ひょっとしてAK5572とAK5574のピン配置は似ているかもしれません。

一度、並べて比較してみましょう。

で、比較してみるとAK5572とAK5574はほぼ同じです。 AK5572のテストピンになっているところがAK5574での電源入力とアナログ入力になっています。

このため、AK5572とAK5572の共用パターンができそうです。

ただ、フロントエンドのアナログ部分が結構面積をとりそうなので、作るなら2ch分のみだけと、AK5574を使えば4chにも拡張可能ということになるでしょう。

| AK5572 |

AK5574

(AK5572のテストピンが電源と入力に割り当てられていて、その他は同じです) |

|

|

めんどうな形状だな〜

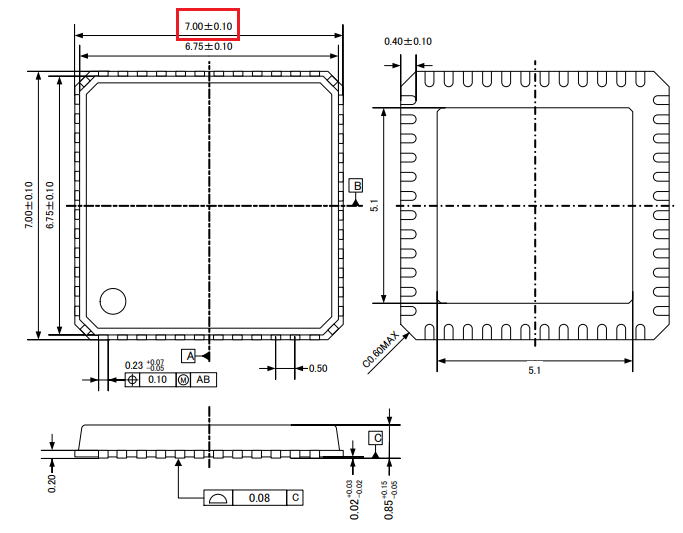

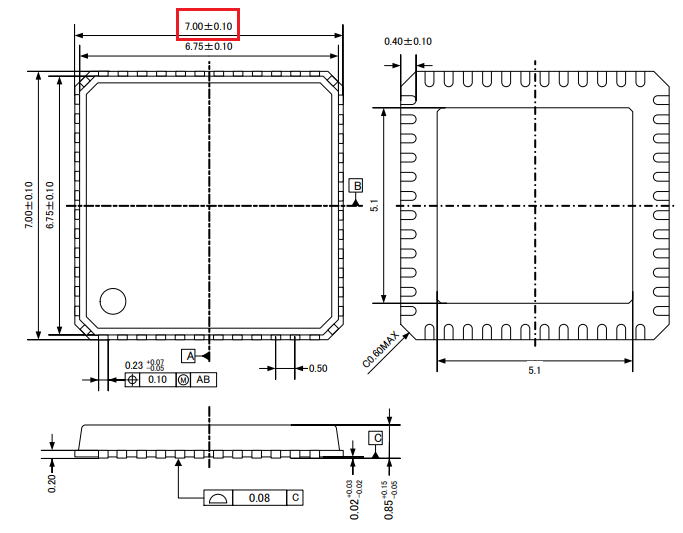

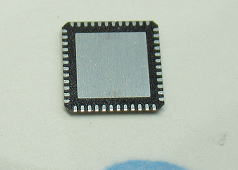

まずはAK5572あるいはAK5574あたりを試してみたくなりましたが、パッケージがHVQFN48です。

また面倒な形状だなあ〜〜、変換基板あるかな?変換基板がなければ、直接基板の設計になっちゃいますが、

それはそれでリスクがかなり高いです。

パッケージはHVQFN48です。外形7mm四方のパッケージです。変換基板があるだろうか?

秋月のQFN48基板は・・・×

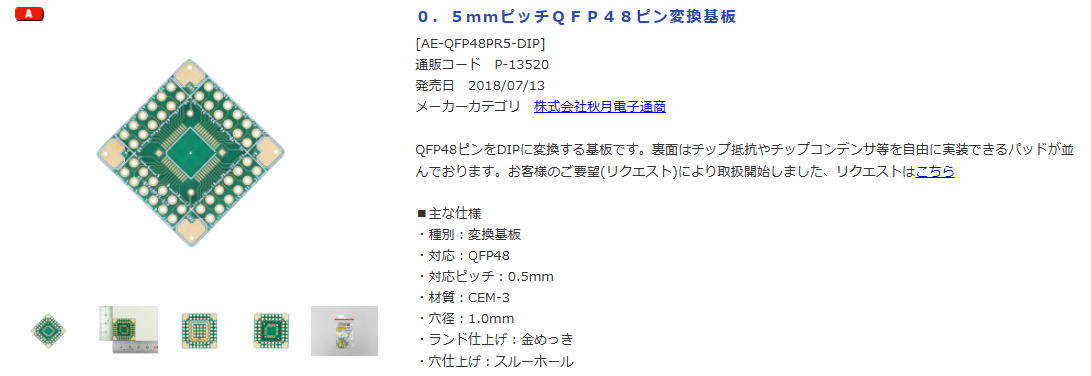

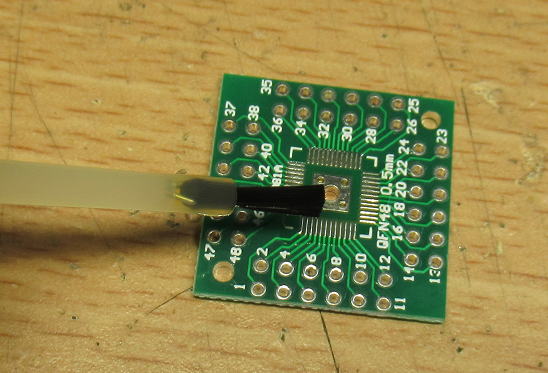

秋月の変換基板を調べてみました。ちょうど0.5mmピッチのQFN48の変換基板があるようです。

EXPOSED PADには対応していませんが、中央に穴をあければ大丈夫です。

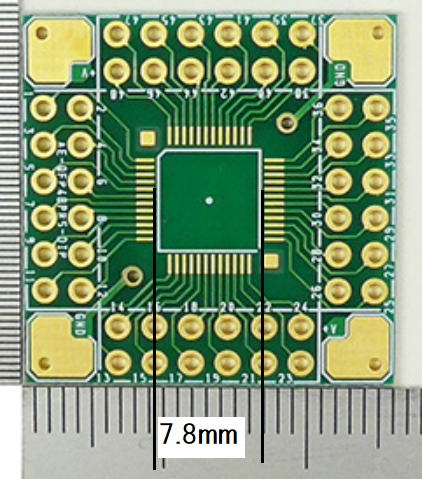

でも、基板をみてすこし対向するパターン間の間隔が広いような〜〜?

計ってみると7.8mmあります。これじゃあ7mmのHVQFNでは届きません。

秋月にQFN48の変換基板がありました。

対向するパターン間の距離が7.8mmと大きいのでHVQFN48では届きません。

これはリードピンのあるパッケージ用でしょう。

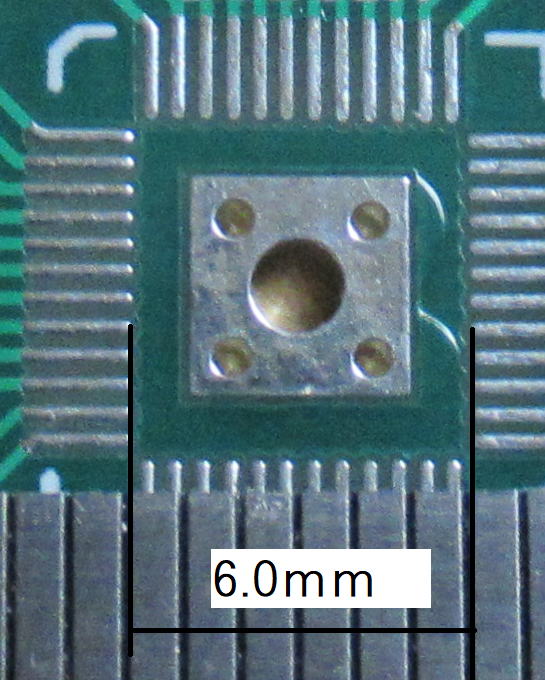

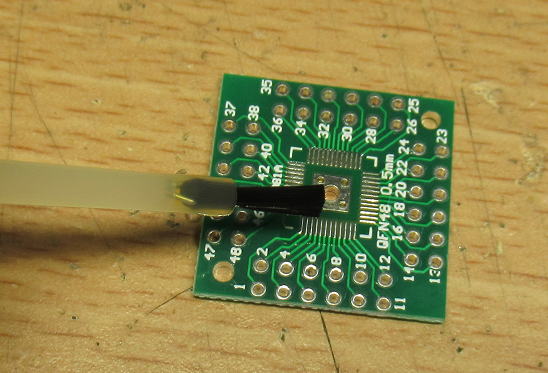

手元にあるかな?・・・・〇!!

秋月の変換基板はだめのようですが、変換基板については色々と買ったりしているので

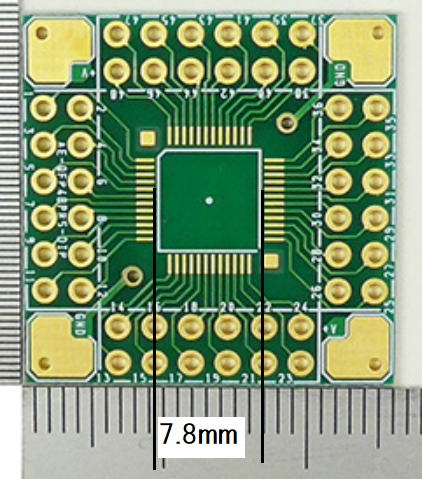

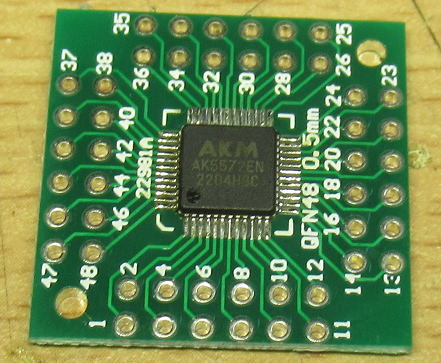

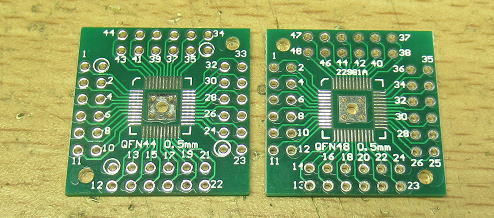

部品箱に転がっているかもしれません。 で、掘り出してみると、使えそうなのがありました。

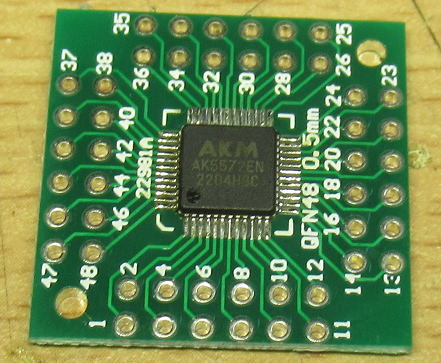

確か、AMAZONで購入した中華製のもののはずですが、両面あってQFN44とQFN48のどちらも

使えるものです。

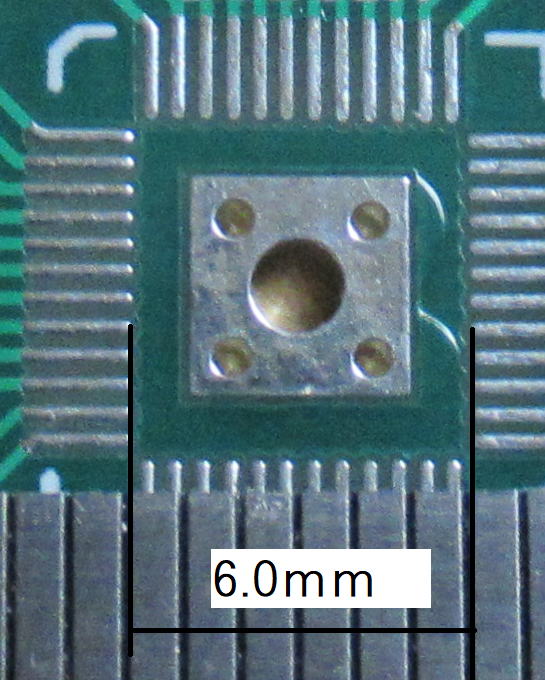

ポイントとなる対向するピン間隔を調べると6mmです。これなら7mm四方のHVQFNが取り付けられます。

さらに、EXPOSED PADのパターンもついているので好適です。

これで、デバイス(AK5572)を買っても動かせそうです。

変換基板がなければ、部品箱の肥やしになってしまいますからね。

こんな変換基板を部品箱で見つけました。

対向するピン間隔が6mmなので7mm四方のHVQFNなら取り付けられそうです。

変換基板もあったことなので、折をみてチップを買ってみましょう。

まずはとりかかり中のパワーアンプが待っています(笑。

それでもブツはやってくる 2023.2.11

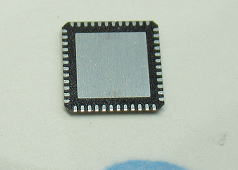

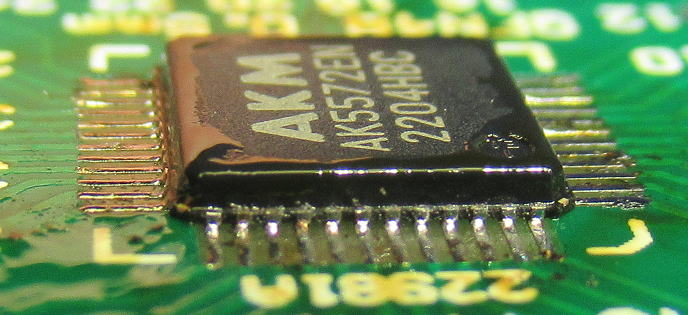

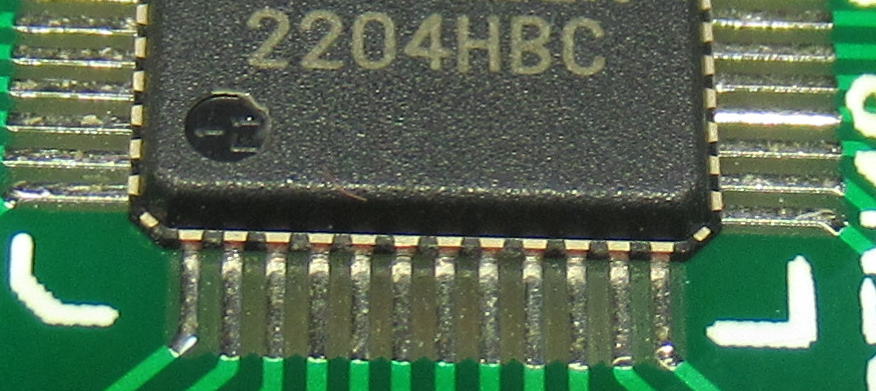

DIGIKEYでの買い物ついでも1個だけAK5572を買ってみました.

やっぱり小さいな〜.

裏面はこんな感じ.

このままだと無くしそうなので、とりあえず変換基板に取り付けておきましょう.

ちょっとHOW TOちっくに書いてみました. 私なりのやり方です.

1)まずは変換基板にフラクスを塗ってすこし乾かします. 粘度がでてICが動きにくくなります.

2)ICを置いて位置合わせです.4方向からルーペで確認して、ずれがないように微調整です.

ここがもっとも大切です. ここで手を抜けば取り返しがつきません.

3)1,2箇所を半田付け. このときコテ先や半田がICに触れないように、 ICは軽いので簡単に

動いてしまいます. 触らないようにして半田を多目でもよいのでパターン端から流し込むような形で

1,2箇所接続します.

4)対角で2箇所半田付けできたら、あとはICは動きませんから、周囲を半田付けです.

半田付けが終わったら、まずはルーペで半田がちゃんとついているか確認です. これ大事です.

ブリッジしている箇所は再度フラクスを塗ってコテを当てれば、表面張力で半田ブリッジが解消します.

5)汚くなったフラクスをアルコールをしみこませた綿棒で清掃してれば、変換基板への取り付け完了です.

しばらくアンプ作りに注力していたこともあり、ひさしぶりに作業再開です。

ハードウエアモードで動かしましょう! 2023.3.23

ADCはインピーダンスの高い状態での入力信号を扱うことから、マイコンはない方がいいのと、

一番お気楽に動かすことができるのでハードウエアモードで動かします。

というか、DAC素子なんかはマイコン使用を前提で動かこすことが当たり前になっていますが、

ADCについてはマイコンレスで動くような設定がかならずあるような気がします。

メーカとしても、ベストな性能を出すためにはマイコンは避けたいという思惑もあるのでしょう。

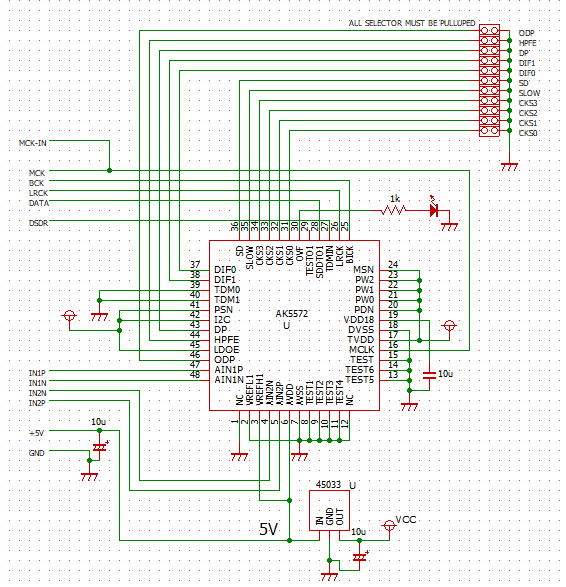

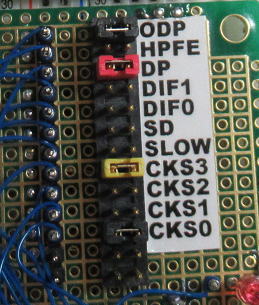

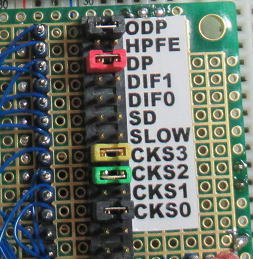

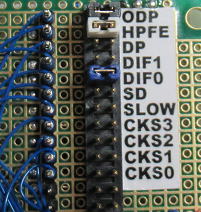

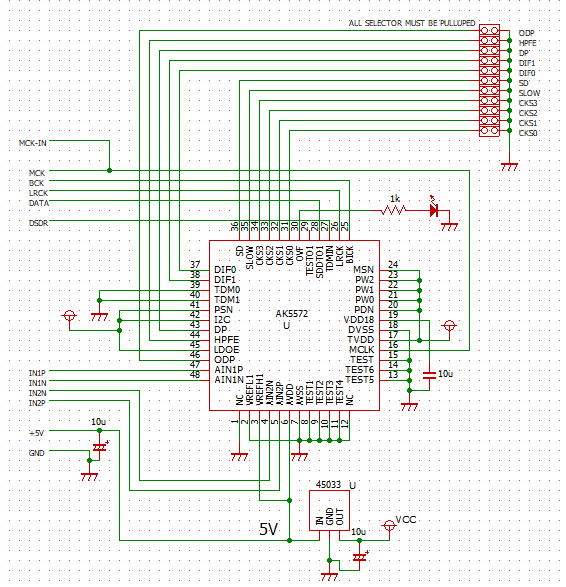

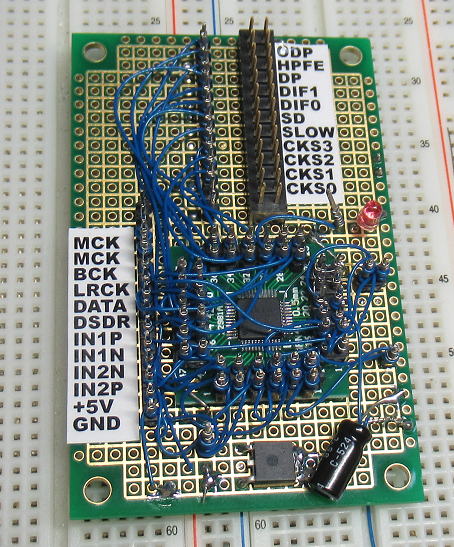

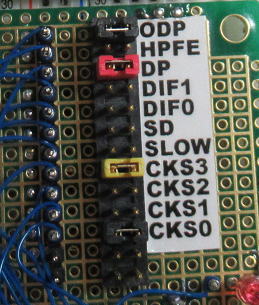

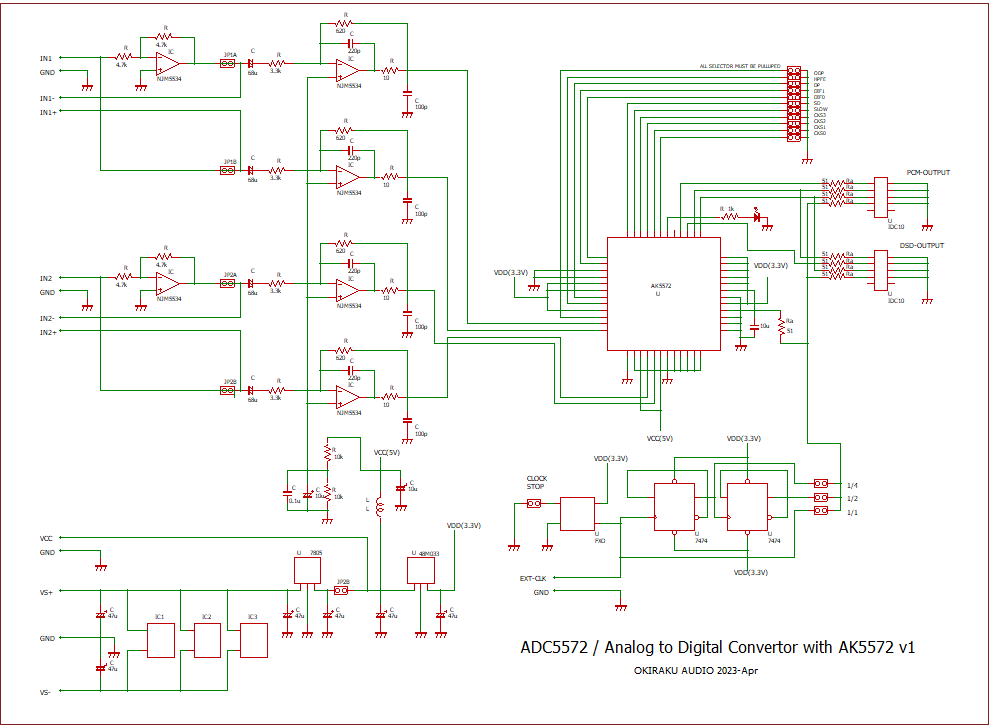

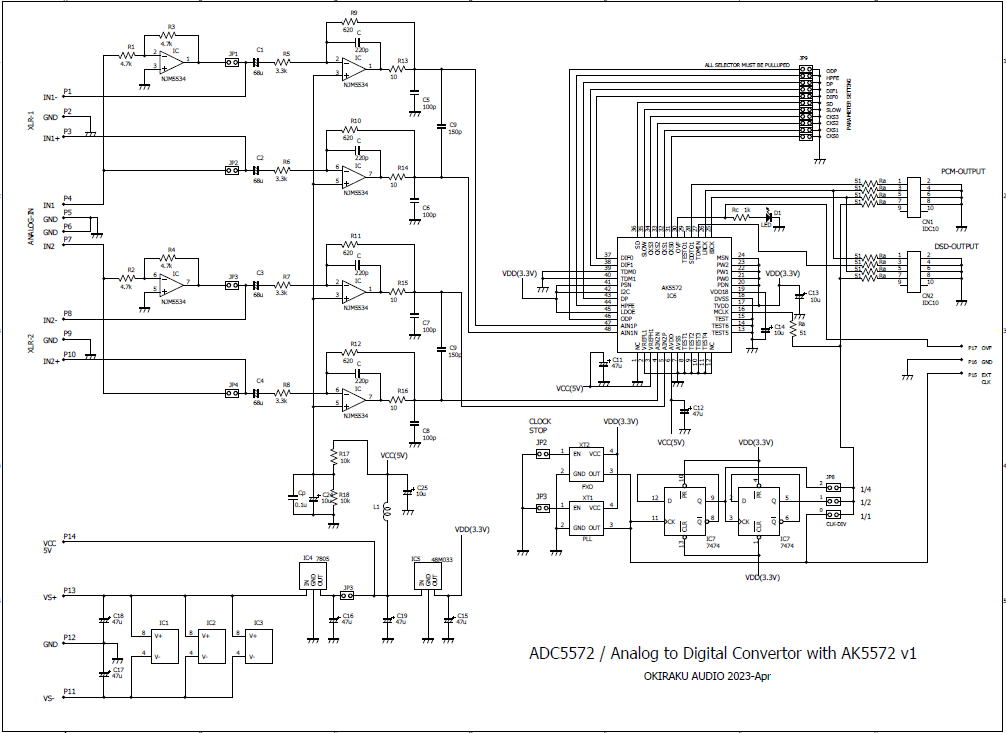

さて、ハードウエアモード(パラレルモード)で動かすためのモージュールを作っていきましょう。

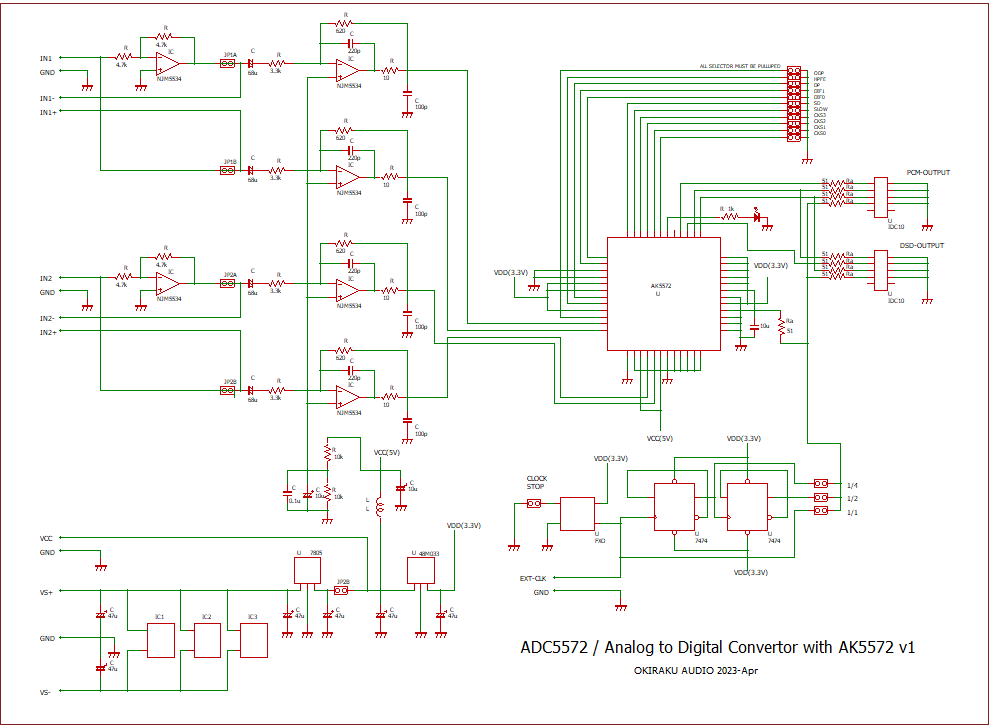

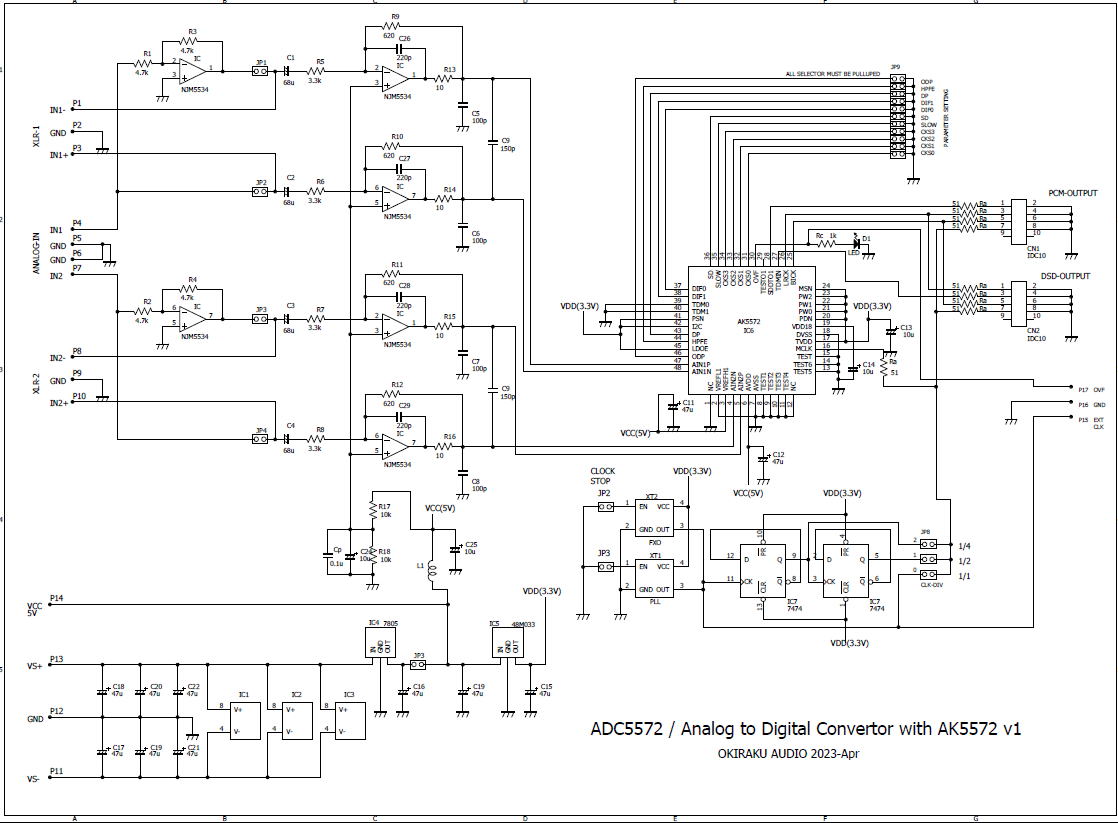

まずは回路図を描いておきます。ハードウエアモードなのでジャンパー設定が沢山あります。

なお、コア電圧の1.8VについてはAK5572内部のLDOを使うことにします。

回路図の作成が終われば、おもむろに作成です。

できるだけ半田付けを少なくして、楽しようとラッピングを使いました。

が、実際にはポリウレタン被覆銅線をつかった方が早かったかもしれません。

というのもラッピングだと、1回の配線で2ピン間の配線しかできませんが、

ポリウレタン被覆銅線をつかえば、隣接するピンなら一気に複数が配線できますから。

まあ、途中で変更するのもなんなんで、今回は再最後までラッピングで配線しましょう。

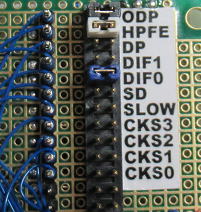

ハードウエアモードで動かすためのAK5572のモジュール部の回路図です。

ラッピングで配線です。ジャンパーポストにはラベルを付けておきました。

動かしてみましょう!

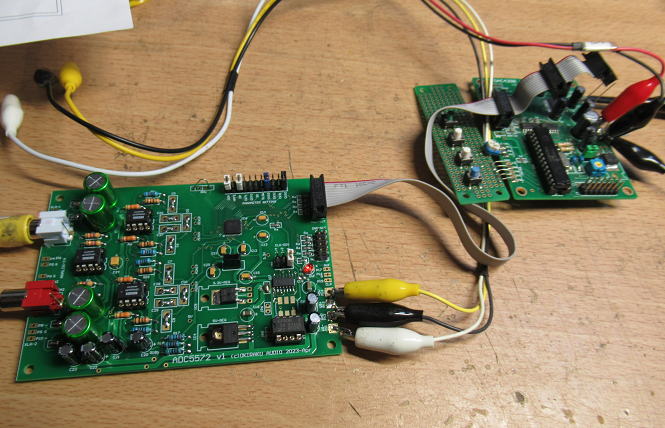

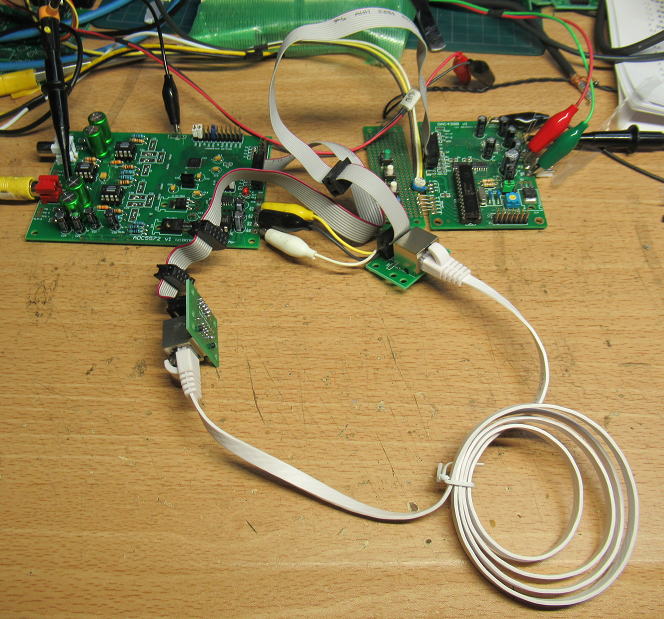

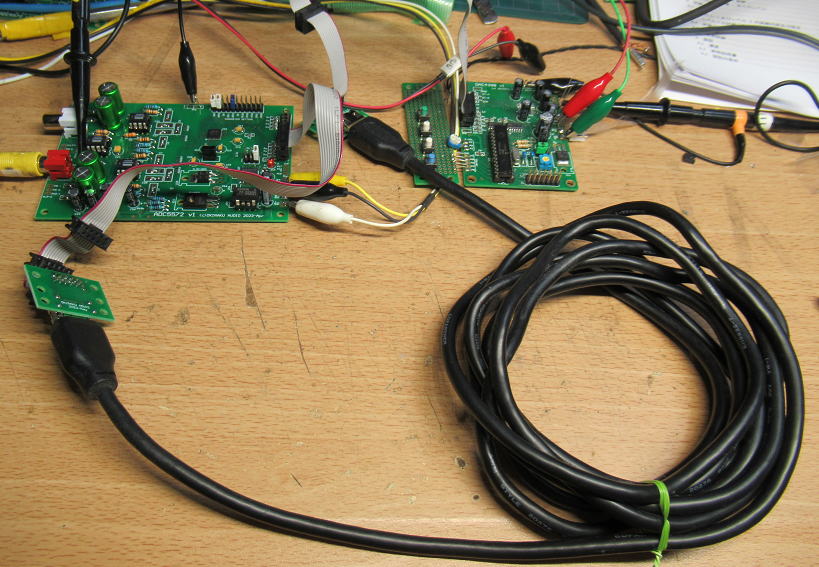

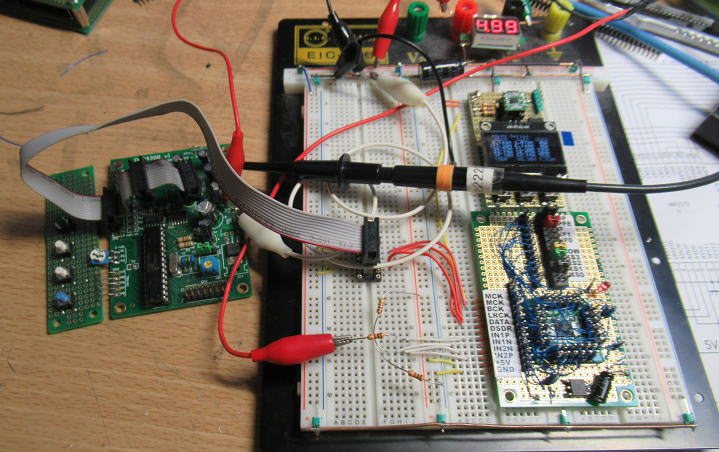

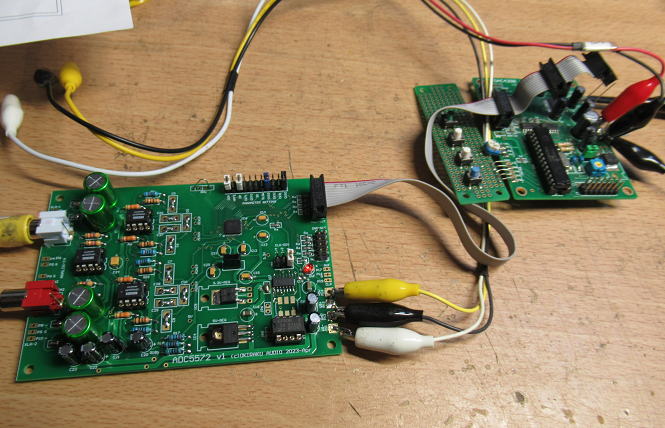

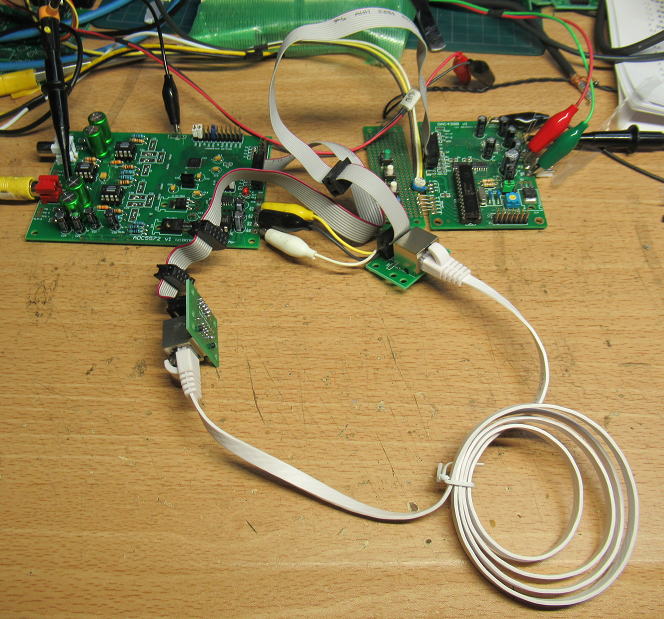

ADCの動作確認のために、変換出力をDACに繋ぐ必要があります。

そこでDACには手元にあったDAC4398をつかいました。

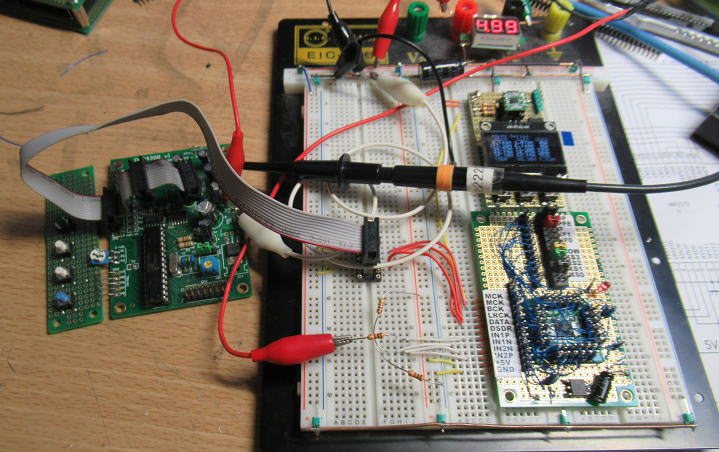

ADCのクロックについては、このテストの為に作成したSi5351Aをつかったオーディオ用のクロック発振器をつかいました。

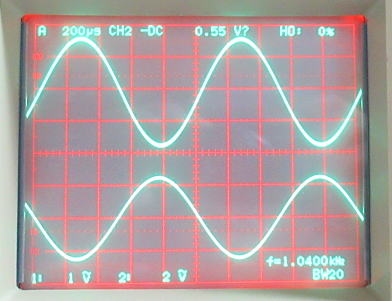

テストの状況です。

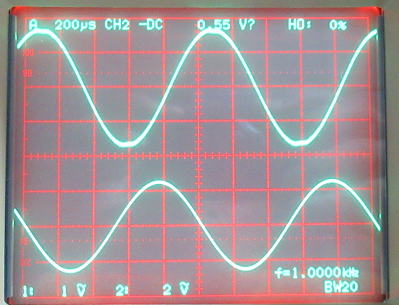

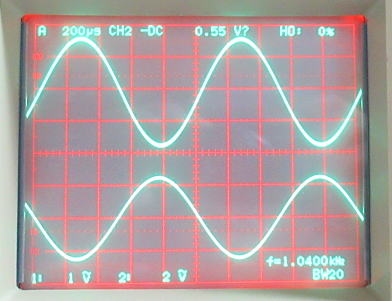

最初はPCMモード

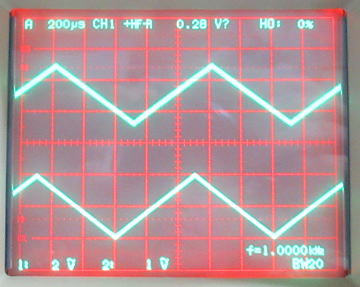

まずはPCMモードでテストです。

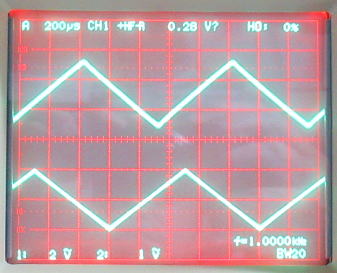

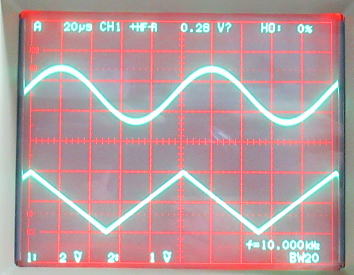

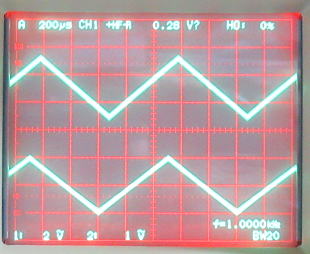

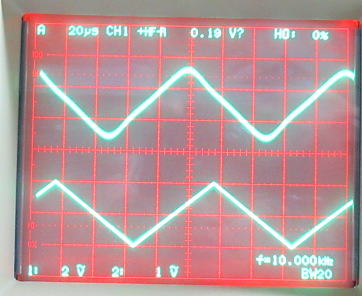

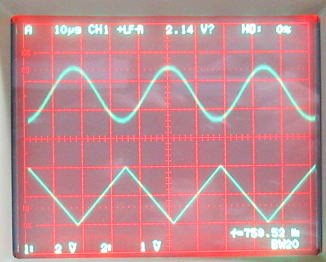

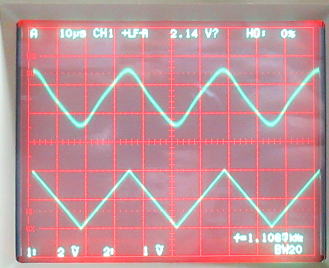

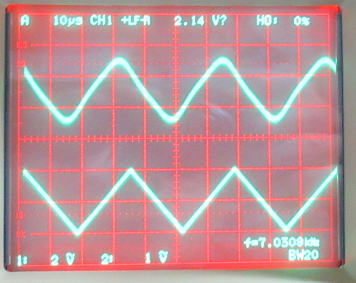

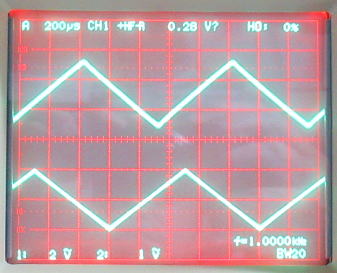

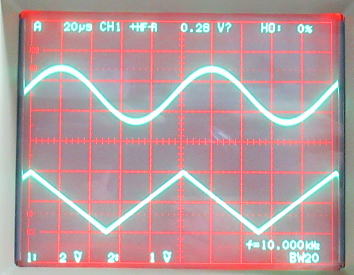

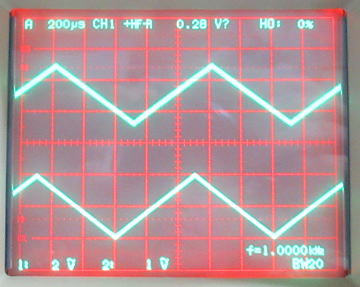

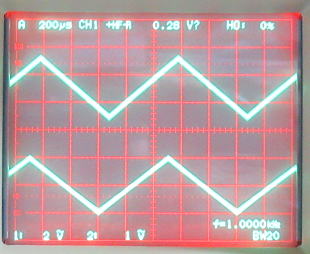

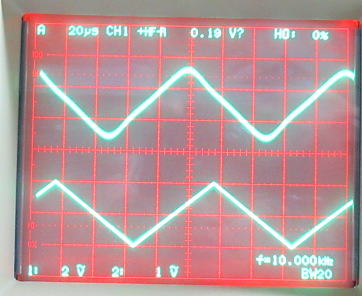

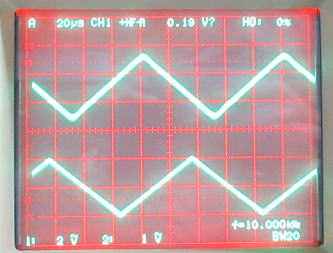

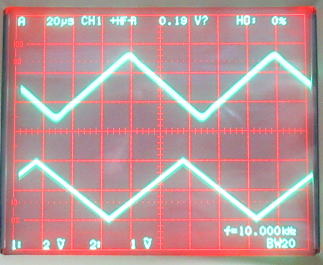

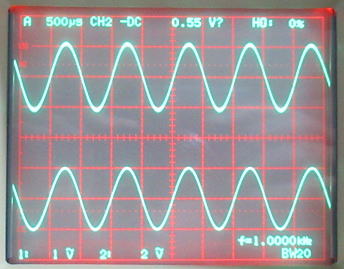

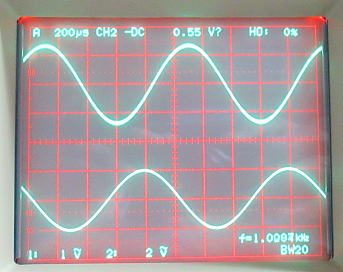

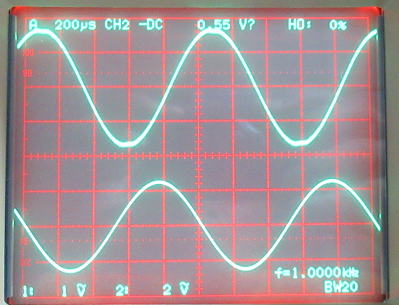

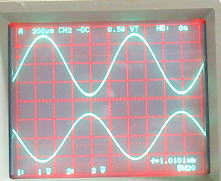

変換状況をみるために、1kHzと10kHzの三角波を入力して、DACからの出力を観察です。

そしてサンプル周波数を変化させたときの波形の変化をみてみました。

結果は想像通りです。

1kHz程度の低い周波数だと、サンプル周波数の違いはほとんどわかりませんが、

10kHz程度になると、サンプル周波数が高いほど波形の再現性が向上することがわかります。

| サンプル速度 |

設定 |

1kHz三角波

上:DAC出力(ADC変換後)

下:ADC入力 |

10kHz三角波

上:DAC出力(ADC変換後)

下:ADC入力 |

NORMAL SPEED

48kHz

(MCK=24.576MHZ) |

|

|

DAC変換後の出力が鈍ってしまって、正弦波のようになっています。 |

DOUBLE SPEED

96kHz

(MCK=24.576MHZ) |

|

|

DAC変換後の出力はすこしは三角波に近くなりました。 |

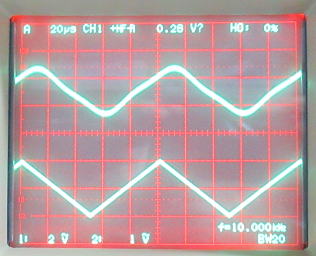

QUAD SPEED

192kHz

(MCK=24.576MHZ) |

|

|

DAC変換後の出力の再現性がかなりあがりました。 |

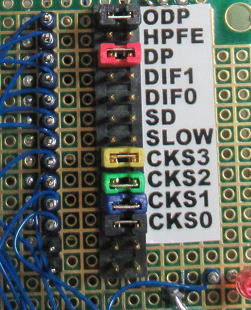

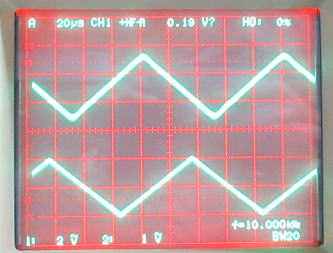

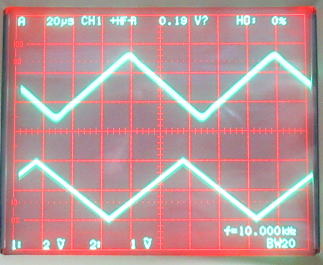

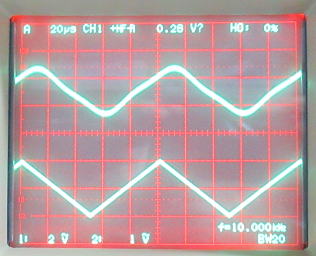

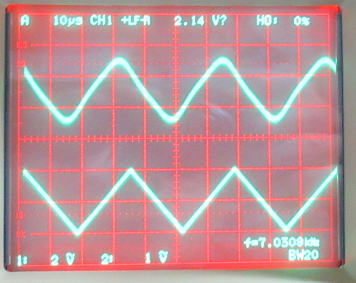

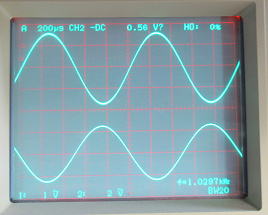

次はDSDで

DSDの設定はDPピンを”H”レベルに変更です.

PCMではフォーマット選択ピンであるDIF0,1がDSDではDSDSEL0,1に変ってサンプル周波数の変更になります.

DCKS(PCMではHPFE)ピンでMSK周波数を512FSあるいは768FSの選択が可能ですが、一般には512FSでしょうから”L”に設定です.

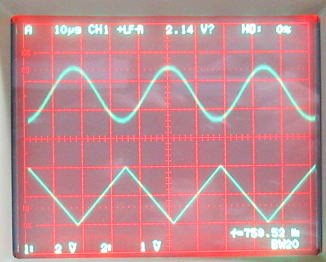

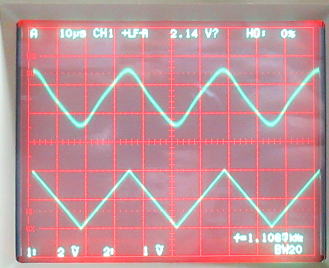

で、DSD64(2.8224MHz)、DSD128(5.6448MHz)、DSD256(11.2896MHz)で変更してみました.

最初は10kHzの三角波で観察してみました.DSD64に比べるとDSD256の方が角の部分がよりシャープになったような感じですが、

差はあまり感じないです. ひょっとして周波数が低いのかもしれません.

追加で20kHz三角波で比べてみました.DSD64とDSD128の違いは明確なのですが、DSD128とDSD256の違いはよくわからなかったです.

もうちょっと周波数の高いところだと違うのかもしれませんが、このあたりの違いがでる周波数成分なんて可聴域をはるかに超えていますから、

どうでもいいような気もしてきました(単に面倒くさい?

| FS MODE |

設定 |

10kHz三角波

上:DAC出力(ADC変換後)

下:ADC入力 |

20kHz三角波

上:DAC出力(ADC変換後)

下:ADC入力 |

64FS

DSD64

(BCK=2.8224MHz) |

|

|

|

128FS

DSD128

(BCK=5.6448MHz) |

|

DSD64に比べるとすこし波形が先鋭になりました. |

DSD64とは明らかに違います. |

256FS

DSD256

(BCK=11.2896MHz) |

|

DSD128と変りないのかな? |

DSD64に比べると波形が先鋭になりました. |

さて、これでPCMとDSDで動作が確認できました.

いやらしいなあ〜

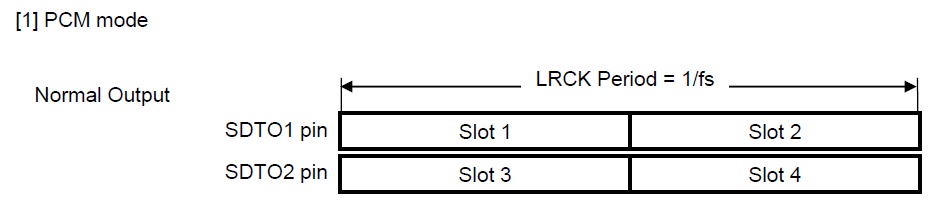

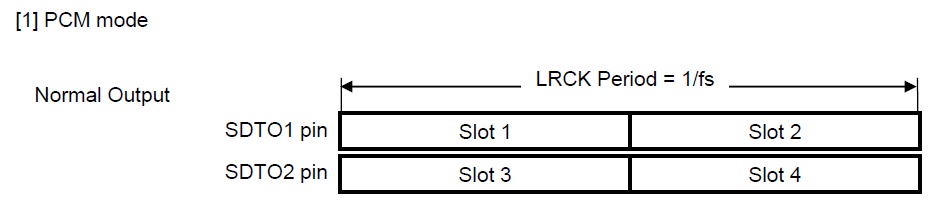

いつもはDACの入力は10PinでPCMとDSDは共用にしています. これができるのは下表の様に、ICのピンが割り当ててあるからです.

| 多くのDACの入力ピン |

PCM入力時 |

DSD入力時 |

|

| MCK |

MCK |

MCK |

|

| BCK |

BCK |

BCK |

|

| LRCK/DSD-R |

LRCK |

DSD-R |

多くのDACのLRCK入力はDSDD-Rと同じになっている |

| DATA/DSD-L |

DATA |

DSD-L |

多くのDACのDATA入力はDSDD-Lと同じになっている |

しかしながら、AK5572の出力ピンはMCKとBCKピンはPCMとDSDと共通ですが、

その他の割り当てが、少々異なっています..

| AK5572の出力ピン |

PCM出力時 |

DSD出力時 |

|

| MCK |

MCK |

MCK |

|

| BCK |

BCK |

BCK |

|

| LRCK/DSDOL1 |

LRCK |

DSD-L |

|

| DATA |

DATA |

|

|

| DSDOR1 |

(INPUT) |

DSD-R |

|

DACとADCのピンを一致させようとしたら.追加でロジックを組まないといけななあ〜.

PCM出力とDSD出力ポートを個別にすればいいのだけど、なんとなくスマートではありません.

というか、出力ポートを統一するだけなら簡単ですが、DSDとPCMを切り替えると他のジャンパーピンの

設定も同時に変更しないといけないといけません. これらもロジックで切り替えるかな?

ADCなんて設定を変えることってほとんどないから、都度ジャンパーピンでの設定にしちゃうかな?

そうすると部品も少なくスッキリするするしなあ〜.

さてさて、どうしたものか?

#あすからの出張のときにのんびり考えましょう!と思ったら、出張帰ったら資料(原稿)の締め切りが目の前だあ〜

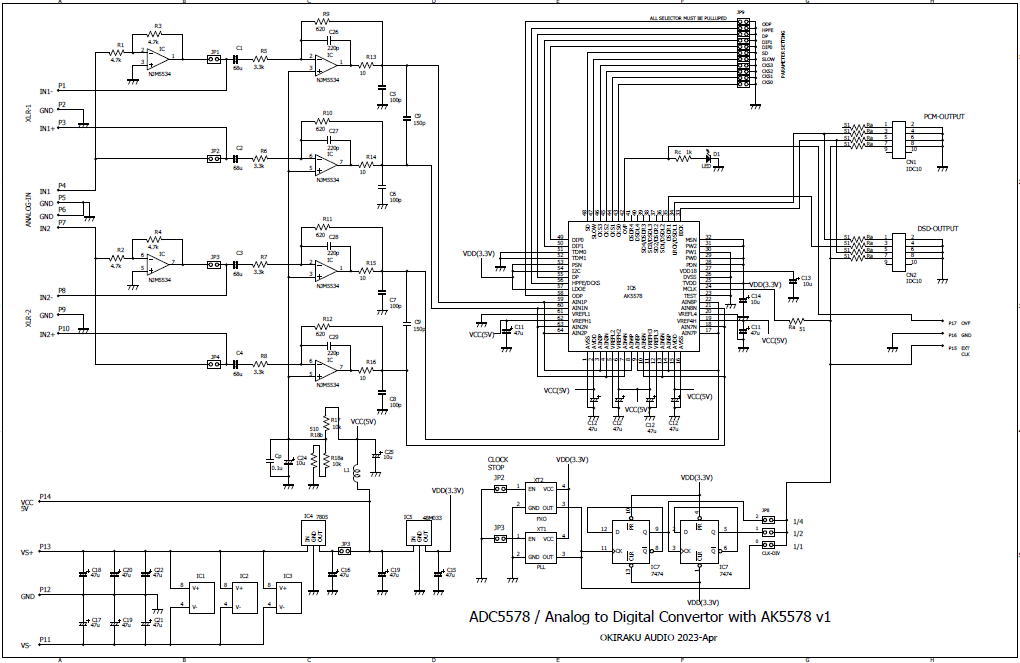

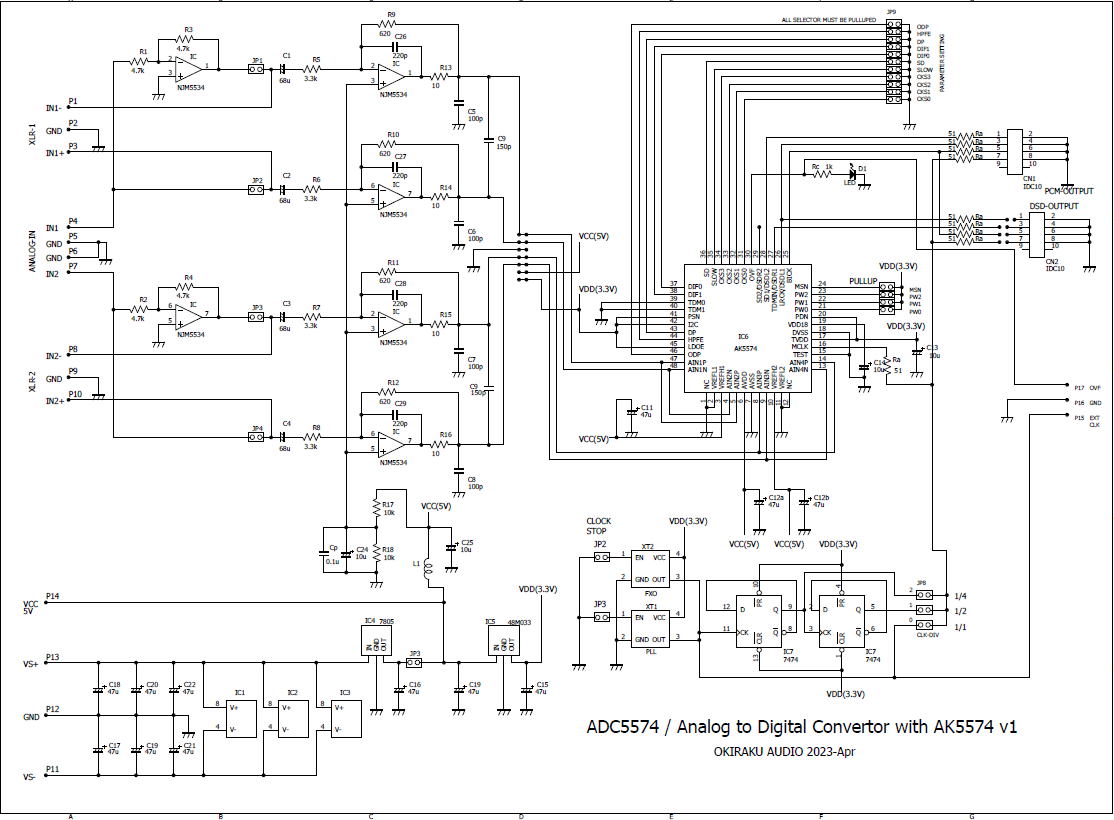

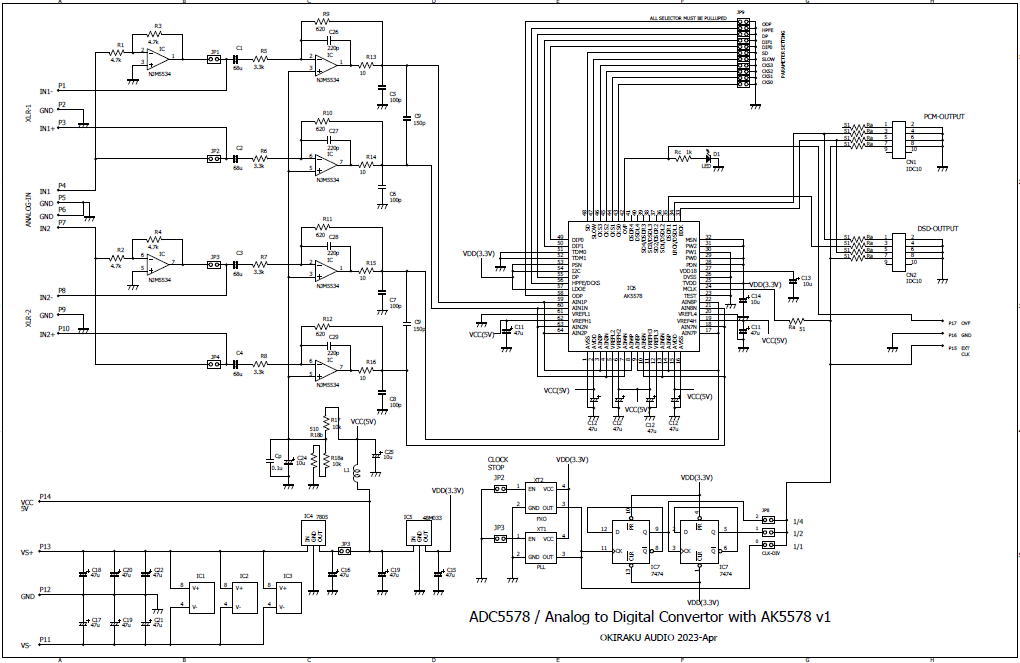

パターンを描いてみましょう 2023.4.26

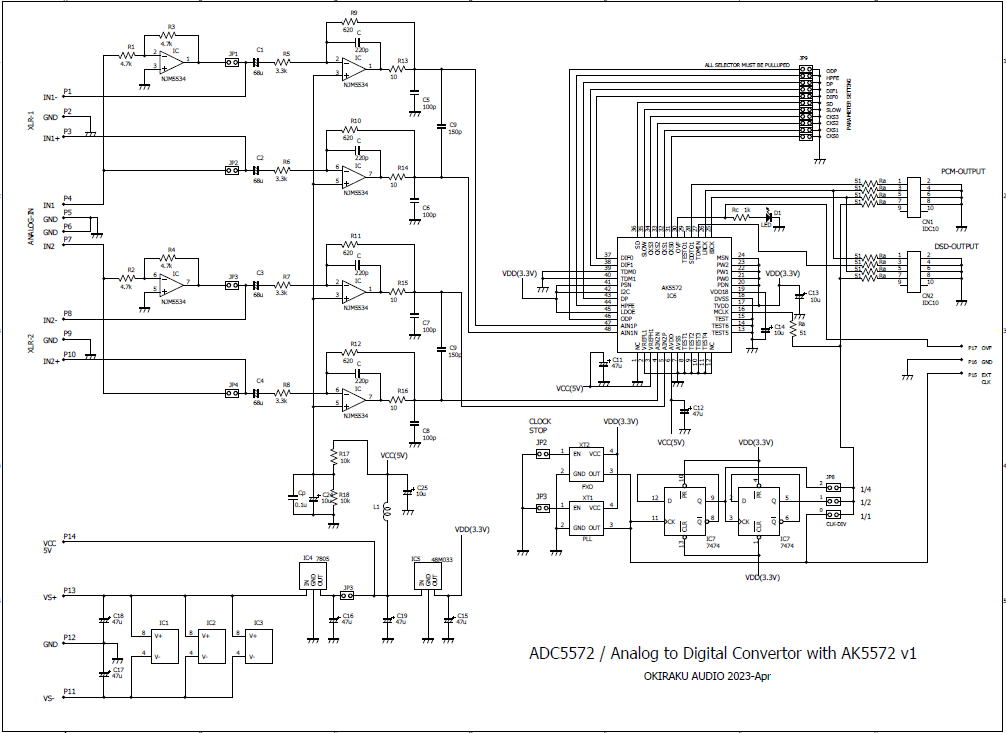

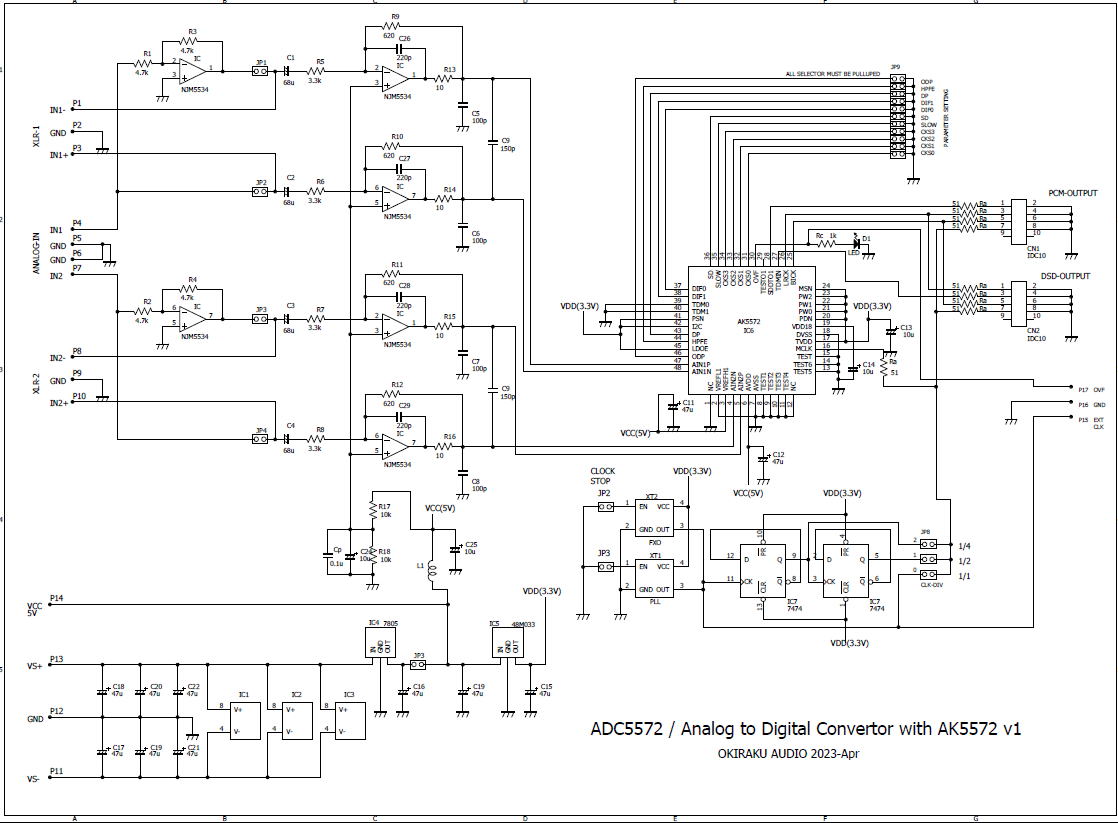

その前に、回路図を作成です。できるだけシンプルに動作させるということで、

・H/Wモードで動作(設定はジャンパーピン)

・PCMとDSDは別出力

・クロックは一系統のみ(但し、外部供給も可能)

・電源は基本は±8〜15V電源の供給(内部で5V,3.3Vを生成。1.8VはAK5572のLDOを使用)

といったところです。

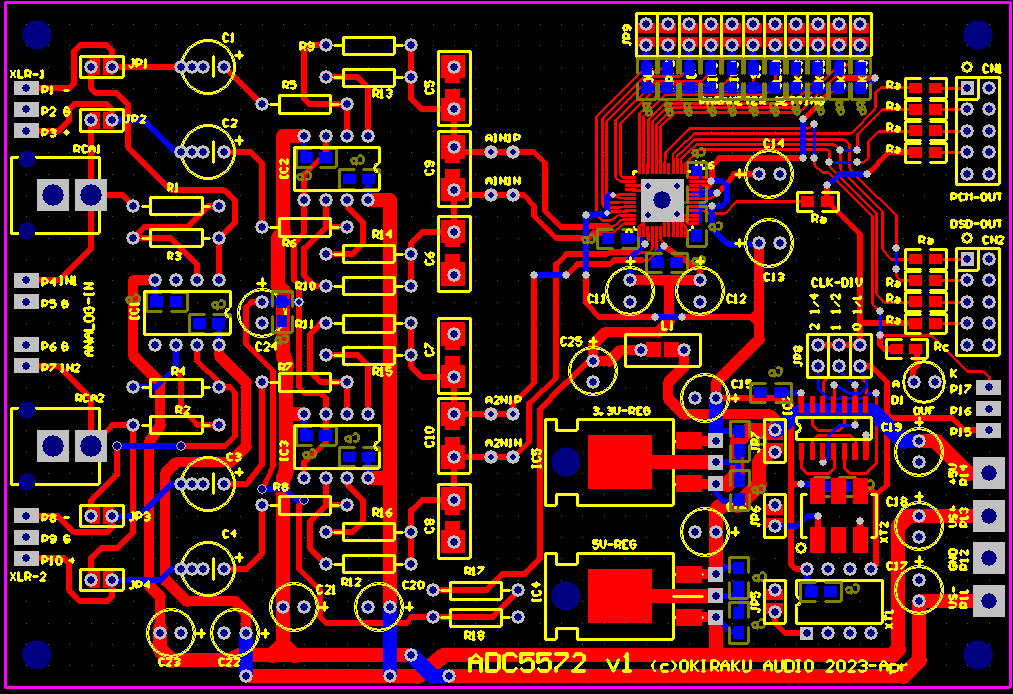

こんな感じかな? 2023.4.26

まずはこんな感じで描いてみました。IC自体が小さいので、

わりとスパースな部品配置です。

まずはこんな感じで描いてみました。

パターンに合わせて回路図も微修正です。

こんな回路になりそうです。

これでチェックしてみて、基板のGNDベタ面を塗りましょう。

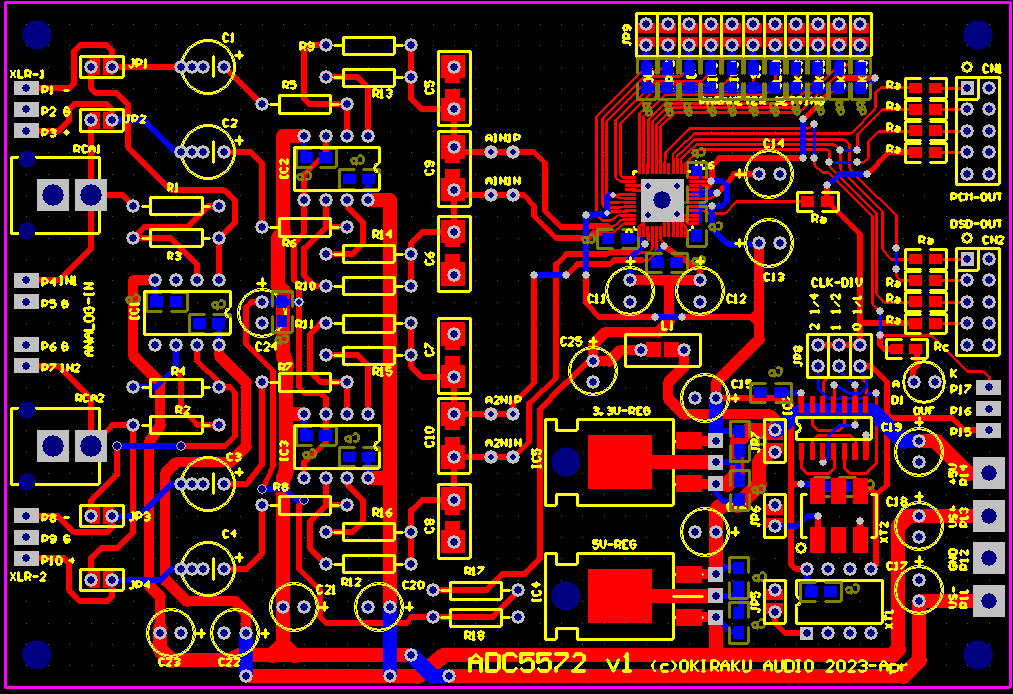

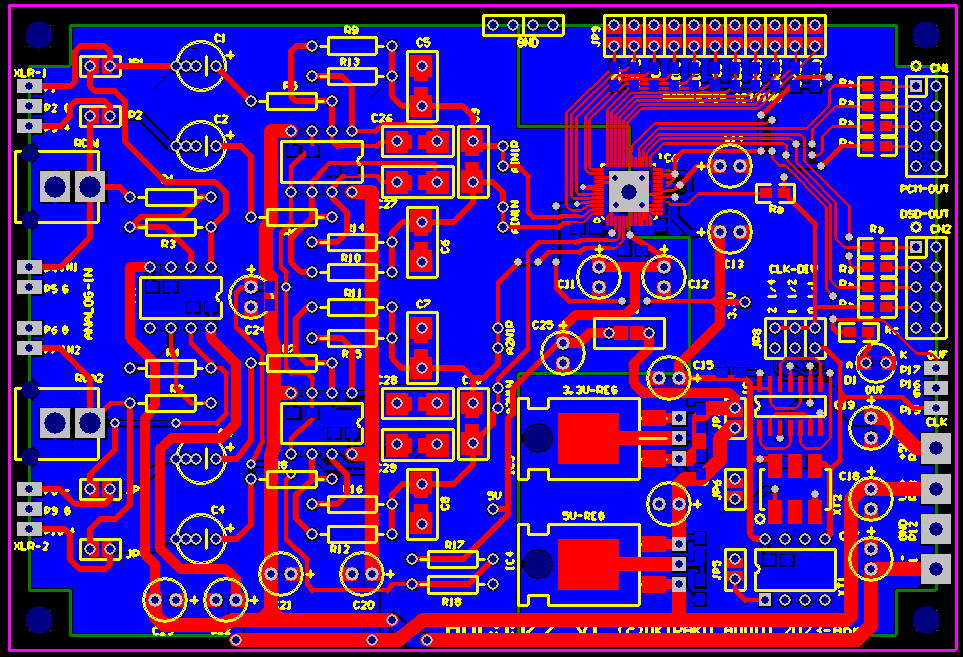

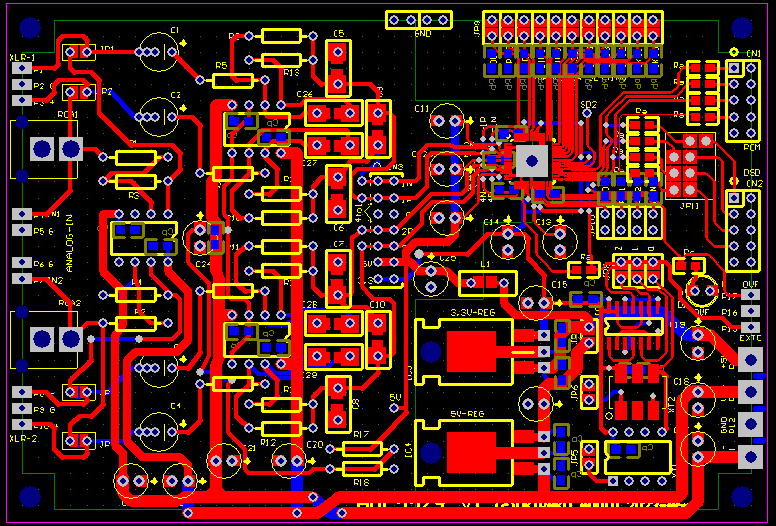

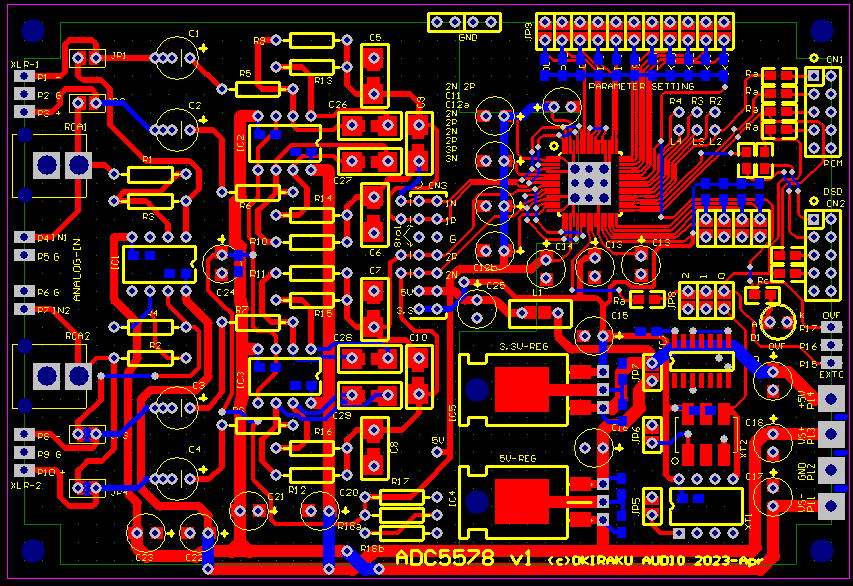

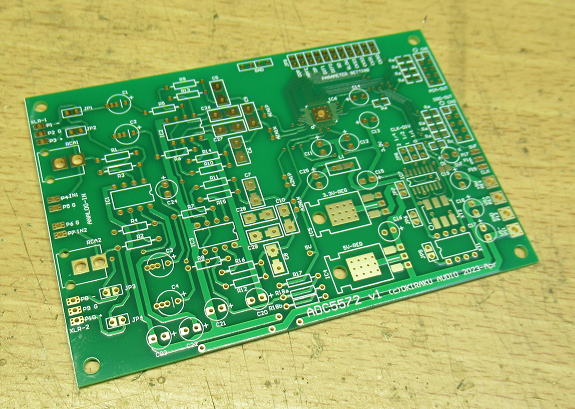

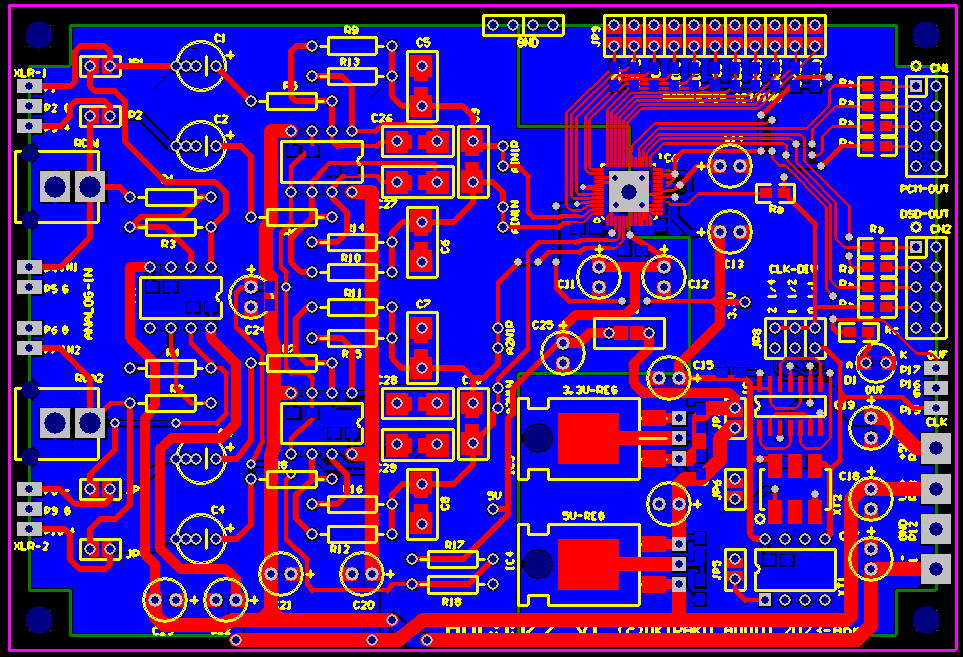

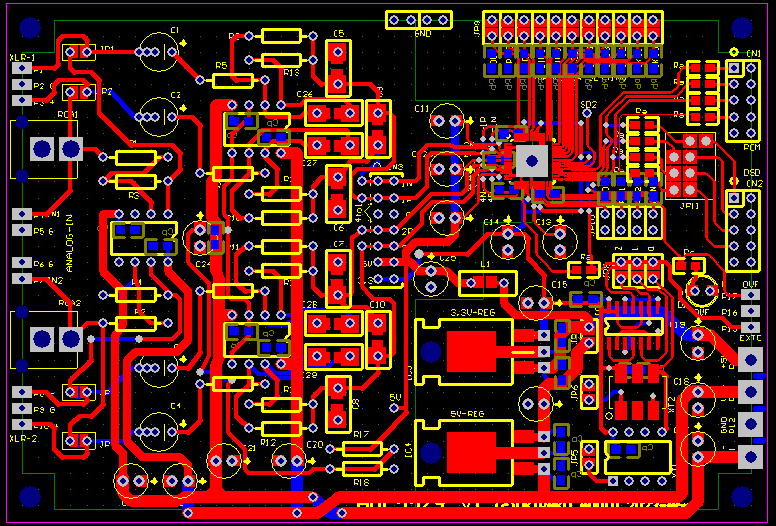

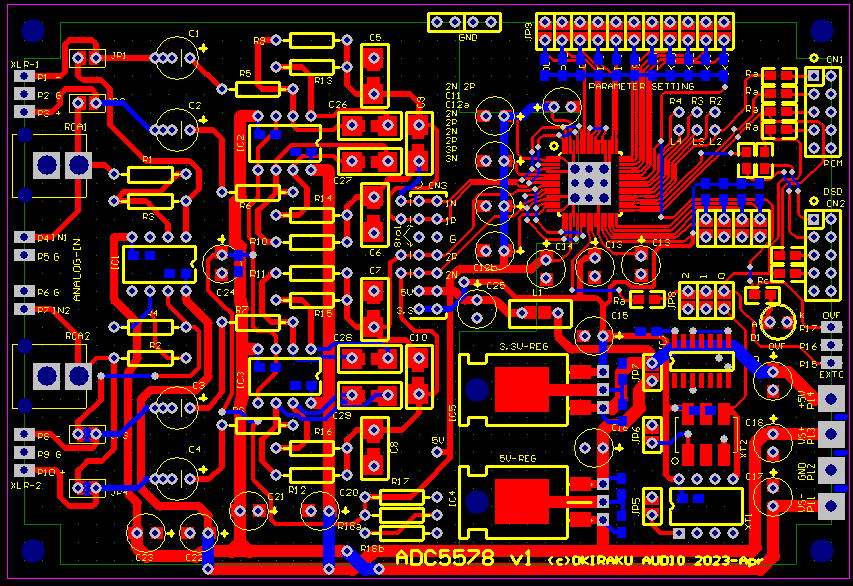

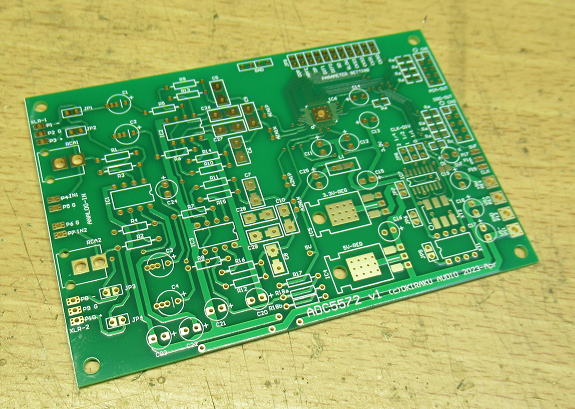

一応、パターン描き完了 2023.4.27

チェックすると色々と抜けていました。OPアンプの位相補償のコンデンサが丸ごと抜けていたりしました(笑。

パターン修正して、GNDベタも描いて完了です。あわせて回路図との部品番号合わせも行っておきます。

パターン描き完了です。

パターンと部品番号もあわせておきます。

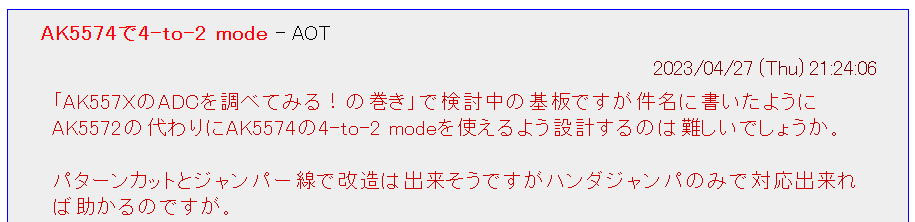

おっと!こんな要望も!!! 2023.4.29

AK557xシリーズの面白いところは、複数のAD変換器をもっていますが、独立して動かせるだけでなく、

並列して動かして、その平均値を出すことができます. たとえばAK5574だと4個のAD変換をもっていますが、

2個に同じ信号を変換させて、平均値を出力することでS/Nが3dB向上します. 一般に平均化による

S/N向上は平均回数の平方根になりますからね.

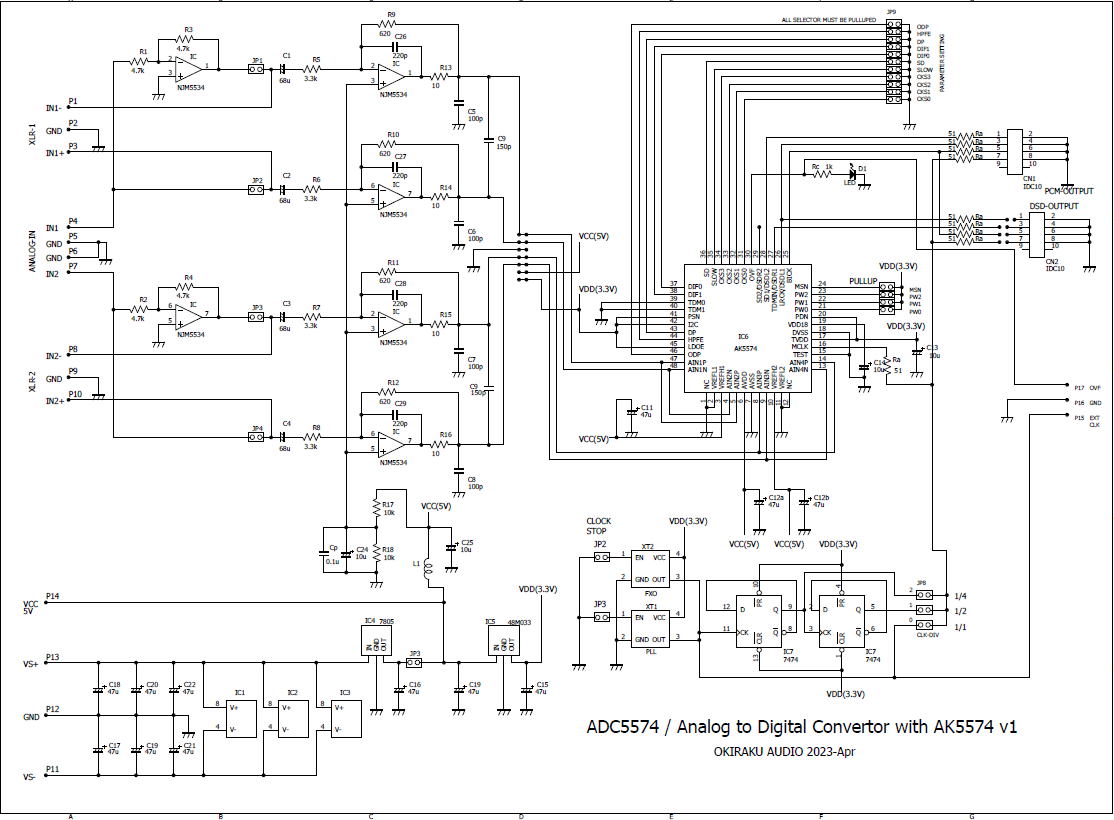

そこで、AK5572だけでなくAK5574もつかえるようにしてAK5574使用時には4to2モードにもできるようにならないかの

提案がありました. 個人的にはAK5572に比べてAK5574はグッと値が張るのであまり触手が動いていなかったのですが、

あらためて価格を見るとAK5572が1421円で、AK5574が2092円ですから1000円弱の違いです. これならば、AK5574が使えるようにしても

面白いかもしれません.

ということで、早速パターンと回路図を書いてみます.

AK5574をつかった場合に4to2モードだけdなく、4to1モードへも対応できるように、すこしパターンを工夫してみました.

AK5574では4to2モードだけでなく4to1モードもありますので、それにも対応できるようにしました.

4to1モードでは基板が2枚必要ですが、アナログ入力部分は1枚だけ必要で、2枚目はディジタル部分のみ実装します.

電源部分も必要ありません.基板の中央にあるコネクタをつかって2枚重ねにしてアナログ信号と電源を共有します.

AK5574での4-to-1モード使用は少々やっかい

AK5574の4to1モードを使うと、4個のADCをつかっての平均値を出しますから、S/Nは1個の場合に比べて倍、すなわち6dBアップします.

方法としては、基板を2枚用意して1枚をマスターモードで使用し、もう1枚をスレーブモードで動作させ、クロックはスレーブから供給してもらいます.

AK5574からの出力はSLOT1のみになってしまいますが、DSDであれば特に問題はないでしょう.

DSDは4to1モドでSLOT1のみの出力になっても、もともとLRの信号線が別なので単純に合わせるだけで済みます.

問題はPCMの場合です. 変換されたデータはSLOT1にしかでません. PCM信号はLRのデータが交互に現われますから、

たとえばRチャンネルのデータは重ねるにはBCKの32クロック分位相をずらせたのちに合成する必要があります.

といっても、単純にシフトレジスタを並べるだけです. 付帯回路もあわせてロジックICが6,7個で済むでしょう.

PCM出力だとSLOT1のみにしかデータが出ないので、LRデータを交互に出すためにはデータをずらす必要があります.

AK5574を2個つかうくらいならAK5578を使えば?

よく考えてみたら、AK5574を4to1モードで動かして、基板2枚にするくらいなら、いっそのことAK5578をつかって8to2モードで動かした方が

早そうです. ちなみにAK5578は1個3339円ですが、AK5574の2個分よりかはだいぶ安いです. それに基板1枚で収まりますし、

ロジック回路なして済みます. ADC4個並列動作でS/Nは127dBもあります.

AK5578になると、パッケージが少し大きくなります. AK5572,AK5574がQFN48に対してAK5578はQFN64です. パッケージとしては

2mmほど大きくなりますが、周りに配置する電解コンデンサも増えますから、搭載できるかな?

一度回路図とパターンを書いてみましょう.

AK5578をつかって回路図を変更してみました.AK5572の回路図を流用です.

AK5578も実装できそうですね. パターンはAK5574をつかったものを流用です.

AK5578をつかった場合でも実装できそうです.

しかし、ここまできたらーーー

AK5578を2個使いのハイエンドADC?

ここまできたら、いっそのことAK5578を2個を8to1モードでつかい、さらにPCM信号の合成回路まで搭載したハイエンドADCを

考えてみたくなります.

しかしなあ〜、当初のAK5572を1個だけだったら1400円ほどですが、AK5578を2個つかってさらにロジックICも加わるとなると

それだけで8000円くらいかかっちゃいそうです. だんだんお財布にとってオキラクでなくなってきます.

それに基板サイズも大きくならざるを得なくなります.

でも、考えるだけなら楽しいですね〜. GWの課題にぴったしです.

ああああ〜 2023.6.26

基板って作るときまでが一番テンションがあがるときのですが、基板の製作には一定の日数がかかることもあり、

その間に興味が他に移ってしまって、いざ基板が納品されてもなかなか着手できないことが多々あります.

そんなところを突っ込まれしまいました(汗

あ、敢て触れなかったのですが、突っ込まれてしまいました(汗。

社会人(?)ってケツを叩かれないと動かないとことがあるのですが、

ようやく動き出しました(笑。

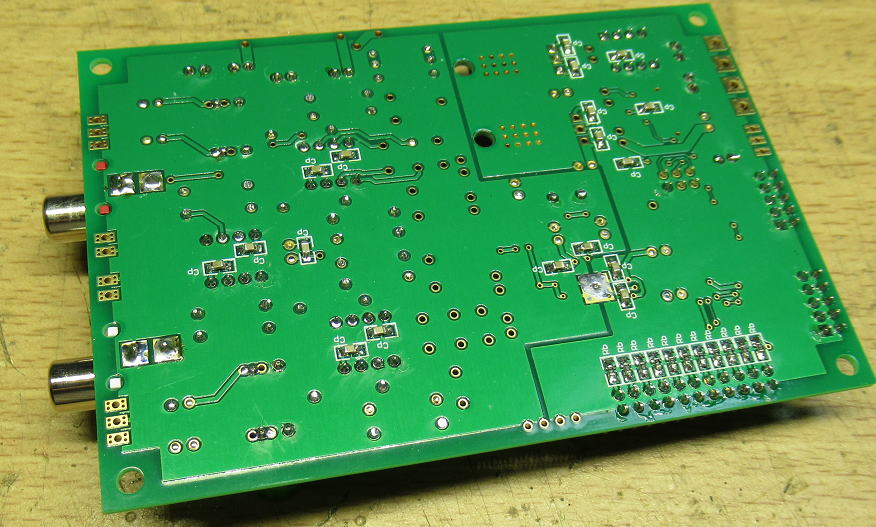

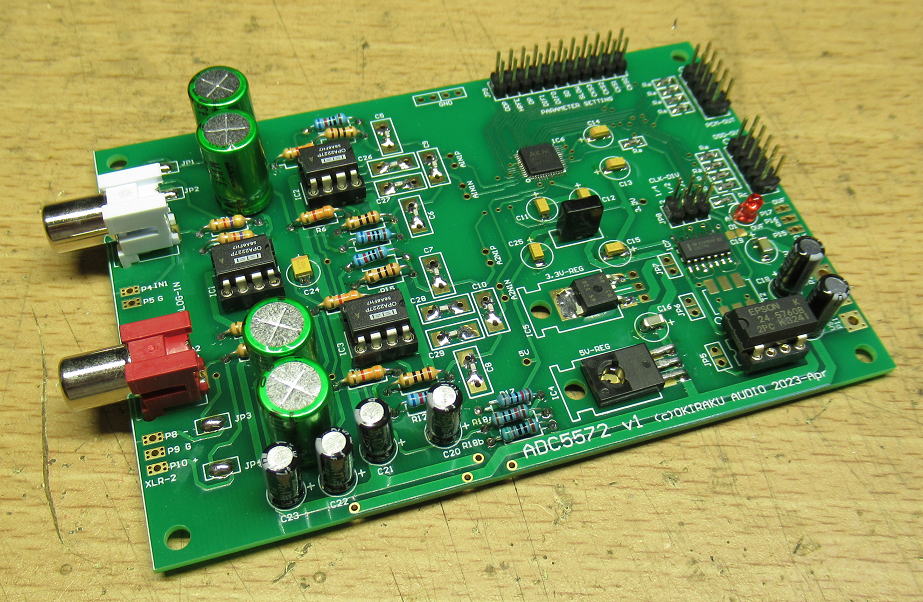

基板は随分前に出来上がっていたのですが----。

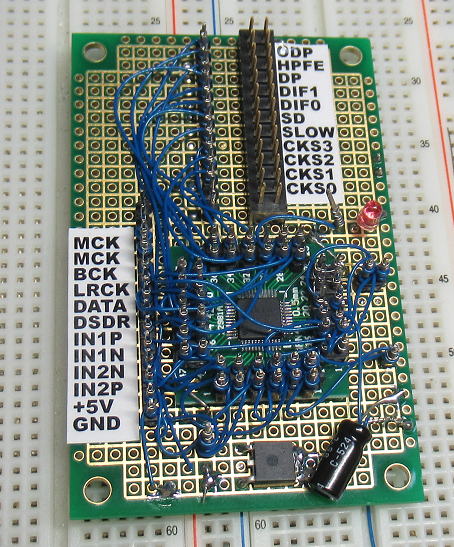

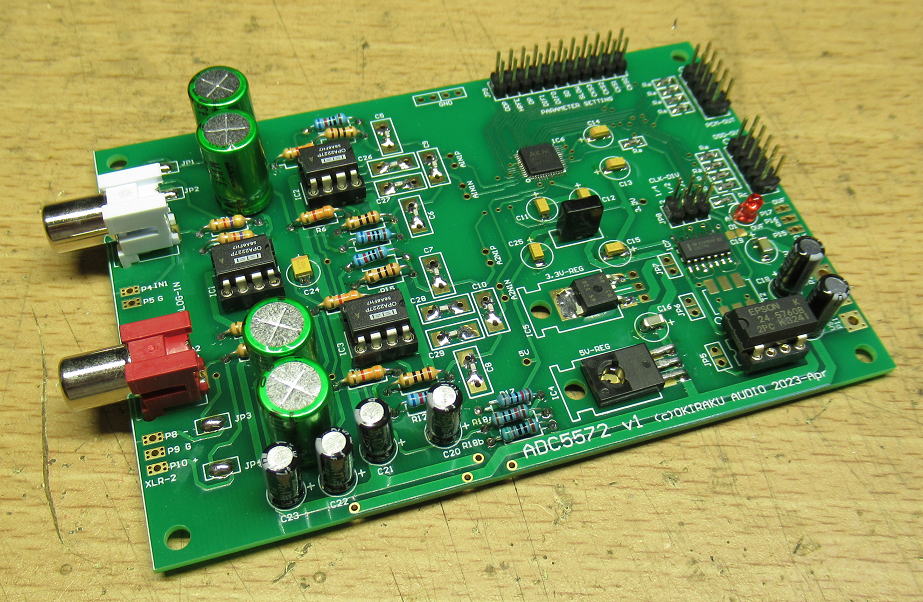

結局ADCに使うデバイスは一番シンプルなAK5572をつかうことにしました.

一気に部品を実装しました。それほど部品点数は多くはありません。

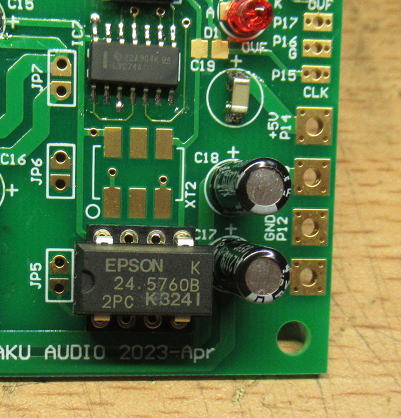

クロックは秋月のPLLの24.576MHz(3,3V動作)を実装しました.

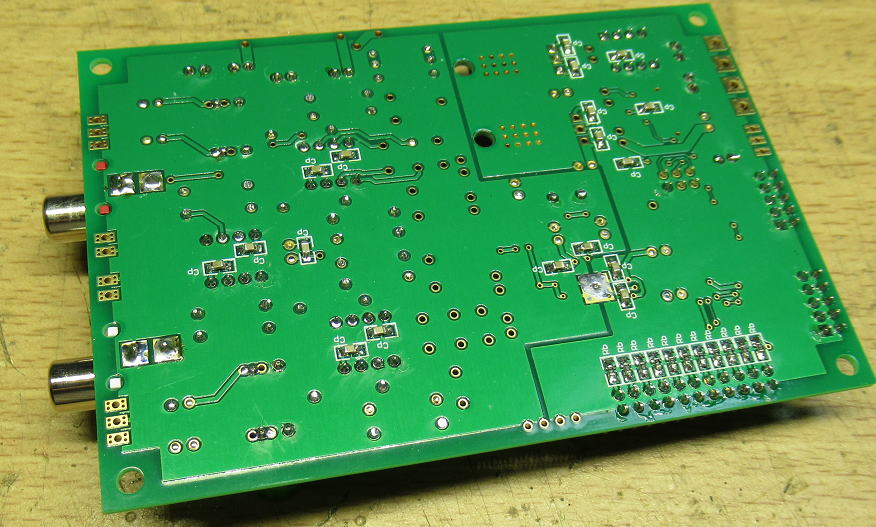

裏面はこんな感じです.

動作確認?

さっそく動作確認しようと思いましたが、今開始してトラブルが発生すると明日に響きそうなので、.

とりあえず後日です.

おもむろに動作確認 2023.7.2

さて、ようやく動作確認にかかりましょう。

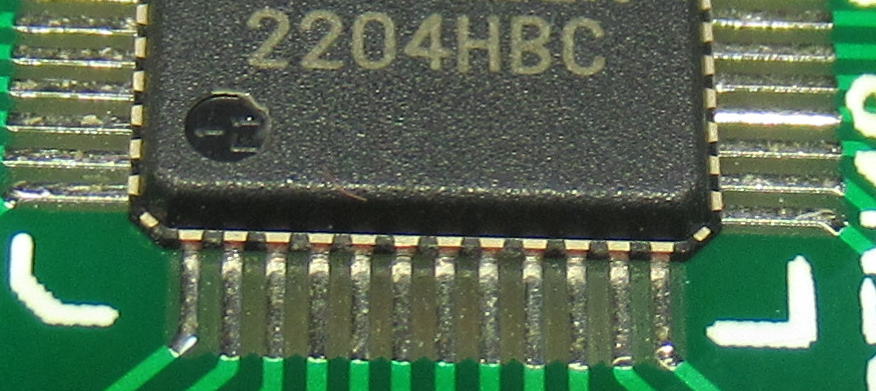

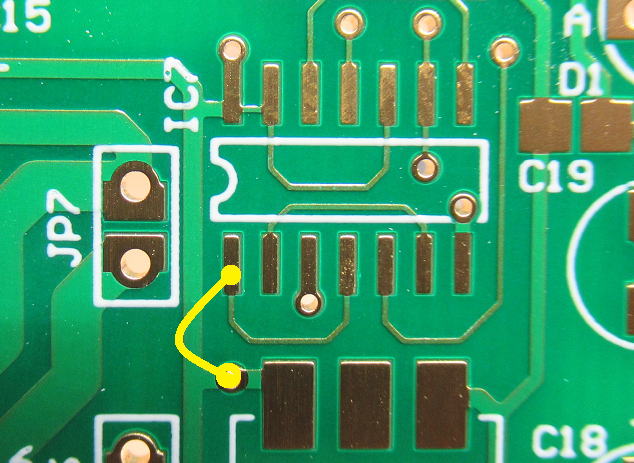

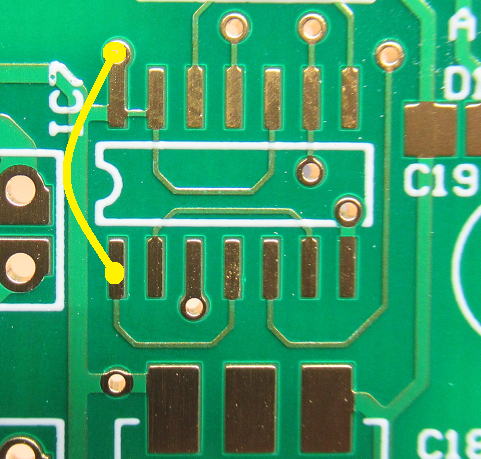

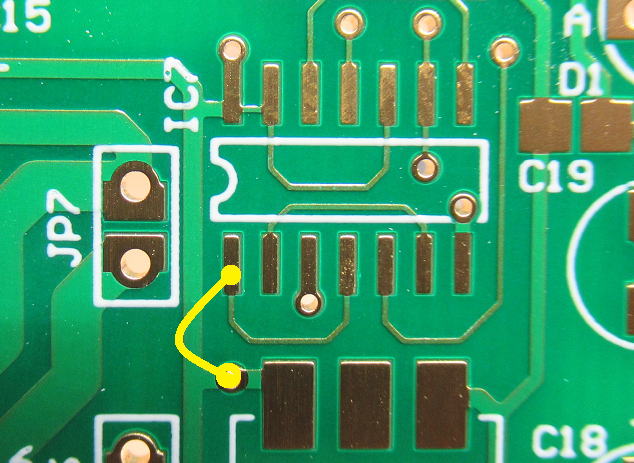

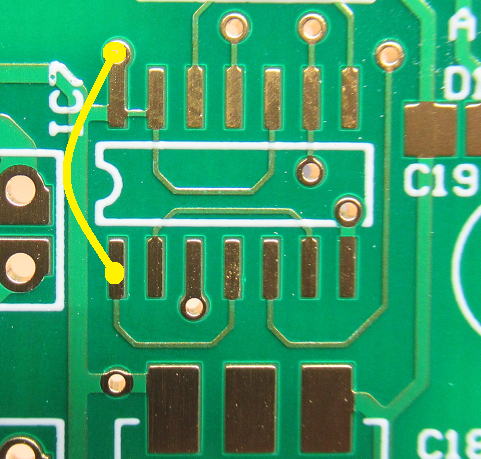

1箇所間違い発見!

クロックの出方が不安定だなあ〜とおもっていたら、基板に1箇所配線抜けがありました。

クロックの1/4分周出力だけ出ないと思って調べてみたらロジックのFF(フリップフロップ)回路

のCLRとPR端子のプルアップが抜けていました.

ということで、修正です。SOパッケージ(1.27mmピッチ)なので、ピン間であってもジャンパーは

できますが、端ピン(Pin1)なので簡単でした。

Pin1を最寄りのVDD(.3.3V)に接続するか、あるいはPin14に接続して修正です。

PIN1を最寄りのVDD端子に接続して修正する場合。 PIN1をPIN14に接続して修正する場合。

ここは距離の短い最寄りのVDD端子に接続しました.

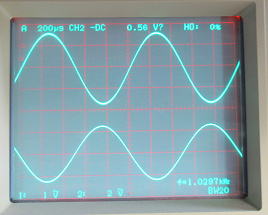

PCMで動作確認

ブレッドボードでの動作確認と同様にDAC4398に接続して動作確認です.

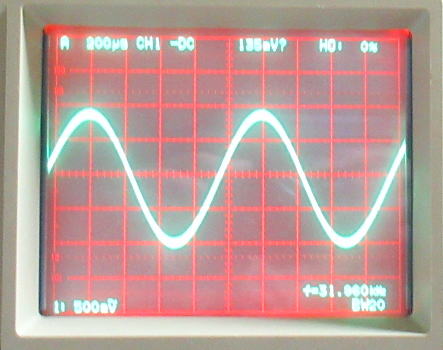

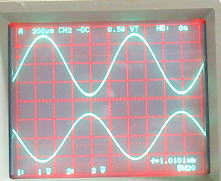

ADC5572に正弦波を入れて、DACの出力を観測です。

問題なく動作することは確認できましたが、出力レベルが低いです。

まあ、これはアナログ回路の定数も問題ですが。

DAC4398に接続して動作確認です。

動作しましたが出力レベルが低いですね〜(判っていましたが)

アナログ回路を見直し

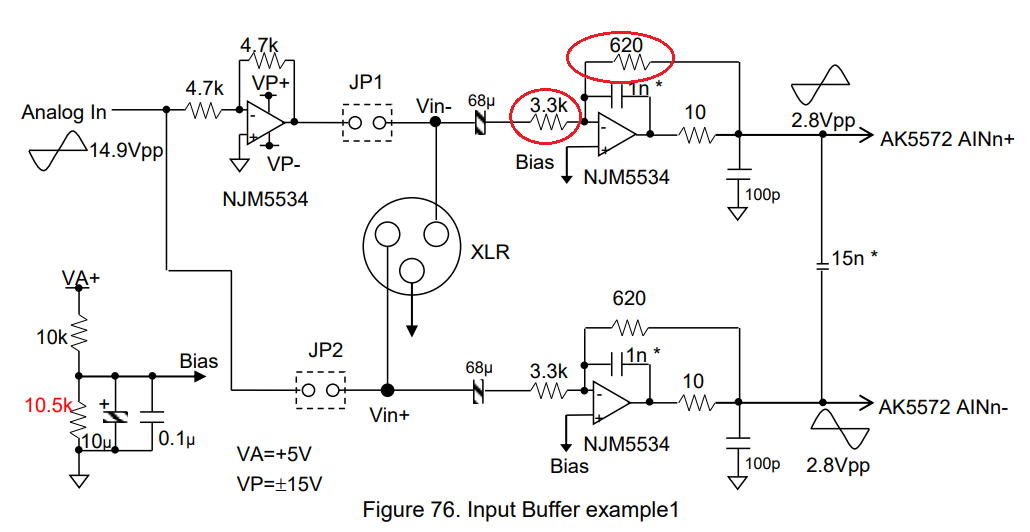

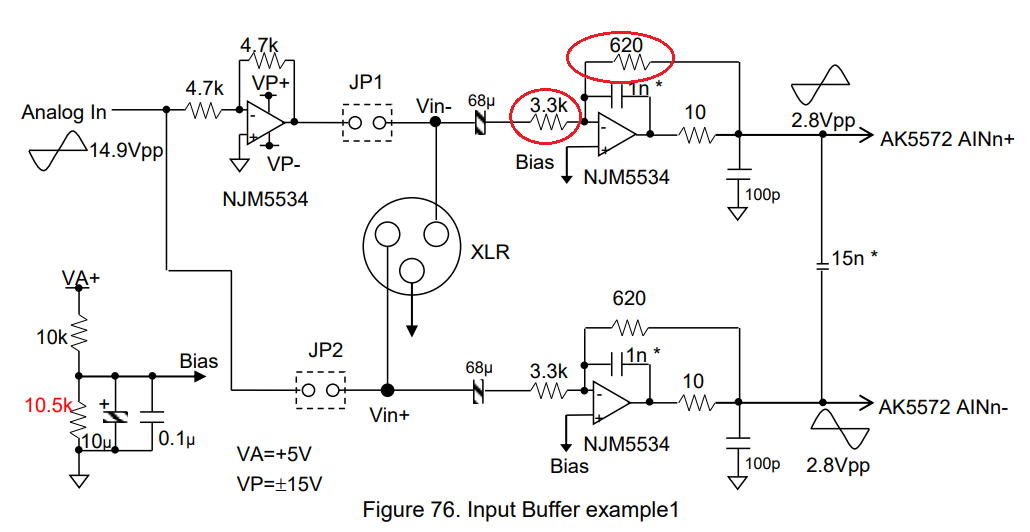

最初なので、アナログ回路はデータシートそのままで組んでみましたが、この回路では

入力信号は14.9Vppを前提としています。こんな大きな入力信号って普通ないですよね〜。

2段目の増幅段では3.3kと620Ωの抵抗で0.19倍の反転増幅器になっています。

一般的なDACなどの出力機器は2Vrmsでしょうかから、振幅に直すと約5.6Vppです。

そのため、2段目の反転増幅器のゲインは0.5倍程度に押さえたほうがいいでしょう。

方法としては、.入力側の3.3kの抵抗を小さくするか、620Ωの帰還抵抗を大きくするかの

どちらかですが、3.3kΩの抵抗を小さくすると入力インピーダンスがそのまま下がってしまうので、

ここは帰還抵抗を上げるようにしましょう。

ゲインを0.5倍に設定するので620Ωを1.6kに変更です。

データシートのアナログ回路では入力が14.9Vppになっています。かなり大きな入力信号です。

抵抗以外の部品変更は必要かな?

抵抗値を変更すると,LPFのカットオフ周波数が変ってしまうので、コンデンサの変更が必要かもしれません。

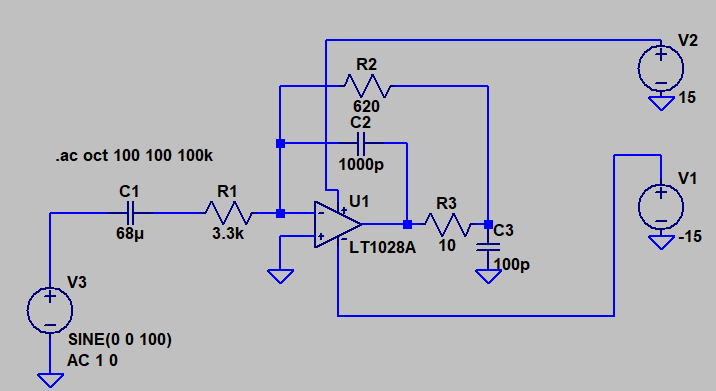

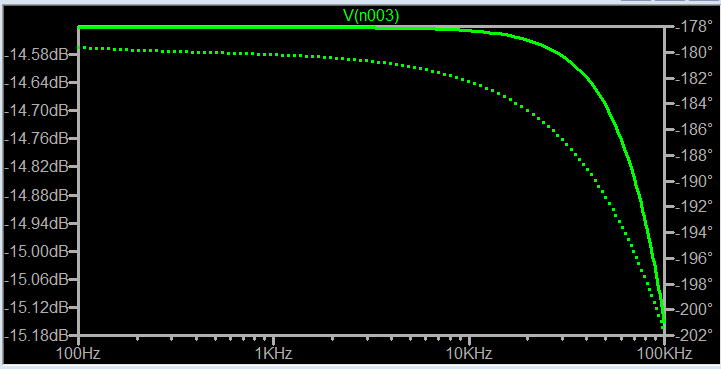

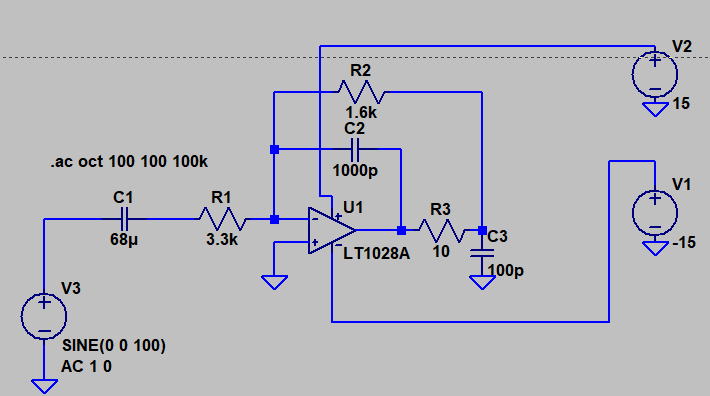

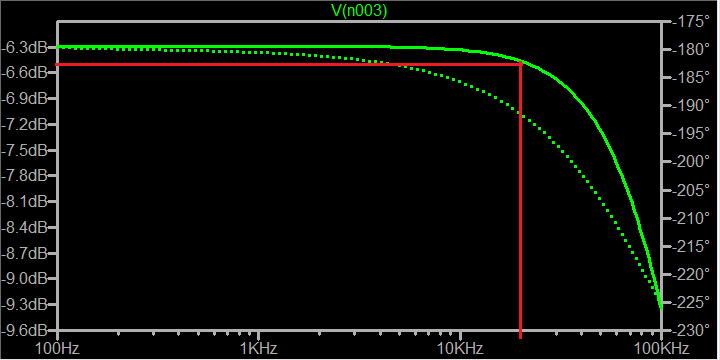

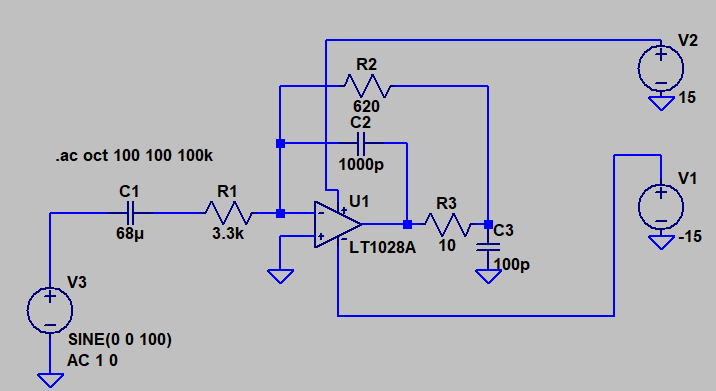

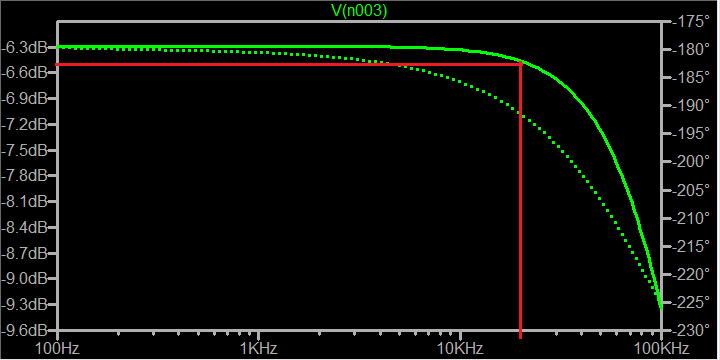

LPFの周波数は簡単に計算できますが、ついでなのでSPICDEにかけてみました。

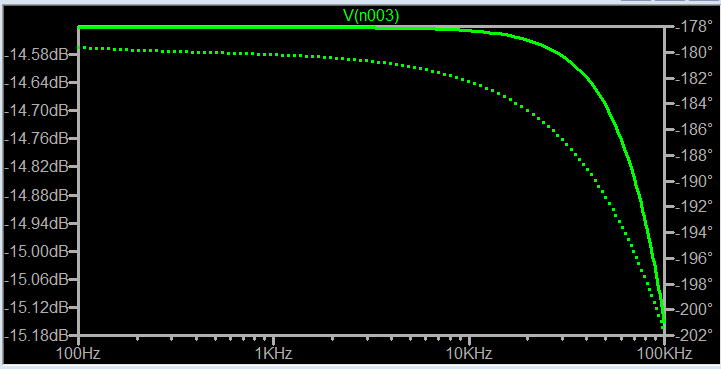

まずは、データシートでの定数で計算です。

データシートの回路図で計算すると、LPFは100kHzで-0.5dBでした。かなり高いカットオフです。

データシートの回路図でのカットオフはかなり高いです。

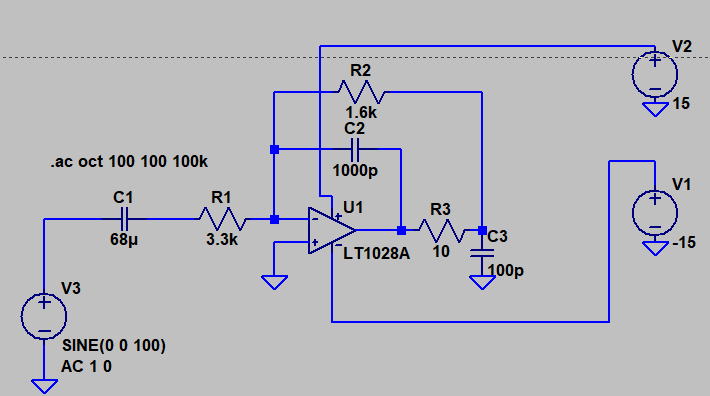

帰還抵抗を620→1.6kに変更

ここで620Ω抵抗を1.6kΩに変更です。この場合はカットオフは下がりますが、20kHzのポイントで-0.3dB程度でした。

まあ、まったく問題ないですね。ただ、ハイレゾ対応に拘るならコンデンサの値も半分程度にしておけばいいでしょう。

帰還抵抗を変更して計算してみました.この場合、LPFは20kHzで-0.3dBでした。

このくらいの周波数特性なら問題なしですね。コンデンサは変更無しとしましょう.

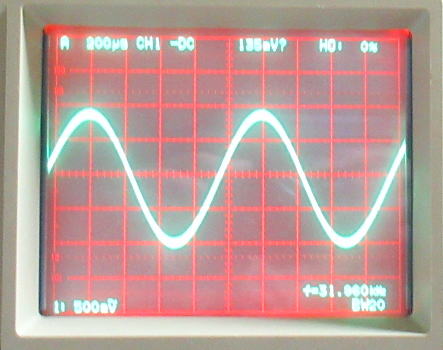

抵抗は1.8kΩに付け替え

1.6kΩに付け替える予定でしたが、手元に1.8kΩの抵抗があったので思わすそれに付け替えました。

多少ゲインが上がりますが、まあいいでしょう。

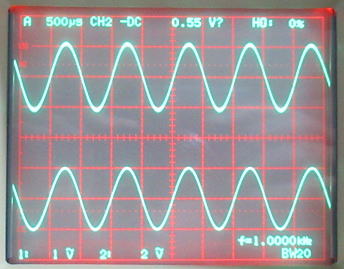

一応入出力の関係をみておきましょう。

下のオシロの写真のように、ゲイン0.5(-6dB)より若干大きくなってしまいました。

下:入力(CH2,2V/Div)、上:ADC入力(CH1:1V/Div)

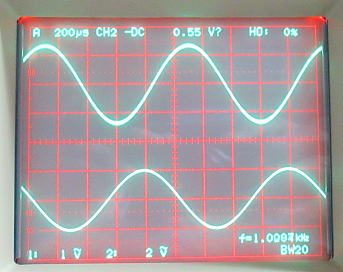

この状態で出力をDACに入れ替えてチェックです.

先の状況より、DACの出力も大きくなりました。

ADC入力としては4.9Vppを超えるあたりからOVFのLEDが点灯しだしました。

4.9Vppの入力で歪ですから、ADCとしてはデータシート通りの変換レンジになっていますね.

下:入力(CH2,2V/Div)、上:DAC入力(CH1:1V/Div)

出力がクリップする手前の波形です.

下:入力(CH2,2V/Div)、上:DAC入力(CH1:1V/Div)

出力がクリップしたした状態です.入力信号は4.9Vppです.

次はDSDで動かしてみましょう!

DSDに設定してみましたが、変換レベルはPCMの場合とほぼ同じですね。

下:入力(CH2,2V/Div)、上:DAC入力(CH1:1V/Div)

DSD変換時時

さて、一度ジャンパーの設定と動作モードを整理しておきましょう!

その前に

PCMやDSD信号の機器間の接続にLANケーブルやHDMIケーブルが使えると便利なのです。

本来は、LVDS信号に変換してで転送するのですが、そのためにはレベル変換のためのICが必要で、

結構な値段がします。結構といっても1個1000円もしませんが、それでもチャンネル数が多くなると

財布に厳しくなってきます。それにオーディオ機器間の距離は数10cm程度でしょうから、LVDSへの

変換ICなしにシングルエンドで使えるように基板が作ってあるので、それらの動作確認もしておきました。

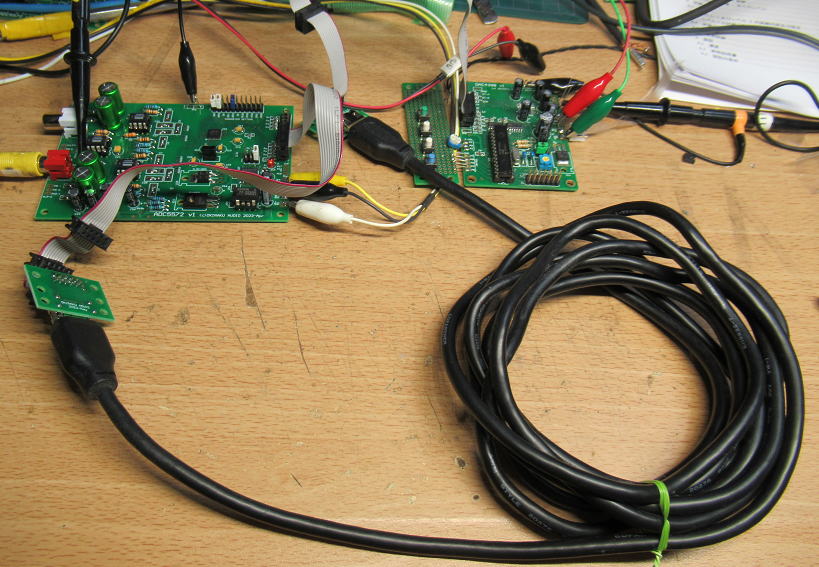

LANケーブルでもHDMIケーブルの、どちらも動作確認です。

LANケーブルならびにHDMIケーブルをつかってシングルエンドで送受するための基板類です。

まずはLANケーブルでのテストです。コスト的にはこれが一番安価です(コネクターやケーブルも秋月で100円程度で購入可能です)。

HDMIケーブルでのテストです。コスト的にはケーブルがやや高いですが、オーディオ的なみてくれはいいかもです。

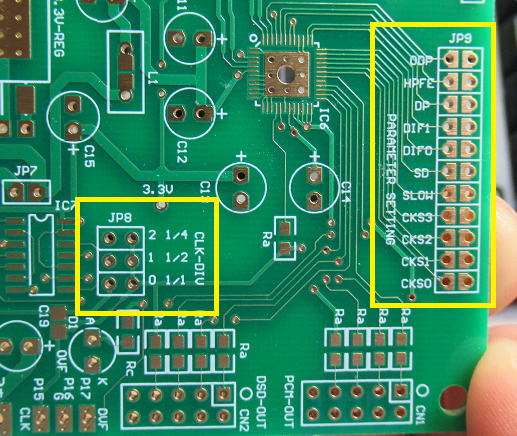

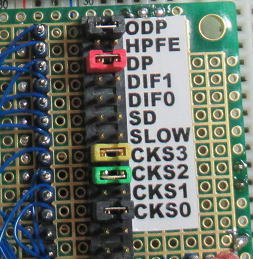

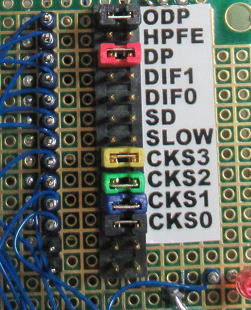

設定を整理しておきましょう! 2023.7.5

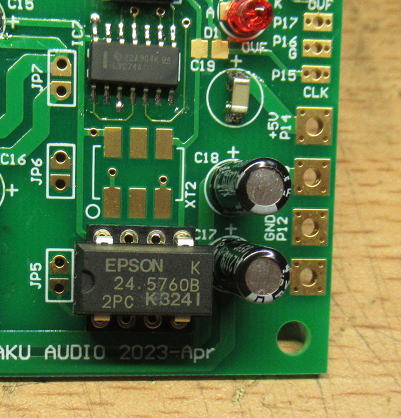

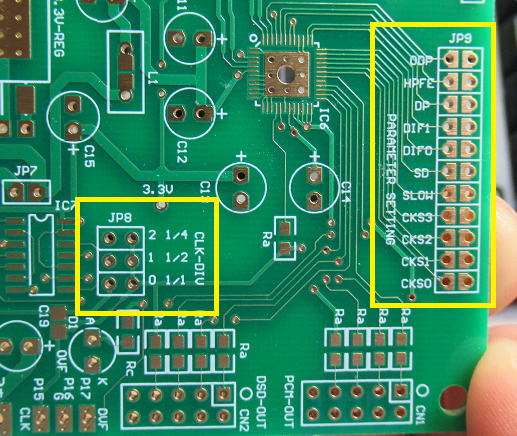

この基板の設定はJP8のクック分周とJP9のパラメータセッティングです。

JP8は実装したXT1,XT2の周波数を1/1、1/2、1/4に分周します。

AK5572では24.576MHzのクロックを使うことを前提としている様子でもあるので、

発振器に24.576MHzを使う場合は1/1を選択します。発振器に49.152MHzを使う場合は

1/2に設定です。ということで、1/4はほとんど使うことはないでしょう(となると、基板の修正

は不要になっちゃいますね)。

基板の動作設定はJP8とJP9で行います。

JP9はPCM出力あるいはDSD出力で設定が変わります。

(1)PCM出力の場合

PCMの場合は下表の様に設定です。HPFEやSD,SLOWについては好みでの設定でいいでしょう。

出力フォーマットの変更もできますが、I2SあるいはMSB(左詰め)の2択ですから、なにも考えずに

I2Sを選択してビット長も32Bitにすればいいでしょう。右詰めフォーマットがないのはなぜだろう?

|

PCM出力設定 |

備考 |

| ODP |

L |

|

| HPFE |

L (HPF-Disable)

H (HPF-Enable) |

好みで設定。 |

| DP |

L |

PCMでは常にL |

| DIF1 |

H |

I2S,32Bit設定

(それ以外はあまり使わないでしょう) |

| DIF0 |

H |

| SD |

SD=L , SLOW=L Sharp Roll-off filter

SD=L , SLOW=H Slow Roll-off filter

SD=H , SLOW=L Short DelaySHarp Roll-off filter

SD=H , SLOW=H Short Delay SHarp Roll-off filter |

好みで設定。

通常はSD=SLOW=Lでしょう。 |

| SLOW |

| CKS3 |

マスタークロックとFSの関係は下表の通り。 |

|

| CKS2 |

| CKS1 |

| CLK0 |

PCMの場合、サンプル周波数設定はCLK3〜CLK0で行います。

マスタークロックは24.576MHzに設定した場合は下表になります。

なお、768fsにも設定できるようですが、32fsになるのでデータは16bitになってしまいます。

マスタークロック24.576MHzでは最大サンプル周波数は384kHzと思った方がいいでしょう。

|

マスタークロック 24.576MHzの場合 |

|

48kHz

(512fs) |

96kHz

(256fs) |

192kHz

(128fs) |

384kHz

(64fs) |

768kHz

(32fs) |

| CKS3 |

L |

L |

L |

H |

H |

| CKS2 |

H |

L |

L |

L |

L |

| CKS1 |

H |

H |

L |

L |

L |

| CLK0 |

L |

H |

L |

L |

H |

マスタークロックを49.152MHzに設定した場合は、サンプル周波数768kHzに限定されそうです。

このマスタークロックだとサンプル周波数768kHzで64fsになりますから、32Bit出力になるでしょう。

でも、接続できるDACはかなり限られそうです。

|

マスタークロック 49.152MHzの場合 |

|

48kHz

(1024fs) |

96kHz

(512fs) |

192kHz

(256fs) |

384kHz

(128fs) |

768kHz

(64fs) |

| CKS3 |

|

|

|

|

H |

| CKS2 |

|

|

|

|

H |

| CKS1 |

|

|

|

|

L |

| CLK0 |

|

|

|

|

L |

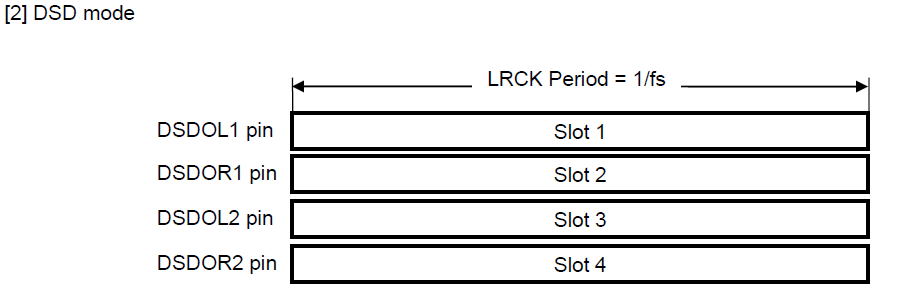

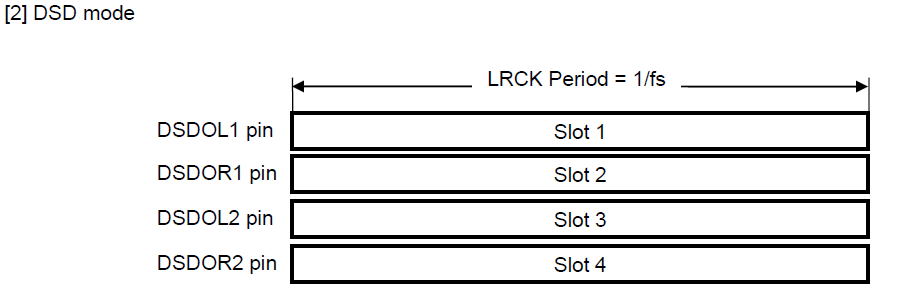

(2)DSD出力

DSD出力の場合は、あまり設定できるところはありません。マスタークロックは24.576MHzをつかって、

あとはサンプル周波数をDSD64,DSD128,DSD256から選択するだけの感じです。

|

DSD出力設定 |

備考 |

| ODP |

L |

|

| HPFE |

L |

DCKSに読み替え

(L)512fsで使用。(H)768fsはあまり使用しないと思います |

| DP |

H |

DSDでは常にH |

| DIF1 |

下表参照 |

DSDSEL0に読み替え |

| DIF0 |

DSDSEL1に読み替え |

| SD |

Lで固定 |

位相変調なし |

| SLOW |

| CKS3 |

DSDでは未使用 |

|

| CKS2 |

| CKS1 |

| CLK0 |

|

マスタークロック 24.576MHzの場合 |

|

DSD64

(BCK=3.072MHz) |

DSD128

(BCK=6.144MHz) |

DSD256

(BCK=12.288MHz) |

| DSDSEL1(DIF1) |

L |

L |

H |

| DSDSEL0(DIF0) |

L |

H |

L

|

マニュアル作成 2023.7.9

製作マニュアルを作成しました. ADC5572_Manual.pdf

近日リリース予定です。

(つづく)