DACの構成図

さて、ソフトの構成は

FFDAC9018Sとサブルーチンを共有してつかっているところが多いので、よく似た構成になっています。

ES9018SでDSDシフトパラは実現するか?の巻き PART2 2012.4.30

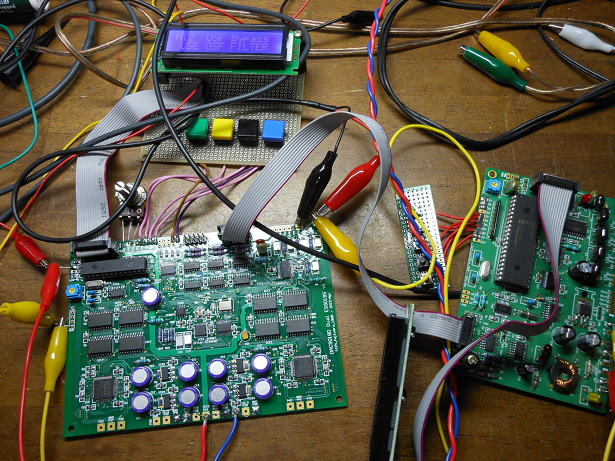

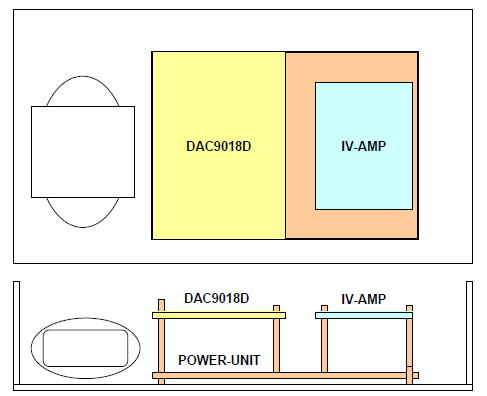

すこし、今回のDACのH/W構成をまとめてみることにしました。ブロック図は下記のとおりです。

入力はSPDIF(4ch)、PCM、DSDの3系統。

SPDIFは一旦CS8416で受けます。ただしCS8416でデコードした信号で活用するのはBCKのみで、

ES9018にはSPDIF信号をそのまま受け渡します。これはSPDIFでもBCKの逓倍のシステムクロックが

つかえるようにするためです。

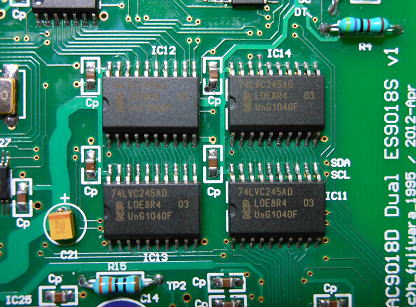

SPDIF、PCM,DSDのデータについてはデータセレクタの74245を介してES9018Sに送られます。

DSD信号についてはシフトパラ信号をつくるため、シフトレジスタの74164を通してデータセレクターに

送られます。

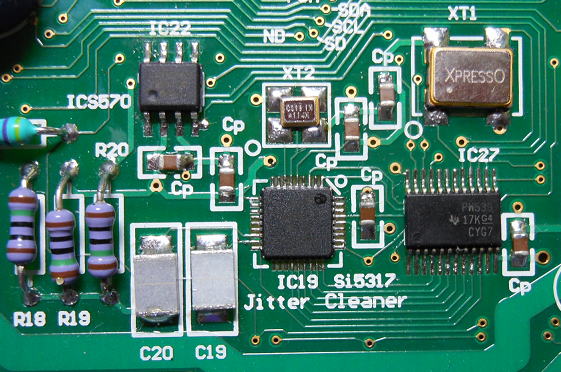

BCKからシステムクロックを生成するために逓倍器のICS570とジッタクリーナのSI5317を用います。

この逓倍クロックを使用するか、あるいは100MHzの水晶をつかうかは切り替えられるようにしています。

DACの構成図

さて、ソフトの構成は

FFDAC9018Sとサブルーチンを共有してつかっているところが多いので、よく似た構成になっています。

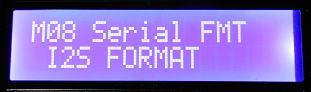

| No | 表示例 | 設定項目 |

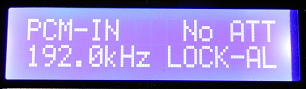

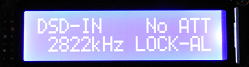

| 0 |    Front pageにあたります。入力(SPDIF0〜3、PCM,DSD、S-DSD、 電子ボリューム減衰量、入力周波数そしてロック状態を示します。 LOCK-AL(LOCK ALL)となればES9018とジッタクリーナ(Si5317)すべて ロックしています。 |

入力信号切替え SPDIF1 SPDIF2 SPDIF3 SPDIF4 PCM-IN DSD-IN S-DSD (*) (*)Shifted Para. DSD |

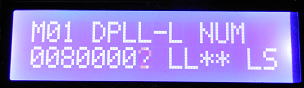

| 1 |  ES9018の左チャンネルDPLLレジスターの表示(16進)です。 LL**はES9018のロックとMUTE状態、LSはジッタクリーナのロックと シグナル有無を示しています。 これらはDACのステータス(状態)を示します。 |

|

| 2 |  ES9018の右チャンネルDPLLレジスターの表示(16進)です。 |

|

| 3 |  DPLLのバンド幅設定です。 |

Best No Lowest Low Med-Low Medium Med-High High Highest |

| 4 |   逓倍器の使用の有無を設定します。ALL OFFにすれば100MHzの水晶発信器 のみをつかいます。SPDIFへの適用あるいはPCM,DSDへの適用、あるいはすべてへ 逓倍クロックを適用するかを選択することができます。 通常はALL ONにすればいいでしょう。 |

ALL OFF SPDIF PCM,DSD ALL ON |

| 5 |  ジッタクリーナ(Si5317)のバンド幅を設定します。LOWESTに設定するともっとも 周期が長くなり、もっとも安定した出力を得ることができます。 |

LOWEST LOW MID MID-HIGH HIGH |

| 6 |  ディジタルフィルータ応答を切り替えます。 |

Fast Roll-off Sharp Roll-off |

| 7 |  シリアルデータ入力(PCM)時のデータ長を指定します。 |

16 20 24 32 (BITS) |

| 8 |  PCM入力時のデータフォーマットです |

I2S Right Justified Left Justified |

| 9 |  出力の極性を設定します。In-phaseにすると正相、Anti-Phaseにすると 逆相になります。 |

In-Phase Anti-Phase |

| 10 |  差動出力の極性を設定します。Anti-Phaseにすると差動出力。 In-Phase にすると同相出力になります。 同相出力にすると16パラのシングルエンドDACとして使うことも可能です。 |

In-Phase Anti-Phase |

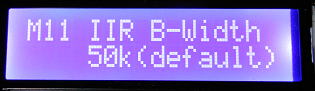

| 11 |  IIRフィルターの設定です。 |

Normal 50k 60k 70k |

| 12 |  Over Sampling Filterの設定です。 |

Use Direct from I2S |

ここまで組んだらプログラム容量が82%になってしまいました。あわせてシンプルファンクションモードも組み込みたいけど

入るかな〜???

ソフト作成中です。

ソフト完成!2012.5.2

ほぼデバッグも完了です(と思うけど・・・)。フルファンクションモードに加えて液晶表示の不要なシンプルファンクションモードも

ひとつのPICに入れ込みました。途中でPICの容量が100%近くなったので、プログラムを見直して重複しているところを整理した

りしたら、85%まで回復したので、さらにフルファンクションモードで機能を追加しました。

最終的な容量は91%になりました。

追加した機能はFIRフィルターに関して 28 coefficeients in length と 27

coefficeients in lengthの切り替え、

さらにES9018内部のジッタリダクションの有無の設定ができるようにしました。

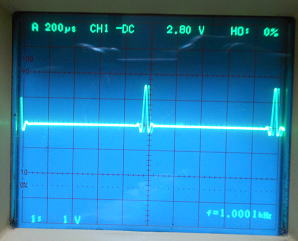

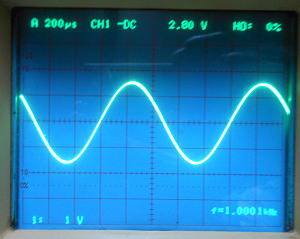

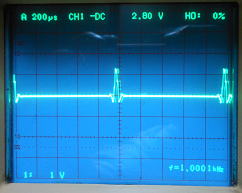

coefficeients in lengthの切り替えって、どう違うのか波形で調べてみるとかなり変形します。

デフォルトの 28がいいでしょうけど、音はどう変わるのか楽しみです。

| 28 coefficeients in length | 27 coefficeients in length | |

| 表示 |  |

|

| 波形応答 |  インパルス応答(Slow rolloff)  1kHz正弦波 |

インパルス応答(Slow rolloff)  1kHz正弦波 |

いきなり試聴!

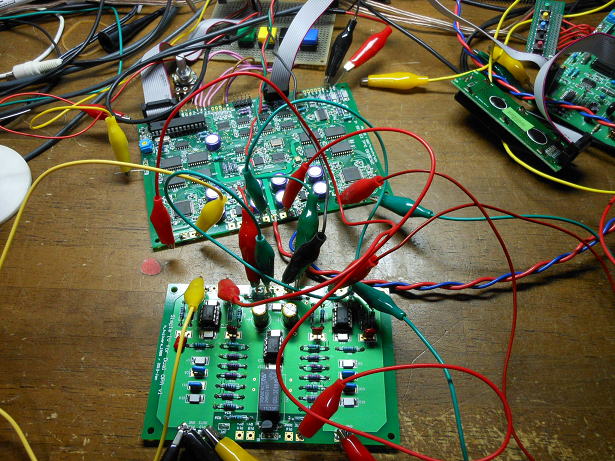

動くことが確認できたので、やっぱり試聴したくてむずむずしてきます。

ということでシンプルIV(DUAL OPA版)を接続して試聴です。

試聴時の接続の様子

DSDももちろんつなげるようにしています。ちなみに表示はこんな感じです。

DSD64入力時の場合 DSD128入力時の場合

ソフト的にはDSD256の入力も対応していますが、残念ながらソースがないので確認できていません。

こんなものもあります。

同一演奏でDSDとWAVの聴き比べようにとファイルをいただきました。これらもも併せて聴いていきましょう

DSDとWAVファイルがはいっています。

恥ずかしい・・・・

表示の綴りが間違っているとご指摘いただきました。入力信号が既定の周波数から

はずれるとUNKNOWNと表示するつもりが、UNKOWNになっていました。

修正前(恥ずかしい・・・) 修正後

今回のDACでは既定の周波数は下記の15種類を設定しています。

それぞれの周波数と動作状況をまとめてみました。

SPDIF入力では32kHz未満の周波数で動作しませんでした。どうやらES9018自体がSPDIFの

低周波数領域では対応していないみたいです。またCS8416自体も16kHzでは動作しないようです。

PCM(I2S等)では16kHzから問題なく動作しました。

いづれにしても192kHzを超える領域では、それだけ高周波数fsで送り出す

機器がないので動作は確認していません。おそらく大丈夫だとおもいますが、機会があれば

動作させてみたいところです。

既定周波数と動作範囲範囲をまとめてみました。

| No | 既定周波数 (kHz) |

BCK周波数 (MHz) |

逓倍クロック 周波数(MHz) |

SPDIF動作 | PCM(I2S)動作 | DSD動作 |

| 1 | 16.00 | 1.0240 | 32.768 | × | ○ | − |

| 2 | 22.05 | 1.4112 | 45.1584 | × | ○ | − |

| 3 | 24.00 | 1.5360 | 49.152 | × | ○ | − |

| 4 | 32.00 | 2.0480 | 65.536 | ○ | ○ | − |

| 5 | 44.10 | 2.8224 | 90.3168 | ○ | ○ | ○(DSD64) |

| 6 | 48.00 | 3.0720 | 98.304 | ○ | ○ | − |

| 7 | 64.00 | 4.0960 | 81.92 | ○ | ○ | − |

| 8 | 88.20 | 5.6448 | 90.3168 | ○ | ○ | ○(DSD128) |

| 9 | 96.00 | 6.1440 | 98.304 | ○ | ○ | − |

| 10 | 128.00 | 8.1920 | 98.304 | ○ | ○ | − |

| 11 | 176.40 | 11.2896 | 90.3168 | ○ | ○ | -(DSD256) |

| 12 | 192.00 | 12.2880 | 98.304 | ○ | ○ | − |

| 13 | 256.00 | 16.3840 | 98.304 | - | - | − |

| 14 | 352.80 | 22.5792 | 90.3168 | - | - | -(DSD512) |

| 15 | 384.00 | 24.5760 | 98.304 | - | - | − |

○:動作確認済み ×:動作しません。 −:未確認

本格試聴!

SPDIF入力

ES9018でのSPDIF入力はすでに経験していますが、やはりモノラル使用だとなんとなく

音の厚みが増しているような気がします。これもシステムクロックをBCK逓倍+ジッタクリーナ

としているのが効いているのかもしれません。

PCM(I2S)入力

これも安定感のある音がで手くる感じです。とくにES9018をLOWEST設定、ジッタクリーナも

LOWEST設定にすると、ずんと重心が下がる気がします。SPDIFもいいですが、PCM入力は

16kHzから動くので、その分の安定性もあるのかもしれません。

DSD入力

これもDSD専用の音源でfour playを聴いてみましたが、滑らかな再生です。ビット臭さが消えるのかな(笑)。

でも、ビット臭さも好きだけど(爆)。もうこなったらプラシーボ全開です!

S−DSD入力

シフトDSDになると、DSDの滑らかさがさらに増した感じもします。感じだけかな?

いづれにしても、なかなかいいDACに仕上がりました。

難点は少し基板サイズが大きいのと、部品点数が多いところでしょうか。

老眼が進むなかでの作業は、だんだん大変になってきますが、半田付けの点数が多くなると

俄然楽しくなってくるのも趣味ならではですね。

お出かけ用の写真をパチリ

いろいろいじって汚くなる前にお出かけ用の写真をとりました。

お出かけ用の写真を撮っておきました。

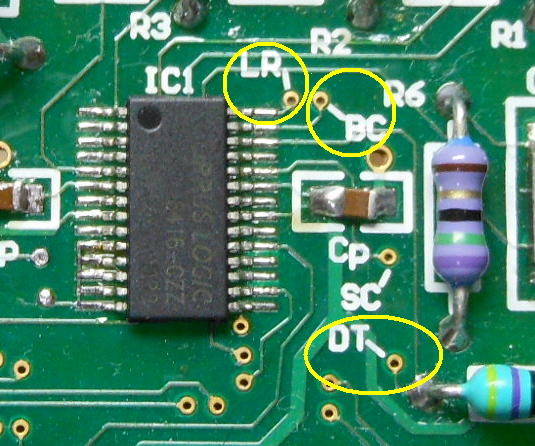

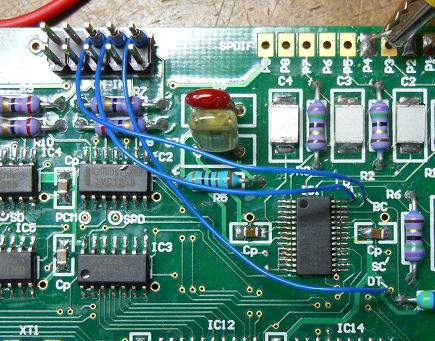

さらに局部的なアップも撮っておきました。

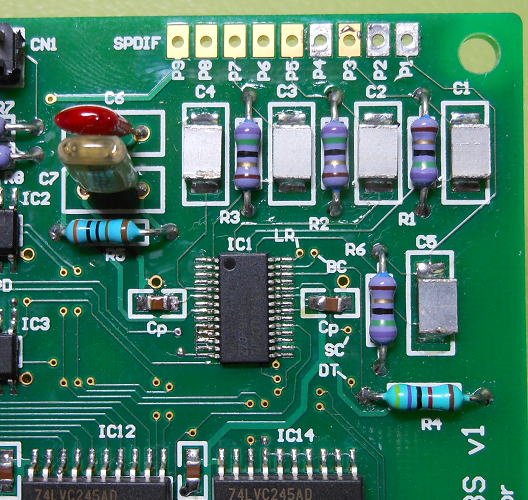

SPDIFのアンプ部にはCS8416をつかっています。またBCK抽出に使っています。

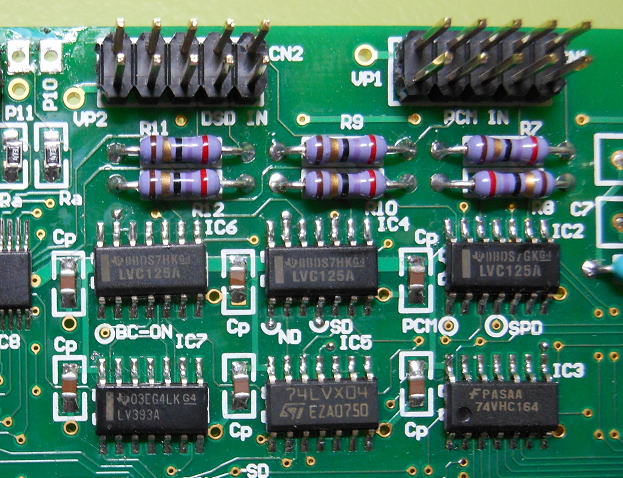

PCM、DSD入力部分です。バッファーアンプとコントロールロジックです。

IOエクスパンダが写っていますが、このICだけ向きが違うので実装には注意が必要です。

シルクを確認しながら実装します。

4つの74245はSPDIF、PCM、DSD、S-DSDの信号切り替え器です。

左右チャンネルにあります。

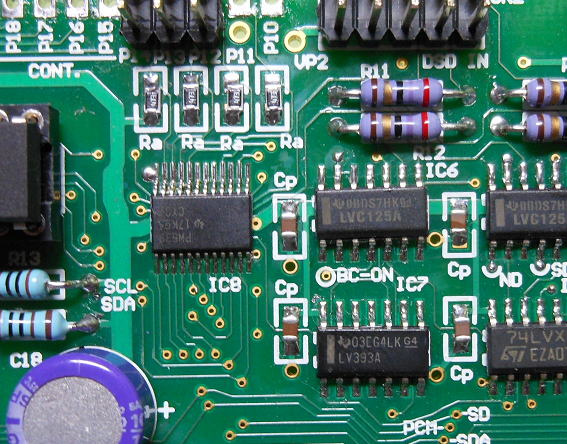

この基板の1つの肝ともいえるシステムクロック生成用の水晶(100MHz)と

クロック逓倍器(ICS570)+ジッタクリーナ(Si5317)です。

制御IOが多いのでIOエキスパンダを直近に配置しています。

でも主役はこれ。ES9018です。

機能追加してみました。 2012.5.9

こんなメールいたしました。

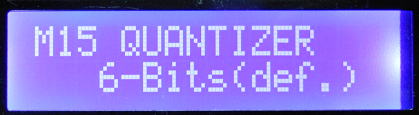

| ES9018のDataSheetには乗っていないのですが、 QUANTIZER(量子化ビット数)を設定するレジスタをご存じでしょうか。 ここを変更することで結構音に違いがあります。 フルファンクションモードでここを設定できるようにするか 7-bit QUANTIZERを起動時に設定していただけるようにできないでしょうか。 register 15 6-bit QUANTIZER 8'b00000000 (default) 7-bit QUANTIZER 8'b01010101 8-bit QUANTIZER 8'b10101010 9-bit QUANTIZER 8'b11111111 ES9018にはDACモジュールが8個ありますが、音をよくする方法として、DACモジ ュールの出力を束ねる方法と大きなビット数で量子化器を使ってDACモジュール に送る方法があるとのことです。 register 15は、QUANTIZERを設定するレジスタで、 6-bit〜9-bitまで設定できます。 ただし、8、9-bitの場合、DACモジュールを消費してしまうため、出力を束ねる ことができなくなるというデメリットがあるとのことです。 register 15はデフォルト値は8'b00000000ですが、うちのBaffaloIIでは7-bit QUANTIZERを設定して使用しています。 明らかによくなった気がします。 |

追加はそれほど難しくありませんが、プログラムの容量が心配ですがなんとか押し込めました。

追加した機能です。

消費電流は・・・・

これについては実測はしているのですが44.1kHzのときだったので192kHzの入力時にどうなるか調べてみました。

なんとES9018が電圧出力時でも690mA(アナログ約105mA、ディジタル585mA)も消費します。

ということは電流出力になると約80mA増えると考えればよいので、

ディジタルは600mA以上、アナログ部は200mA以上用意する必要がありそうです。

余裕をみればディジタル800mA、アナログ部300mAでしょうか。

かなり電源はしっかりと作る必要があります。

こんなリクエストも

なるほど。CS8416の周りにはDATA、LRCK、BCKを取り出すランドがあるので、そこからPCM入力(CN2)に

接続すればいいですね。そういった入力モードも作ってみましょう。

CS8416周辺のデータの取り出しパッドです。

取り出しパッドからPCM入力(CN2)へ配線です。

表示は

こんな感じです。SPDIF1PのPがポイントです。CS8416の入力を切り替えつつ、

実際のデータはPCM(CN2)にしています。

表示はこんな感じ。SPDIF1の後のPがポイントです。

このため入力は

SPDIF1

SPDIF2

SPDIF3

SPDIF4

PCM−IN

DSD−IN

S−DSD

SPDIF1P

SPDIF2P

SPDIF3P

SPDIF4P

のなかからセレクトすることになります。少し多くなってしまいましたが、まあ自作ならではですね。

ちなみに、この入力パターンはフルファンクションモードのみサポートです。

さて、ここまで機能を増やしたらプログラム容量も97%になりました。

もう無理です。さて、このPICプログラムバージョンでリリースしていきましょう。

といっても週末は合宿なので、作業が出来るのは日曜日の夜になりそうです。

電源をどうしよう 2012.5.15

このDACはとても電流を必要としてます。3.3Vで約800mAです。

RA40-144トランスの容量は十分ですが、リニアレギュレータで構成すると大きな放熱板が必要です。

8V(AC)出力を使用した場合、整流後の電圧は約11Vです。それを3.3V800mAを流すまでドロップさせると

(11-3.3)*0.8=6.16Wの熱損失があります。この電力は小型の放熱板で補えるものではありません。

ということで、すこし電源を考えないといけないです。

ひとつの案は

3.3Vラインはアナログとディジタル部にわかれます。ディジタルは約600mA、アナログは約200mA(100mA×2)です。

アナログ部はでリニアレギュレータとして左右分離すれば、片チャンネルあたりの熱損失は(11-3.3)*0.1=0.77Wであり、

これは小型の放熱板でも大丈夫でしょう。問題はディジタルです。そこでディジタル部はスイッチングレギュレータとリニアレギュレータの

ハイブリッドを考えてみましょう。スイッチングレギュレータで5Vまで降圧し、そこから3.3Vまでリニアレギュレータで落とします。

そうすれば、効率と電圧リップルの低減の両立をはかることができます。電力損失は(5-3.3)*0.6=1.02Wですから小型の放熱板

でも大丈夫でしょう。

こんなスイッチングICを買ってみました。

5V固定電圧出力ですが3Aの容量のあるICを買ってみました。

これをつかって特性を調べていきましょう。

AP1506です。

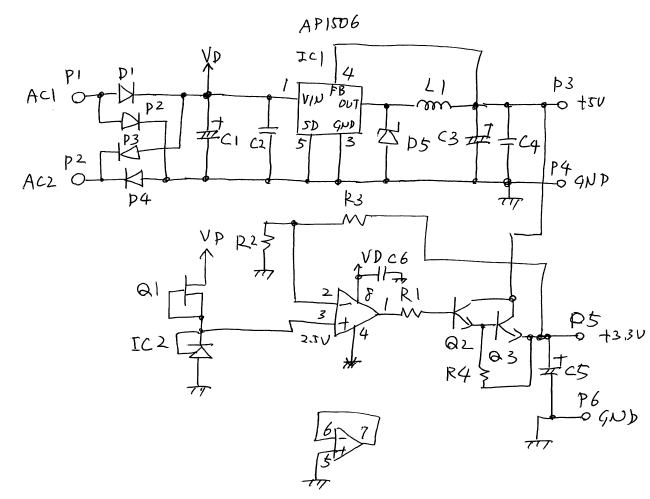

回路はこんな感じでしょう。5→3.3Vのリニアレギュレータは3端子レギュレータでもよいのですが、

もうすこし性能を出したいこともありOPAによる制御回路を採用してみましょう。基準電圧は

シャンとレギュレータのTL431(IC2)を使います。誤差増幅のOPAはまずは安価なLM358あたりを

使ってみましょう。

試作してみる回路はこんな感じ。

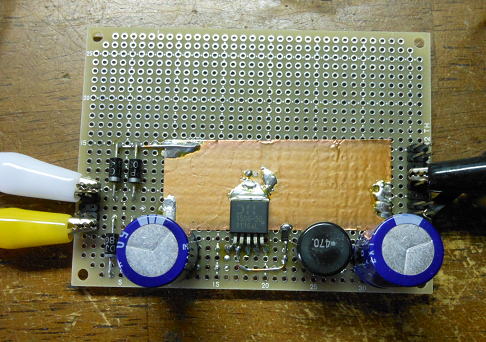

ユニバーサルでつくってみましょう。2012.5.20

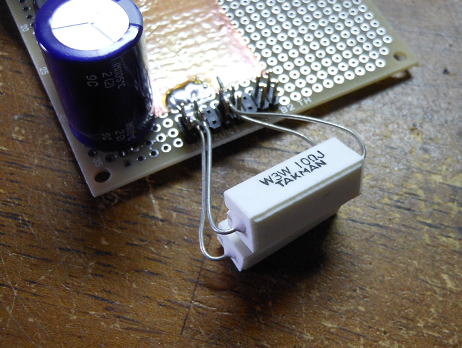

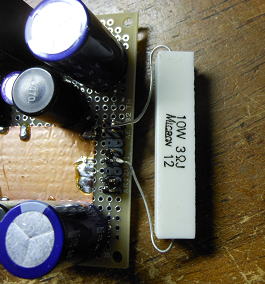

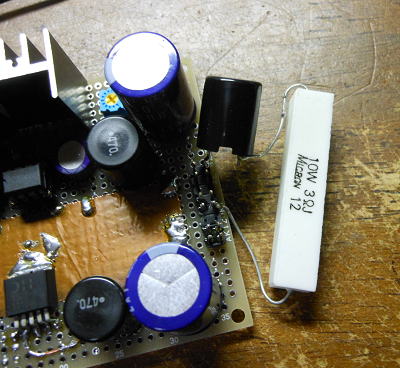

まずは5Vのスイッチングレギュレータ部をつくりました。部品は手元にあるものだけでです。

コンデンサは1000uF/50Vのものです。これはデジットで安かったので大量に買いましたが、

いつになったら消費できるのって感じです。

まずはスイッチングレギュレータ部のみをつくりました。

無負荷時の電圧を測定してみると5.13Vと少し高めです。でも3%程度ですから問題はありません。

無負荷時の電圧です。

負荷には1A程度をかけようと思います。手元に10Ωの抵抗があったので、それを2つ並列にして

5Ωとしてちょうど1Aが流れるように設定しました。

5Ωの負荷抵抗を接続しました。

負荷を接続すると少し電圧がさがりました。4.95Vなので−1%です。このくらいがちょうどいいでしょう。

負荷時(1A)の出力電圧。

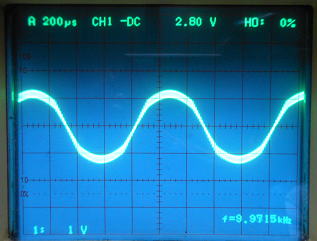

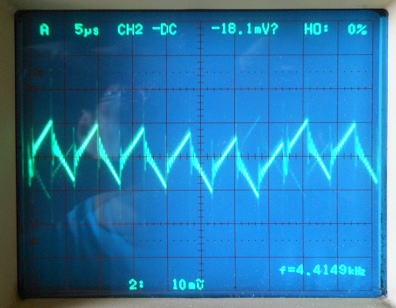

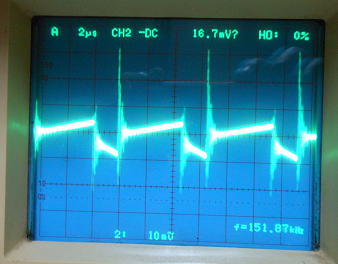

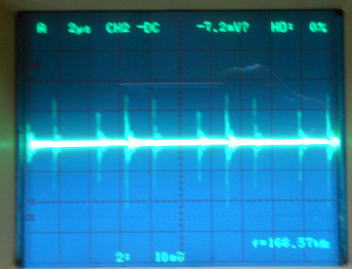

ついでに出力電圧のリップルの様子を観測です。振幅で10mV程度のリップルがあります。

周期は約7uSですから140kHzとスイッチングレギュレータの素子のスペックに合致します。

リップルの低減のために、電解コンデンサに並列にOSコンデンサをいれたところ約半分に減りました。

このところにつかうコンデンサはESRの小さいものがいいですね。

リップルは10mV程度です。

3.3Vのリニアレギュレータをくみたてる。

さて、次は5Vから3.3Vに降圧するためレギュレータ部を組み立てます。

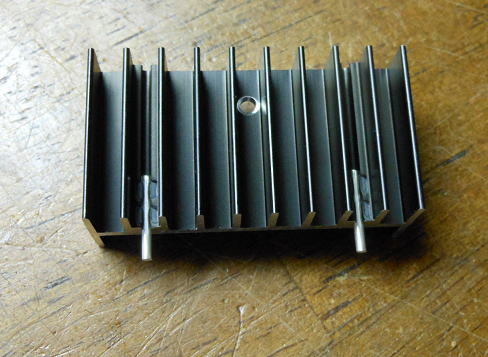

放熱板は秋月で売っている@50円のものをつかいました。これは11℃/Wありますから、

1W程度の消費電力でつかうには十分です。

仕様した放熱板

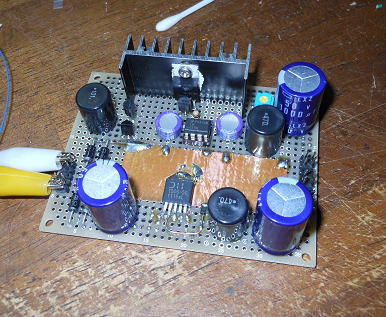

完成!

各種の部品を載せて完成です。レイアウトがあまりよくありませんが・・・・。

まずは完成しました。

負荷には3Ωの抵抗を接続しました。電流にすれば約1.1Aになります。およそDAC9018Dで必要とする

ディジタル部の電流の2倍の負荷になります。

負荷抵抗を接続

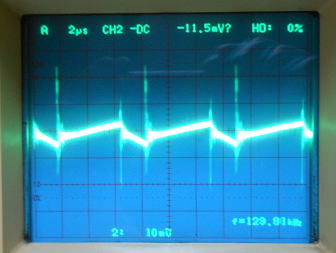

気になるリップルをみて見ましょう。鋭いひげもありますが、およそ振幅で5mV程度かな。

少しへっていますが、この回路での高周波数リップル除去の限界でしょうか。

DAC基板の動作上は問題のないリップルですが、やはりスイッチングレギュレータではなく

すべてリニアレギュレータにするべきかな?ちょっと悩んでしまいます。

振幅で5mV程度のリップルが残留しています。

もう少し、回路をいじってみましょう。

測定方法でずいぶん変わるな〜

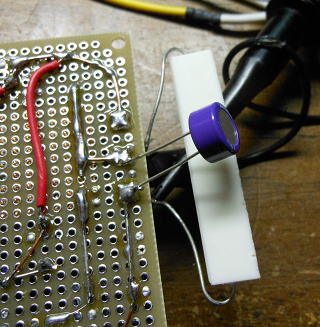

オシロのプローブを動かすと、かなり波形がかわります。どうやらオシロのプローブのループ部で

誘導が起こっているようです。ということで、できるだけループ面積が小さくなるように取り付けました。

オシロプローブのループができるだけ小さくなるようにして接続です。 だいぶ段差が小さくなった

つぎに出力にESRの小さいOSコンデンサをはさんで見ました。

リード線をもっと短くしたいところですが、あとで再利用することも考えてそのままの長さで我慢です。

OSコンをはさむとさらに改善しますね。

OSコンをはさんでみると、さらにリップルが小さくなりました。

つぎにOSコンを取り外して、出力に100uHのインダクターを接続してみました。

こんぼ場合でも改善が見られます。

インダクターをとりつけても改善が見られます。

では、インダクタとコンデンサを両方とりつけてみましょう。

いわゆるLPFを構成することになります。やはりこの場合の効果は大きいです。

ほぼリップルは見られなくなりました。

ただし、高周波数そスパイクは若干残っています。これらはもっとインダクターの容量をあげると抑制できるかな?

インダクターとコンデンサの両方を取り付けて試してみました。リップルはほぼなくなりました。

やっぱり電源はシリーズレギュレータかな。 2012.5.27

スイッチング電源は効率はいいのですが、どうしても高周波数のスイッチングノイズが発生しています。

可聴域をはるかに超えていますが、やはり心理的なハードルがでてしまいます。

ということでは、やっぱり電源はシリーズレギュレータにしましょう。

DAC9018D専用電源はどうかな?

最初、DAC9018Dの基板サイズですべて収まるかな?と思ったりしましたが、放熱板がたくさんいるので

かなり無理そうです。ということで、DAC9018DとIV基板が搭載可能なまで基板サイズを拡張して

すべての電源がまかなえるDAC9018Dの電源を考えてみることにしました。

サイズ的にはRA40トランスと一緒にタカチ電機の23mm幅で奥行き37cmのケースに収める都合上、

電源基板の長さは200mm前後になります。

搭載したときのイメージはこんな感じです。

DAC9018Dの専用電源のイメージ

色々とパターンを考えてみるも・・・・ 2012.6.1

いろいろとパターンを考えてみるも、それにしても基板がでかい!

必要なのは

アナログ電源 正負15V(200mAくらい)×1

DACアナログ電源 正3.3V(150mA)×2

DACディジタル電源 正3.3V(1Aくらい)×1

液晶用補助電源 正5V(50mAくらい)×1

なんだけど、かなりの部分がTYPE-D,TYPE-E電源と重なります。

色々と考えてみるも定まりません。

本当に必要なのは、

DACディジタル電源 正3.3V(1Aくらい)×1

液晶用補助電源 正5V(50mAくらい)×1

の部分があればいいので、この部分だけ小型の基板をつくってもいいのかな〜という気もしています。

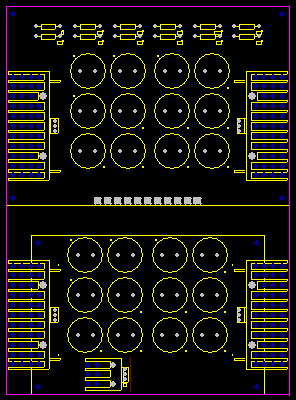

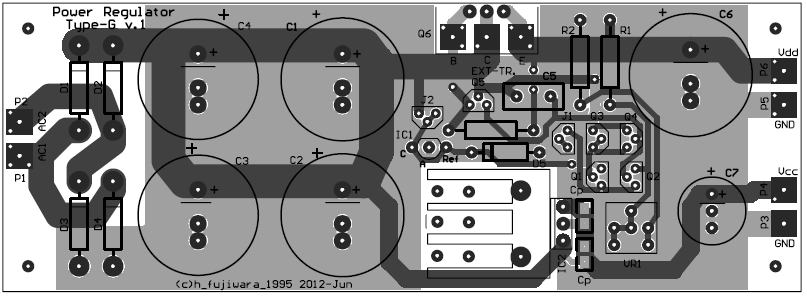

TYPE-G基板にしてみました。

出力は3.3V(1A)と5V(100mA)を想定しています。

3.3Vはディスクリートでの誤差増幅アンプを搭載しています。5Vは簡単に3端子レギュレータです。

3.3Vの出力電流は外付けのトランジスタ容量に依存です。

2段ダーリントンですから、初段が150、2段目が60で10000倍の電流増幅率が見込めます。

初段のベース電流0.1mAで1A程度なら安定して動作するでしょう。もっと電流が必要なら3段以上にしたほうが

いいかもしれません。そのときは2段目をダーリントンタイプにすればいいでしょう。

TYPE−G基板なるものを描いてみました。

リモコン化計画? 2012.6.16

リモコン化計画は別ページに移転しました。(2012.7.1)

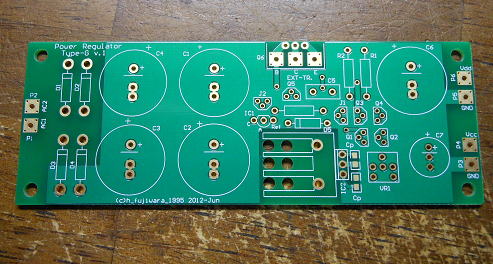

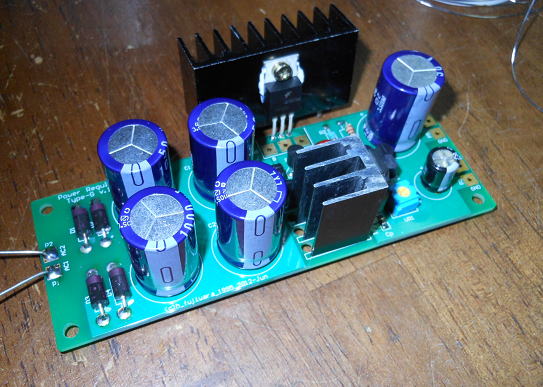

TYPE-G基板到着! 2012.7.4

ようやく基板が到着しました。さて、一気に組み立ててみましょう。

電源基板TYPE−G基板です。

部品箱を探しているとこんなダイオードが見つかりました。おまけでもらったものですが、

何のおまけか忘れてしまいました。ダイオードの容量は2Aあるのでこれで十分でしょう。

おまけでもらった整流ダイオード。音響用って何がちがうのかな?

部品点数も少ないのであっという間に完成です。

まずはお出かけ用の写真をパチリです。

完成しました。

動作テストのために、外付けのトランジスタをとりつけます。今回は汎用のTIP32CTIP31Cをつけています。

Ic=3Aの普通のパワートラです。放熱板にとりつけていますが、本来はケース底面に取り付けるようなことを想定します。

まずは動作確認用に外付けパワトラを取り付けました。

動作確認!

まずは通電して無事動くことを確認しました。部品点数も少ないので、間違うことはあまりないでしょう。

でも、この規模で動かなかったら、ちょっとショックで寝込んでしまうかもしれません(笑)。

動作することがわかれば、VRを調整して出力電圧を3.3Vにあわせてました。

出力電圧の調整です。

つぎは負荷テストです。負荷には4Ωの抵抗をつなげました。2Ω×2個の構成です。

3.3Vで4Ωの負荷ですから電流は約800mA強流れます。ほんとうはもっと流したかったのですが、

元電源の容量の都合からこの値にしました。

負荷抵抗をつないでチェックです。

負荷を接続すると若干ですが電圧が落ちましたが、この程度ならレギュレーションも優秀です。

負荷時の電圧です。約6mV低下ですが、出力抵抗0.01Ω以下ですから優秀です。

さて、この電源基板もマニュアルを作成してリリースしたいとおもいます。

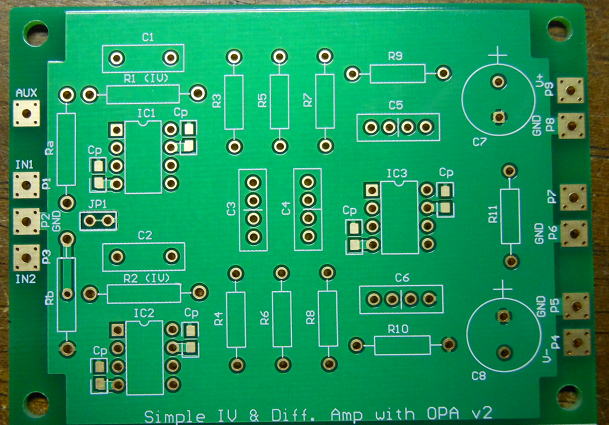

シンプルIV&Diff,amp V2です。

基本はV1基板と同じですが、入力部に若干回路を追加しました。

V2基板です。

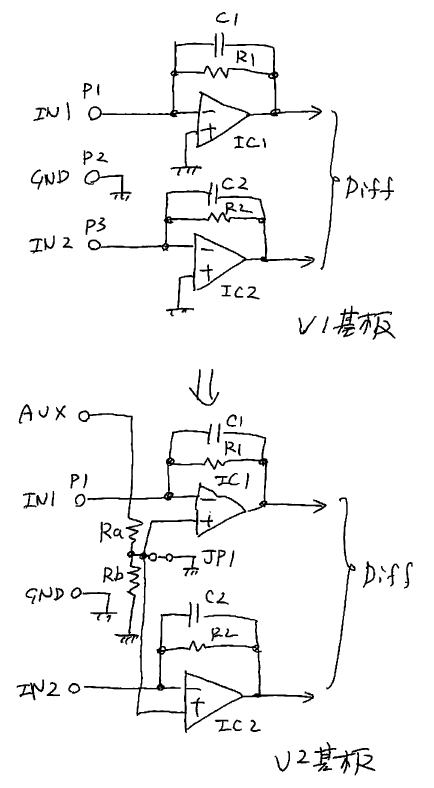

追加の部分は下記のような回路です。とくに意識しなければ従来のV1基板と同じように使うことができます。

V1基板とV2基板の違い。JP1は既定値が接続なので、V1基板と同じように取り扱えます。

変更点はここにまとめました。→ simpleIV-v2.pdf

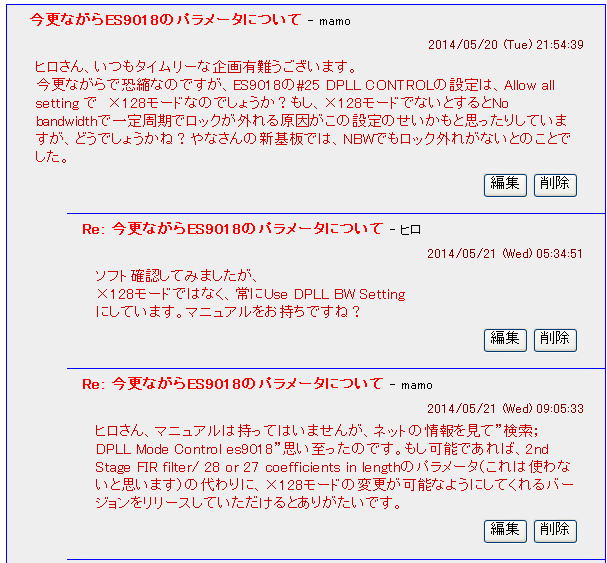

すこしソフトを改造 2014.5.29

こんな投稿をいただきました。

ということで#25レジスターの×128モードを設定できるようなソフトを組んでみました。

ROM容量に余裕がないので、FIR LENGTHの項目を入れ替えました。

まだ自分では試していません。元にもどせるようにオリジナルのバイナリーもアップしました。

| バイナリーファイル | 説明 | |

| 1 | FFDAC9018D_release.HEX | オリジナル版 |

| 2 | FFDAC9018D_128mode.HEX | ×128モードを追加 |

(つづく、かな?)