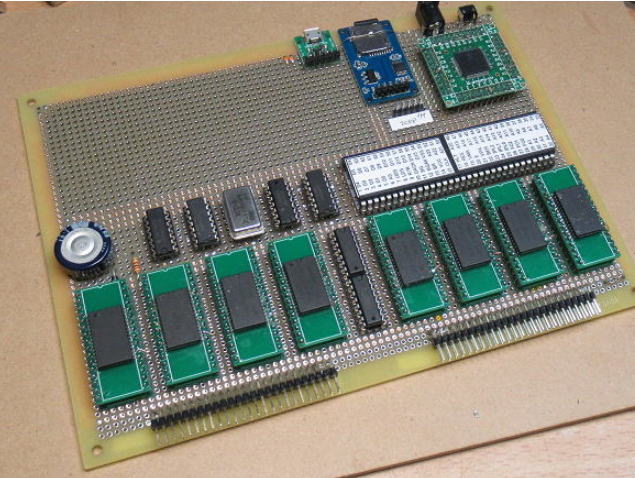

尰嵼偺CPM68K偼PC偐傜撈棫偟偰摦嶌偱偒傞傛偆偵偟偰偄傑偡丅偡側傢偪RS232偱PC偵愙懕偟偰巊梡偡傞偺偱偼側偔丄

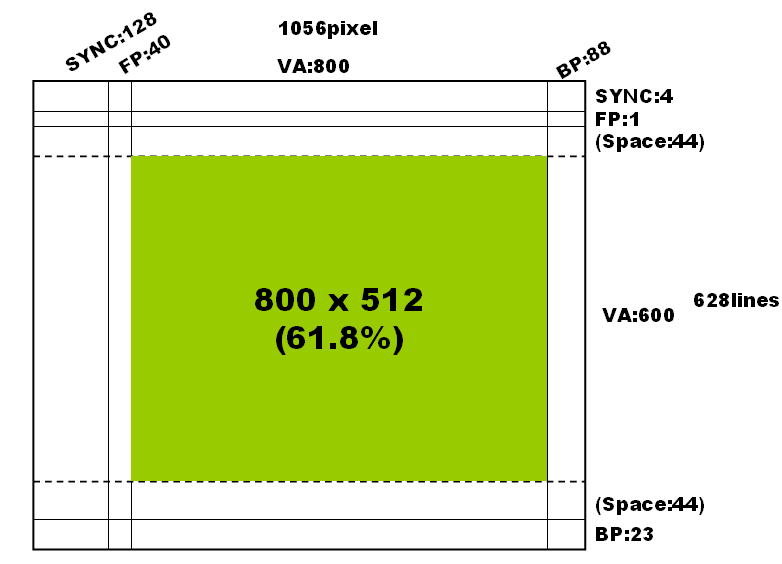

VGA儌僯僞偲僉乕儃乕僪傪愙懕偟偰摦嶌偝偣傞傛偆偵偼側偭偰偄傑偡丅VGA偺婎杮巇條偼800x600偺昞帵婯奿傪偮偐偭偰

800x512Dot偱偮偐偭偰偄傑偡丅偙傟偵昁梫側儊儌儕乕偼512kW(1MB)偲愗傝偺偄偄悢帤偵側傝傑偡丅

堦墳丄撈棫偟偰巊偊傞傛偆偵偟偰偄傞偺偼偄偄偺偱偡偑丄尰嵼偺僌儔僼傿僢僋RAM乮GRAM)偵偼傑偩傑偩寚揰偑偁傝傑偡丅

侾丏GRAM偵彂偒崬傓偲夋柺偵僲僀僘偑惗偠傞

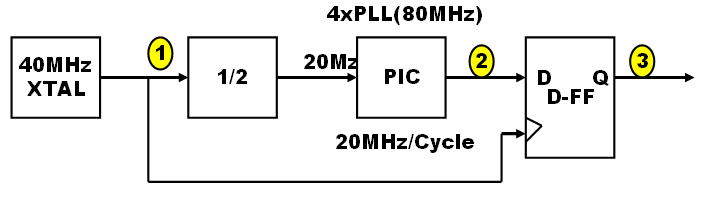

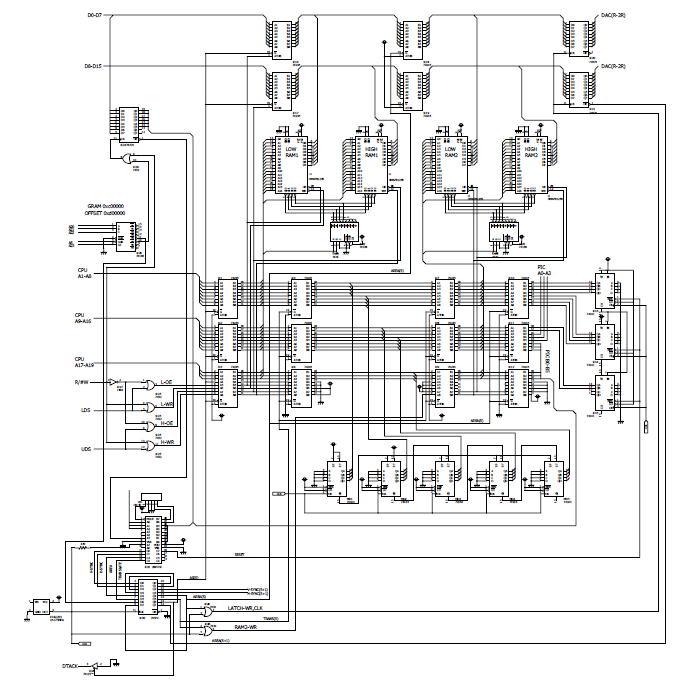

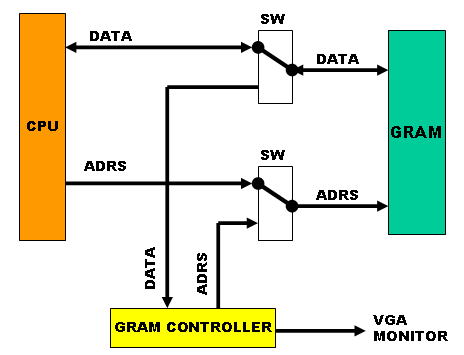

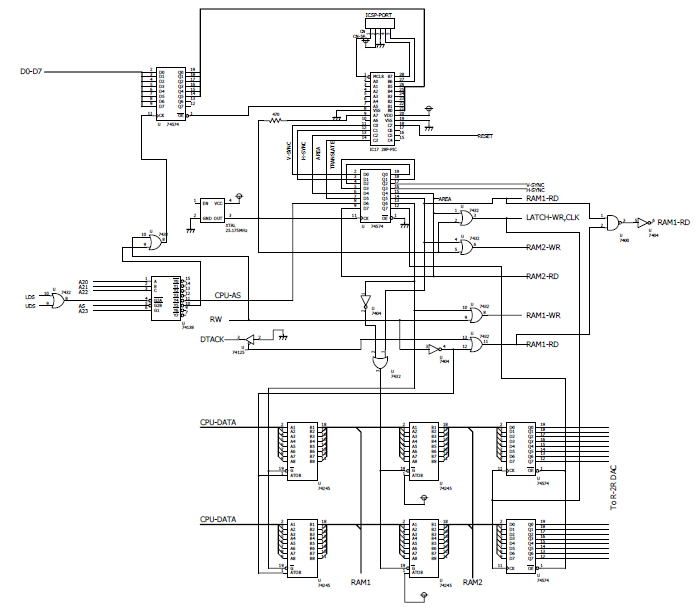

丂尰嵼偺GRAM偺峔憿偼壓恾偺傛偆偵側偭偰偄傑偡丅偙偺偨傔RAM偵彂偒崬傓偲偒偵偼丄昤夋偺偨傔偺撉傒弌偟偑偱偒傑偣傫丅

丂偦偺偨傔丄昤夋偺嵟拞偵RAM傪傾僋僙僗偡傞偲夋柺偵僠儔僠儔偲僲僀僘偑偱偰偟傑偄傑偡丅GRAM傊偺傾僋僙僗偼CPU懁偑桪愭側偺偱

丂偄偨偟偐偨偁傝傑偣傫丅僲僀僘傪梷偊傞偨傔偵偼丄昤夋埲奜偺帪娫懷丄偡側傢偪VGA怣崋偺悈暯偁傞偄偼悅捈偺婣慄帪偵

丂偵CPU偐傜RAM偵傾僋僙僗偡傞昁梫偑偁傝傑偡丅

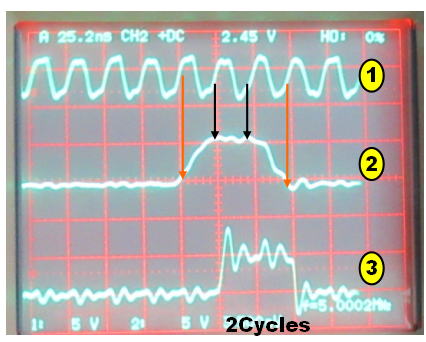

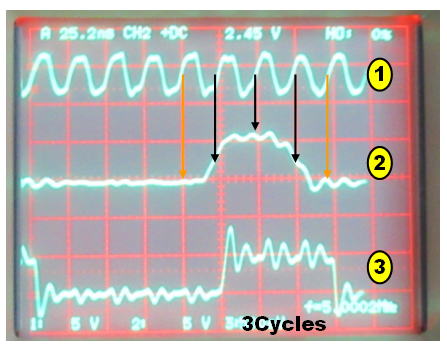

尰嵼偺僌儔僼傿僢僋儃乕僪偺峔惉丅傾僋僙僗偼CPU桪愭側偺偱丄昤夋拞偵傾僋僙僗偑偁傞偲

夋柺偵僠儔僣僉僲僀僘偑偱傑偡丅

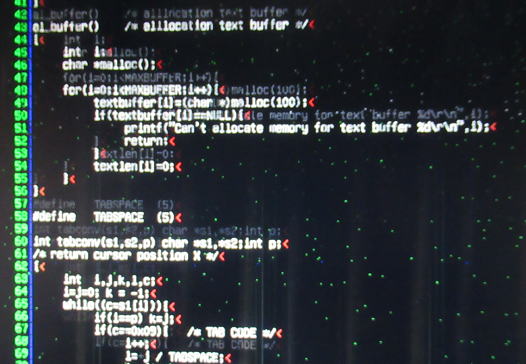

僗僋儕乕儞僄僨傿僞乕偱僗僋儘乕儖偟偰偄傞偲偒偺夋柺丅夋柺偵僲僀僘偑偱偰偟傑偄傑偡丅

俀丏僲僀僘傪梷偊傞偲昤夋懍搙偑抶偔側傞

丂夋柺偺僠儔僠儔僲僀僘傪梷惂偡傞偵偼丄昤夋埲奜偺僞僀儈儞僌偱GRAM偵傾僋僙僗傪偡傞傛偆偵偟側偗傟偽偄偗傑偣傫偑丄

丂偙傟傪峴偆偲丄摦嶌懍搙偑嬌抂偵掅壓偟傑偡丅偲偄偆偺傕昤夋偺帪娫妱崌偼慡懱偺俇妱嫮偵側傞偺偱丄斀懳偵

丂巆傝偺係妱庛偺帪娫懷偟偐RAM傊偺傾僋僙僗偑偱偒傑偣傫丅昤夋婜娫拞偼GRAM傊偺傾僋僙僗傪懸偨偣傞昁梫偑偁傝傑偡丅

丂梫偼僠儔偮偒僲僀僘傪梷偊傞偲丄昤夋懍搙偑1/3掱搙傑偱棊偪偰偟傑偄傑偡丅偄傗丄幚嵺偵偼傕偭偲棊偪崬傫偱偄傑偡丅

丂丂偲偄偆偺傕摉弶偼CPU偑RAM偵傾僋僙僗傪偟偨偲偒偵昤夋拞側傜CPU偵HALT傪偐偗傞傛偆偵偟偨偺偱偡偑丄

丂偙傟偑戝幐攕偱偟偨丅CPU偵HALT傪偐偗傞偲丄僶僗偺抣偑搑拞偱偲傑傞偺偱僠儔僠儔僲僀僘偱偼側偔偰

丂夋柺偺昞帵偑徚偊偰偟傑偄傑偡丅偙傟偼僠儔偮偒埲忋偵夋柺偑棎傟偰偟傑偄傑偡丅

丂丂偦偺偨傔丄摨婜怣崋偑偱偰偄傞娫傪僾儘僌儔儉偱億乕儕儞僌偟偰GRAM偵彂偒崬傓傛偆偵偟偨偺偱偡偑丄偙傟偑抶偄丅

丂傕偪傠傫夋柺偺僲僀僘偑徚偊傑偟偨偑丄昤夋懍搙偑HALT傪偐偗傞傛傝偝傜偵抶偔側傝傑偟偨丅偲偄偆偺傕丄僜僼僩僂僄傾

丂偱億乕儕儞僌偟偰偄傞偺偱丄侾揰昤夋偡傞娫偵偵俀侽僋儘僢僋掱搙偺柦椷傪梋暘偵幚峴偟偰偄傑偡丅栺1us掱搙偺帪娫儘僗偱偡丅

丂偙傟偑慡夋柺偵側傞偲栺0.5倱偑捛壛偱偐偐傞偙偲偵側傝傑偡丅

丂丂懱姶揑偵僗僋儕乕儞僄僨傿僞乕傪摦偐偟偰傒傞偲丄峴偺憓擖傗嶍彍傪偍偙側偆偲偐側傝撦偔偰丄偪傚偆偳9600b偔傜偄偺

丂RS232偱摦偔抂枛掱搙偺懍搙偵側偭偰偟傑偄傑偡丅偙偺懍搙偼僉儍儔僋僞乕昞帵偩偗偱偼側偔僌儔僼傿僢僋昞帵傕摨條偱偡丅

丂丂偦偺偨傔丄尰嵼偼懍搙傪桪愭偟偰丄僠儔偮偒僲僀僘傪嫋梕偟偰偮偐偭偰偄傑偡丅傑偁丄僲僀僘傕婥偵偟側傟偽偄偄偺偱偡偑丄

丂婥偵偟偩偡偲婥偵側偭偰偟傑偄傑偡丅

俉侽侽x俇侽侽偺VGA昤夋僞僀儈儞僌丅慡懱偵愯傔傞夋柺昤夋偼俇妱嫮偵側傞偺偱丄偦傟埲奜偺僞僀儈儞僌偱偺傒

傾僋僙僗偟傛偆偲偡傟偽慡懱偺僗儖乕僾僢僩偑棊偪傑偡丅

俁丏怓偵傓傜偑偱傞

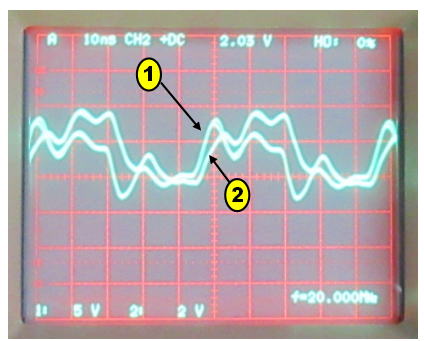

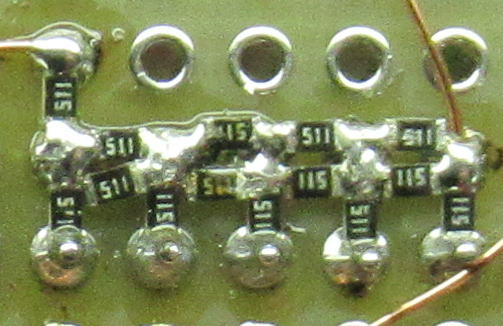

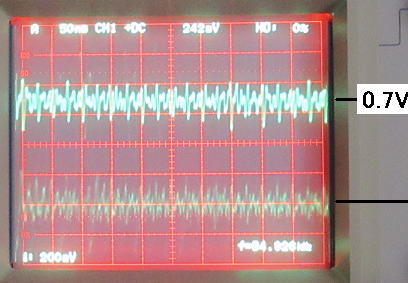

丂丂GRAM偺怓忣曬偼侾俇價僢僩側偺偱65k怓偵側傝傑偡丅RGB偵偦傟偧傟丄俆丆俇丆俆價僢僩傪妱傝摉偰偰R-2R偺DAC偱傾僫儘僌

丂弌椡偲偟偰偄傑偡偑丄揹尮儔僀儞偺僲僀僘傗怣崋慄偺僲僀僘偑儘僕僢僋夞楬偺弌椡偵廳忯偡傞偺偱丄偦傟偵塭嬁傪庴偗偰

丂傾僫儘僌弌椡偵僲僀僘偑忔偭偰偄傑偡丅偙傟偑怓傓傜偺尨場偵側偭偰偄傑偡丅

丂丂偪傚偆偳丄恀偭崟偵昞帵偝偣偨応崌偵偼敄偄慄忬偺儉儔偑尒偊傑偡丅斀懳偵恀偭敀偵昞帵偝偣偨応崌偵偱傕丄偲偙傠偳偙傠

丂偱怓偺敄偄偲偙傠偑偱偰偄傑偡丅傑偁丄敀崟偺僉儍儔僋僞乕昞帵偩偗側傜丄偲偔偵婥偵側傞傕偺偱偼偁傝傑偣傫偑丄

丂偱傕丄偙傟傕婥偵偟偩偡偲婥偵側傝傑偡丅

丂丂丂

VGA偺怣崋儔僀儞偵偼僲僀僘偑偐側傝忔偭偰偄傑偡丅

丂

丂

VGA怣崋偵廳忯偟偨僲僀僘偑怓傓傜偲側偭偰偱偰偟傑偄傑偡丅

忋婰偺傛偆偵丄尰忬偺GRAM偵偼偄偔偮偐偺壽戣偑偁傝傑偡丅

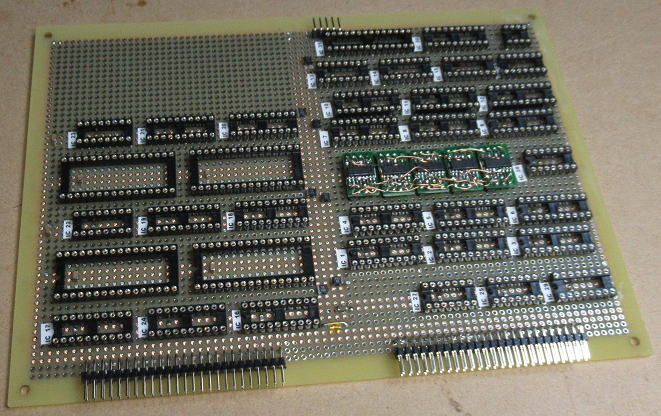

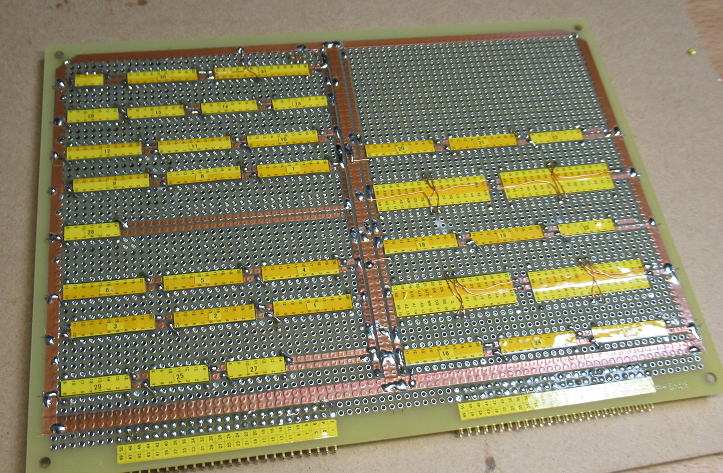

偦偙偱懳嶔偲偟偰丄壓婰偺婡擻傪捛壛偟偨怴偟偄僌儔僼傿僢僋儃乕僪傪専摙拞偱偡丅

懳嶔偼偳偆偡傞偐丠

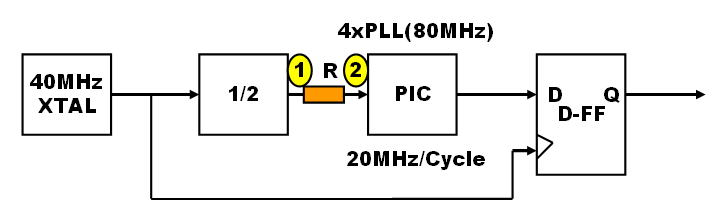

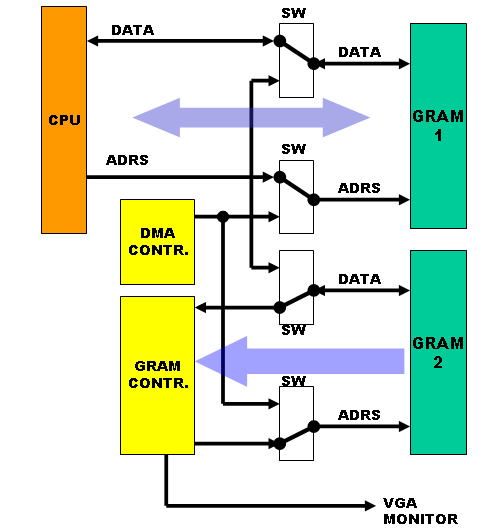

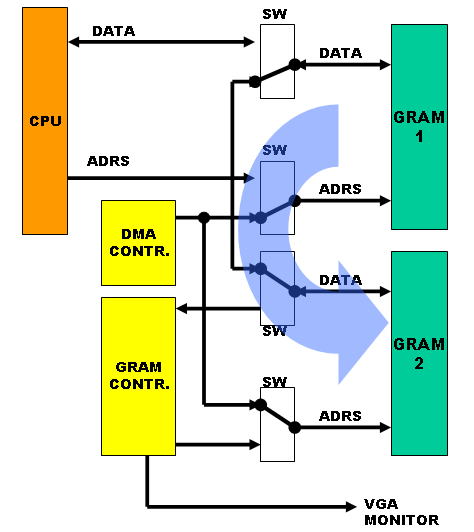

侾丏GRAM傪俀宯摑梡堄偡傞丅

丂CPU偐傜偼撉傒彂偒偡傞GRAM侾偲丄昤夋偺偨傔偺GRAM俀傪暘棧偟偰撈棫摦嶌偝偣傞傛偆偵偟傑偡丅偦偆偡傟偼丄CPU偐傜偺GRAM傾僋僙僗

拞偵昤夋傪巭傔傞昁梫偼偁傝傑偣傫丅偦偟偰丄GRAM1偐傜GRAM2傊偼悈暯偲悅捈婣慄偺抁偄帪娫偱崅懍偵僨乕僞揮憲傪峴偆傛偆偵偟傑偡丅

丂僨乕僞揮憲偺偨傔偺僋儘僢僋傪昤夋僋儘僢僋偲摨偠係侽MH倸偵愝掕偡傞偲丄512kW偺儊儌儕乕揮憲懍搙偼

丂栺80Hz偱峴偊傑偡丅偨偩偟丄揮憲偵偐偗傜傟傞帪娫偼昤夋埲奜偺帪娫偱偡偐傜丄妱偗傞帪娫偼慡懱偺38亾偱偡丅

丂偡側傢偪80x0.38亖31俫倸掱搙偱慡懱偺僨乕僞偑揮憲偱偒傑偡偺偱丄傎偲傫偳帪娫抶傟偼姶偠傞偙偲偼側偄偼偢偱偡丅

丂丂GRAM1偐傜GRAM俀傊偺僨乕僞揮憲拞偵丄CPU偐傜GRAM1傪傾僋僙僗偡傞応崌偵偼丄摉慠CPU懁偑桪愭側偺偱丄僨乕僞揮憲傪拞抐

丂偟側偗傟偽側傝傑偣傫偺偱丄偦偺娫偼GRAM2忋偺屆偄僨乕僞偑昞帵偝傟傞偲偄偆偙偲偵側傝傑偡偑1/30s屻偵偼僨乕僞偑彂偒姺偊傜傟傞

偙偲偵側傞偼偢偱偡偐傜丄堘榓姶偼側偄偼偢偱偡丅

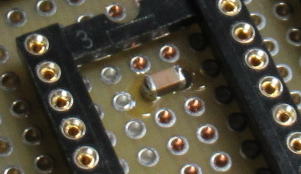

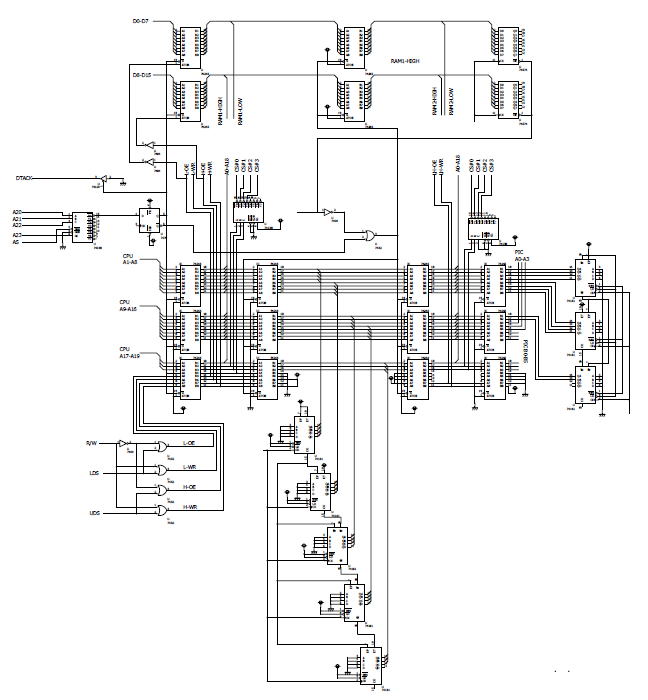

丂偙傟傪幚尰偡傞偵偼GRAM偼俀僙僢僩昁梫偵側傝丄傑偨僨乕僞偺揮憲夞楬偑昁梫偵側傝傑偡丅晹昳揰悢偼懡偔側傝傑偡偑

夞楬揑偵偼偁傑傝擄偟偄傕偺偱偼側偄偼偢偱偡丅

丂偙傟偱懍搙偲僲僀僘偼椉柺偱夝寛偱偒傑偡丅

RAM傪俀宯摑梡堄偟偰丄昤夋拞偵傕CPU偐傜RAM偵傾僋僙僗偱偒傞傛偆偵偟傑偡丅

昤夋埲奜偺僞僀儈儞僌乮悈暯摨婜丄悅捈摨婜拞乯偵GRAM1偐傜GRAM俀偵僨乕僞傪

揮憲偟傑偡丅揮憲拞偵CPU偐傜偺GRAM1傊偺傾僋僙僗偑偁傟偽丄偦偪傜偑桪愭偱

偦偺娫偼僨乕僞揮憲傪堦扷拞抐偟傑偡丅

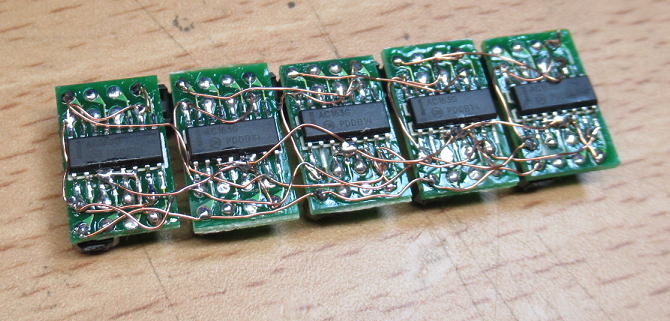

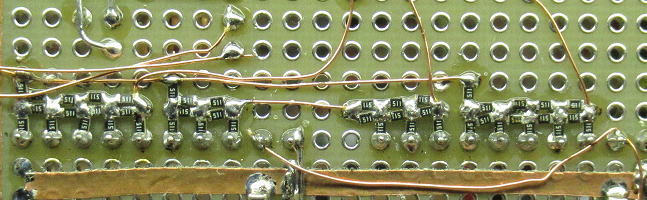

俀丏DAC偼暿揹尮偱摦嶌偝偣傞

丂尰忬偺VGA傾僫儘僌弌椡偲側傞R-2RDAC偺儘僕僢僋IC偼揹尮儔僀儞(5V)偱摦偄偰偄傑偡偑丄揹尮揹埑偺曄摦偑偁傞偺偱偦偺塭嬁傪

丂偆偗偵偔偔偡傞偨傔偵丄俆V偐傜3.3V偵揹尮傪曄峏偱偡丅揹埑崀埑偵儗僊儏儗乕僞傪偮偐偄傑偡偺偱丄偦偺儗僊儏儗乕僞偵偰

崅廃攇揹埑曄摦偑梷惂偝傟偰揹尮揹埑偺曄摦偑彫偝偔側傞偼偢偱偡丅傑偨丄怣崋儔僀儞偺揹埑傪曄摦傪梷偊傞偨傔偵

堦扷丄3.3V偱摦嶌偝偣傞儘僕僢僋IC傪娫偵憓擖偡傞梊掕偱偡丅丂丂

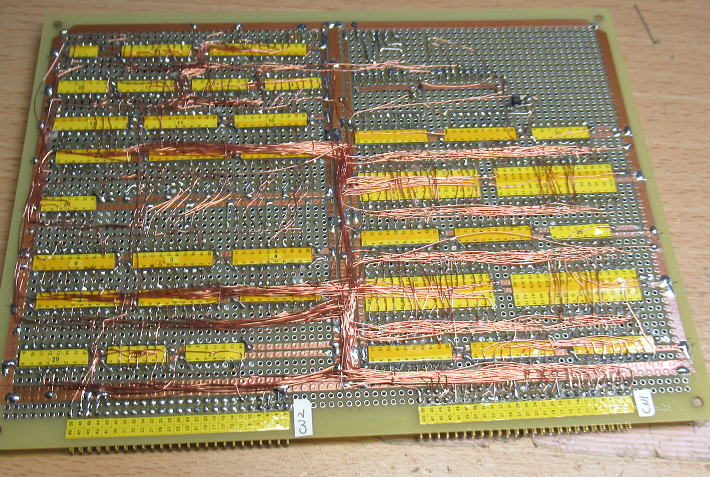

夞楬恾傪峫偊偰傒傞

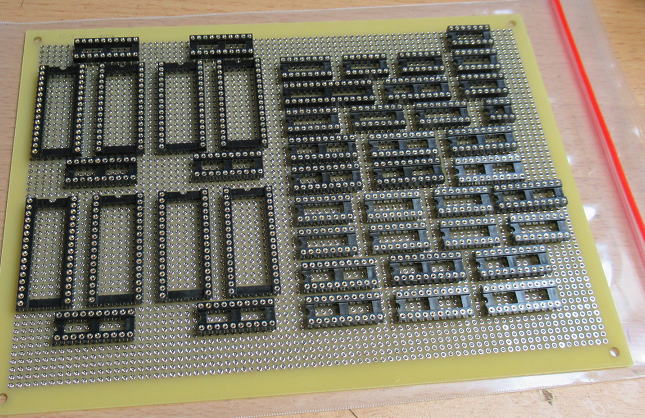

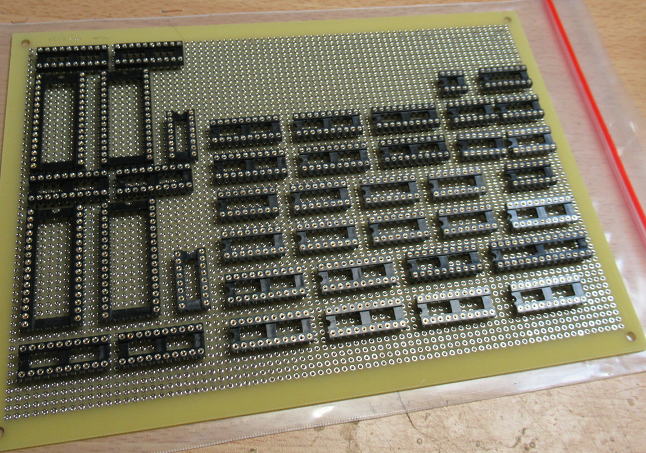

傑偢丄昁梫偵側傝偦偆側IC偺悢傕尒愊傕傞偨傔偵傕娙扨偵夞楬傪昤偄偰傒傑偟偨丅

戝偒偔側傝偦偆側偺偱丄僐儞僩儘乕儖晹暘偲愗懼晹暘傪暘偗偰峫偊偰偄偒傑偡丅

僐儞僩儘乕儖晹暘傪拞怱偵夞楬傪専摙偱偡丅

丂

丂愗懼晹暘傪拞怱偵夞楬傪専摙偱偡丅

昁梫側IC悢偼

夞楬恾偐傜昁梫側IC悢偱偡偑偙偺偔傜偄偵側傝偦偆偱偡丅