メモリーバッファー考 2007.6.13

メーカ製単体DACには今後標準か!

単体のDACにはディジタル信号を一旦メモリにバッファーしたのち、

外部の水晶発振器で正確に送り出す機能がついているものがあります。

たとえば、DAC1794-3の検討のトリガーになったようなSOUL NOTEの DC1.0

やレイオーディオなど(これはKsさんに教えてもらいました)。

これはSOUL NOTEのカタログから抜粋。ref:http://www.kcsr.co.jp/soulnote/products/dc1.pdf

ref:http://www.reyaudio.com/R-DAC.html

オーディオ雑誌を買っていれば、メモリーバッファー機能をもったDACについては

もっといろいろな機種が列挙できるでしょう。

でもたまにしかオーディオ・サウンド誌かオーディオ・アクセサリー誌くらいしか買わないので、

知っているのはこれだけです。どちらも教えてもらった情報ですね(汗)。

ちなみに、定期的に購読しているのはトラ技(トランジスタ技術)だけです。

昔はインターフェイスも購読していたけど、記事がソフトばっかりになってから

やめちゃいました(随分昔の話しです)。

話はもどってメモリーバッファーは確かによい方法です。

自分的にはその延長線上にあるとおもっているHDオーディオがもっと市場に出てもよいかと思っているのですが、

ピュアーオーディオの世界では出ないですね。やっぱりCDの内容をHDDに転送するのが面倒なので、売れないんでしょうか。

ひょっとして著作権の問題がからんでいるのかな(コピーしてCDを売却する人が一杯でそうです)。

アマチュアは非同期リクロック!?

さて、CDPの信号を正確にする手法としてアマチュアの中では非同期リクロックというものがあります。

これはDAIからの信号であるDATA,BCK、LRCKの信号をさらに周波数の高いクロックで整列させるものです。

これは、私も試したことはありますが、リクロックそのもので音が大きく変わったことは残念ながら感じ取れませんでした。

このリクロックの効果を定量的にみていくと、面白いものがあります。

リクロックでどの程度、ジッタが減るか計算してみましょう。

その前に、市販のDAIのジッタ性能をちょっと列挙してみます。

| 型名 |

メーカ |

ジッタ(ps) |

| DIR9001 |

Texas Instrument |

50 |

| DIR1703 |

ITexas Instrument |

75 |

| CS8146 |

シーラスロジック |

200 |

カタログ性能だけ見れば、DIR9001がもっともよいのですが、その他のDAIでも十分な性能をもっていると思います。

ポイントはリクロックでこれらのジッタを下回るかどうかです。

BCKを80MHzでリクロックした場合を考えましょう。

BCKは64fsな場合が多いので、サンプル周波数が44.1kHzの場合はBCK=2.8224MHzになります。

時間間隔にすれば354.3nSです。

一方リクロックに80MHzを用いた場合時間間隔は12.5nSですから、

BCK信号の間隔はリクロックすれば12.5nSの倍数になるので350nSあるいは362.5nSになります。

すなわちリクロックすることによりBCKは350nSと362.5nSで頻繁に切り替わることになります。

その頻度は350nSが2回あって次に362.5nSが1回くるような頻度になるでしょう。

これを標準偏差にすると6000pS(6nS)くらいですから、

リクロックにより一般のDAIに比べて1〜2桁以上ジッタが増えることになります。

では、リクロックは不要か?と言われればそれはNOだと思います。リクロックにより「音が良い」方向に進むのであれば、

それは結果として成功です。物理特性と音質が対応しないところが、オーディオの面白い所であり、かつ難しい所です。

でも理論的にもジッタが増えるのは音の結果がよくても、すこし気になるところです。

やっぱりジッタを解消する方法としてのメモリーバッファーは気になる存在です。

メモリーバッファーに必要な容量は?

気になる点はバッファーにどれくらいの容量がいるか?ということです。

演奏の途中でメモリーが一杯になって音が途切れるようではいけません。

1枚のCDの演奏は連続で鳴って欲しいものです。さて、ちょっと計算してみましょう。

まず、重要な数値はSPDIFの規格でどこまで周波数のずれを許容しているかですが、

規格がどこにあるかわからなかったので適当に0.1%(1/1000)をサンプリング周波数の誤差として

考えて見ましょう。

この数値を出した根拠はあまりありませんが、水晶の温度発振精度が100ppm(3℃)なので、

実用上の温度範囲だったら1000ppm程度は狂うだろうと推定しました。

44.1kHzでCDPのサンプリング周波数が高い場合

CDPの周波数が44.14kHzでDACの送り出し周波数が44.06kHzとしましょう。

ちょうど、80Hzの差です。これにCDの演奏時間(70分?)をかければバッファーが必要なでてきます。

溜める必要のあるデータ個数は80(Hz)×70(分)×60(秒)=336k個になります。

1個のデータには左右とビット長32Bitがありますから、容量(バイト)としては

336k×2×32/8=2.688MByteになります。かなり大きな容量ですが、

最近のメモリであれば1チップでカバーできる容量でしょうか。まあ、とくにコストが

どうのこうのということはなさそうです。

さて、表題であげた「メモリーオーディオ考」のきっかけは、実は逆の話しで

CDPの方が周波数がおそかったどうなるか?

です。たとえば同じように0.1%(1000ppm)の誤差があるとしてCDPが44.06kHzでDACが44.14kHzの場合です。

DACはデータが貯まらない状態でも、信号を送り出す必要がありますから、

途中どこかでデータの欠落(あるいは前と同じデータの送出)が生じます。

これは問題ない(メモリーにデータが溜まるのでオーバフローは要注意)

CDP側の周波数が遅いとデータのダブりがでてくる。

データが1度欠落してしまえば、しばらく送出するデータには(1個ずれますが)余裕が出ます。

上記の誤差(0.1%)だと、おおよそ500データに1回はデータが欠落することになります。

周波数にすれば400/44.1k=10mS(100Hz)になります。ちょっと頻度が高いですね。

データの欠落を防ぐためには?

これを防ぐためには、あらかじめデータを一定期間だけバッファリングすればよさそうに感じますが、

あまり長い時間をバッファリングするようだと操作性もわるくなってしまいます。

ながくても1秒が限界でしょう。では、この1秒のバッファリングができれば、どのくらいバッファーが機能

(データの欠落がなくなる)するかですが、計算上は500秒は大丈夫になります。

とはいえ10分弱です。CD1枚を演奏した場合、最初の20%弱はメモリーの効果がでていても、

それ以降はやはり500回に1回はデータが欠落する状態に陥ってしいまいます。

CD1枚分をバッファーを効かそうすれば、タイムラグは10秒近く必要です。これでは使い物になりません。

曲間移動で10秒も音がでなければ、「故障?」とおもっちゃいますからね。

さて、結局この問題を解決する方法ってメーカではどうやっているのか、とても興味のあるところです。

500回に1回程度のデータ欠落は気にしない、のでしょうか?

ただし、500回という数字は0.1%という水晶発振精度の場合ですから、

実力的にはその1-2桁は下でしょう。5000回に1回、あるいは50000回に1回程度のデータ欠落なら許容して

いるのかもしれません。

5,000回に一回ということは約0.12秒に1回程度のデータ欠落(誤差)です。周波数で8Hz程度ですから、

可聴域を下回る領域なのでひょっとして気にすることは無いのかもしれません。

ひょっとして?

あるいは、もっとも簡単な対処方法はDACの送出周波数をあらかじめ44.06kHzなどの規定値よりも遅くしているかもしれません。

そうすればバッファーが途切れることはありません。これについては、CDを1枚分演奏してみて、

どのくらいの時間ずれが生じているかを計ってみればどのくらいの周波数精度があるかわかりますね。

もし、DACを通したほうが遅い(CDの演奏が終わってからも音がでている)のならDACのほうが周波数が低い。

同時に終わればDACとCDPが同じか、あるいはCDPが速いことになります。

メモリーバッファーをどうやって構築するの?

メーカ製のものは1チップのコントローラ(メモリは別)で動かしているようです。

アマチュアがつくる場合でも、CPLDやFPGAなどを使えば実現できるのでしょう。

でも、これをするには記述言語の知識・活用技術もいるのでおいそれとは(すくなくとも私は)手がでません。

マイコンをつかうのも1つの方法でしょうが、ちょっと速度的に難しいような気がします。

やっぱり、もっている知識で対応しようろすればハードロジックだけになっちゃいますが、

これで組めるのかな?(自分にとっては壮大な試みだな−。実現の確率は1%くらい?)。

検討再開?2007.6.19

DAC1794-3の動作確認ならびに必要部品の発注作業も終わりひと段落。

いや、発送準備ならびに発送という最大の山場が残っているが、

しばしの間、メモリーバッファーについての思考を再開。

さて、いろいろとBBSにても意見をいただきましたが、

雰囲気的にはアンダーバッファーについては考慮していないようです。

SOULENOTEもメモリーが半分たまった時点で送出を開始しているようですしね。

送出までの時間が長いと使い勝手が悪いので、タイムらぐは0.1〜0.2sec程度でしょうか。

ということは0.4秒程度のバッファーがあれば十分なような気がします。

となるとメモリー容量は44.1kHzで0.4秒蓄えられるとすればデータ数は約17k個になります。

1データは左右×32bitの8バイトになりますから17k×8=136kByte。

まあ切りよい数字とすれば128kByte、すなわち1MBitのメモリがあれば十分なような気がします。

1枚のCDで0.2secのずれが生じるための水晶の精度は演奏時間70分とすれば

0.2/(70×60)=4.8×10E-5です。

すなわち48ppm以下の精度であればいいわけですが、水晶発振子の周波数確度をみていると

だいたい50ppmくらいのようですから、大丈夫でしょう。

気になるのは自分のつかっているCDPって水晶発振子をつかっているかどうかというところです。

これは一度周波数を計ってみないといけないでしょう。

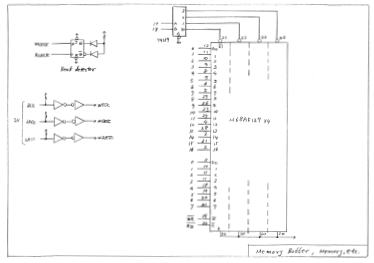

さて、使うメモリー容量が決まりましたので、FIFOを探してみましょう。

いつものようにDIGIKEYでFIFOを検索すると、いろいろとでてきました。

とりあえず、一番容量の大きいものをチェック。1Mbのものがあります。

IC DEEP SYNC FIFO 128KX9 32-PLCC 18,000円

高!なんでこんなに高いの?

1GBのSDカードが2000円程度で買える時代に・・・・・

その他をみてみてみても、ほとんどが「非在庫保有品」ですので、調達するには1000個単位で

納期もかかることが容易に推察されます。

まずは簡単に手にはいるものをつかってテストをしたほうがよさそうです。

ということで、スタティックメモリをつかうことを考えて見ましょう。

ちょうど秋月に5個で500円の1MBのメモリがありました。

M68AF127Bというものらしいです。

ref http://img.akizukidenshi.com/images/org/m68af127b.jpg

1.27mmピッチですから半田付けも簡単です。

マニュアルを探してみると、ありました。→ここ

普通のSRAMですね。しかし、昔に2101(1kB)のものを2000円くらい出して買ったことを考えると涙がでてきます(大袈裟?)

ついでなので10個ほど買ってみましょう。

具体的な制御は 2007.6.22

FPGAやCPLDなどが使えればいいのですが、いかんせんそちらの方には知識がゼロなので、

ここは単純にハードロジックで組んでみましょう。

つかうロジックをすべてDIPでおこなうかSOPでおこなうかはちょっと悩みますが、

それはまず動いてから考えればいいわけで、まずはロジックをどうするか考えましょう。

基本仕様は

1.対応周波数は44.1kHzのみ(48kHz系はスイッチあるいは水晶の切り替えで対応でしょう)。

2.メモリー容量は1Mbitとする。すなわちバッファー時間は0.4秒です。

3.メモリの半分たまった時点でスタートするようにする。スタート時間は0.05,0.1,0.2秒が選べるようにする。

4.メモリーのオーバーフロー、アンダーフローは気にしない。

5.使用するロジックはすべて汎用品とする。

あとはゼロレベルが一定時間続けば、メモリーポインターをクリアする機能もできれば設けましょう。

さて、基本的な仕様がきまったので、ロジックを考えていきます。

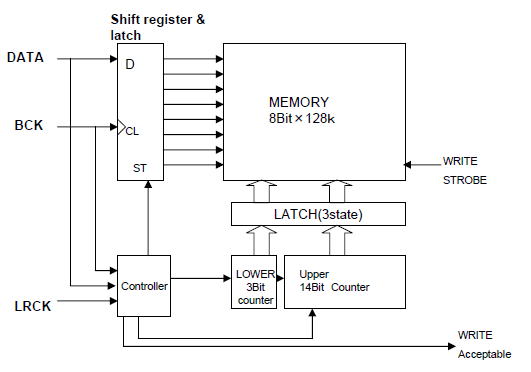

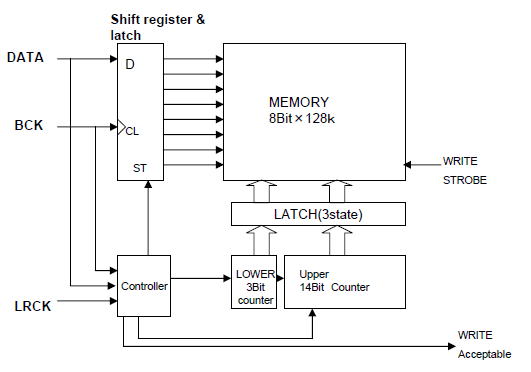

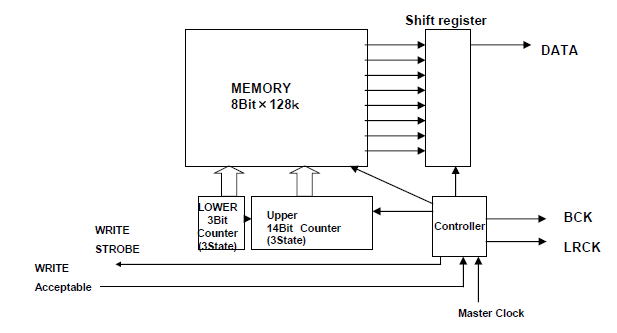

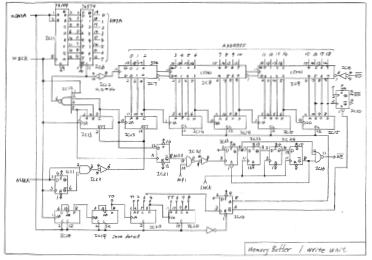

大まかな構成はこんな感じになるでしょう。

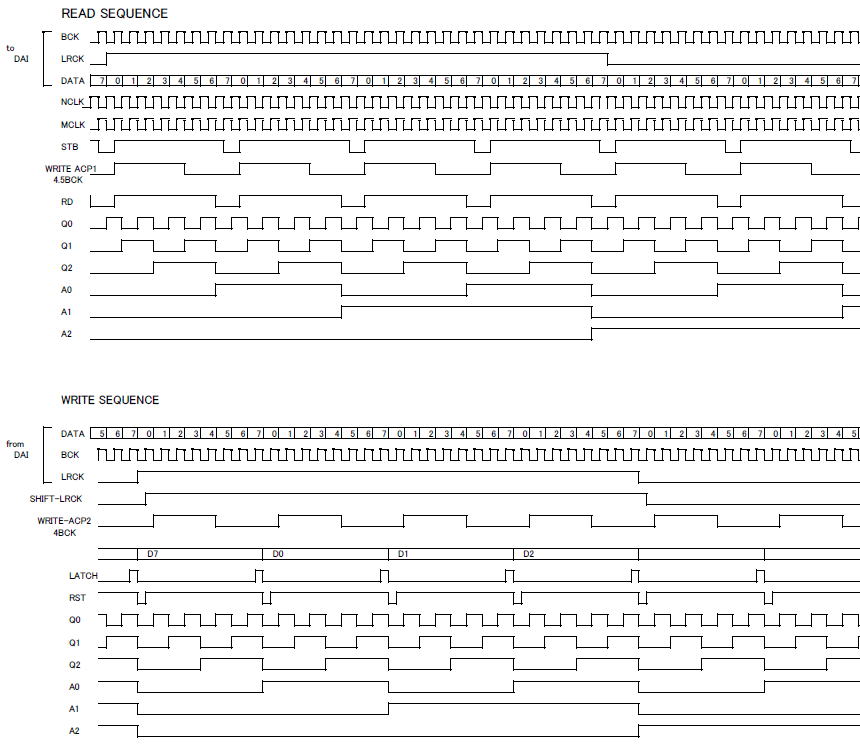

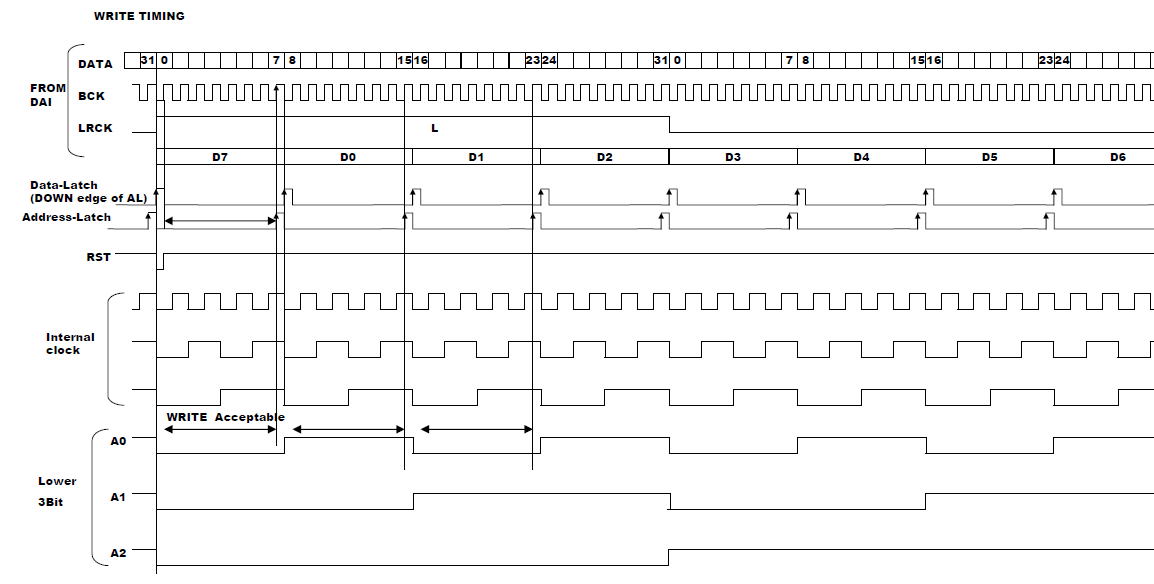

書き込み回路

まずは書き込み回路のみです。

書き込み回路のブロック図。読み出しはこれとはほぼ反対

メモリは8Bit構成なので、シフトレジスタによりシリアルパラレル変換を行います。

メモリーへの書き込みは8ビット単位になるので、4回で左右1セットのデータになります。

シフトレジスタが満杯になった時点でデータを8bit分ラッチするのでメモリに書き込みアドレス値と

ずれますから、アドレス値もラッチしておきます。

書き込みで気をつけなければいけない点は、読み出しと干渉しないようにしなければなりません。

そのため、書き出しタイミング自体は読み出し側で作成します。ただし、書き込みを許可するための

信号を読み出しタイミング側に教えてやる必要があります。

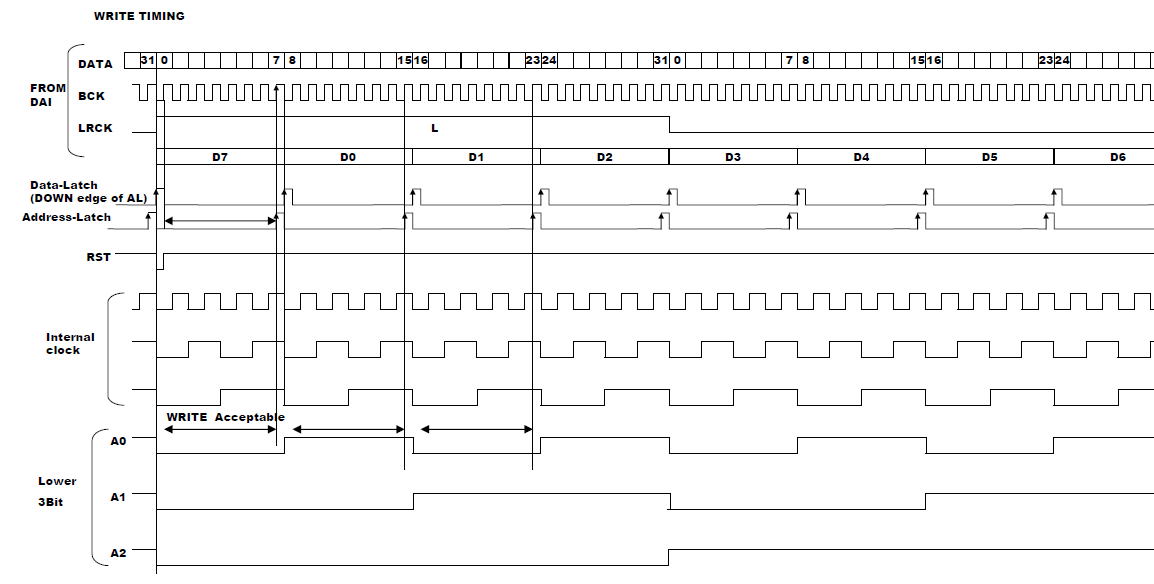

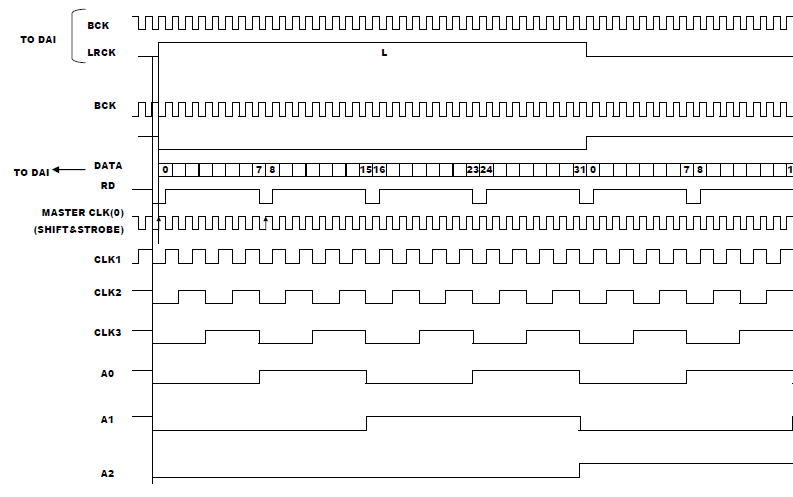

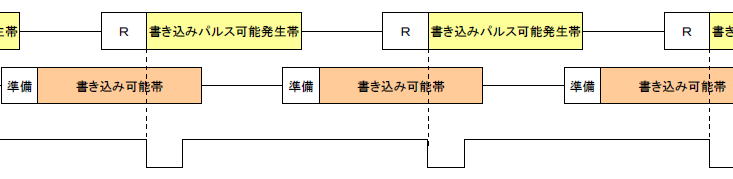

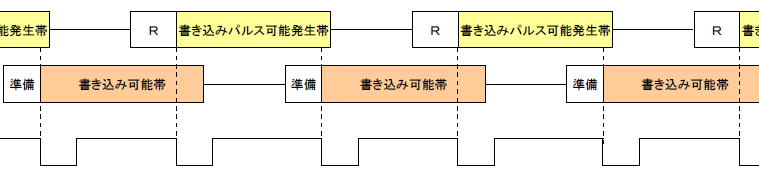

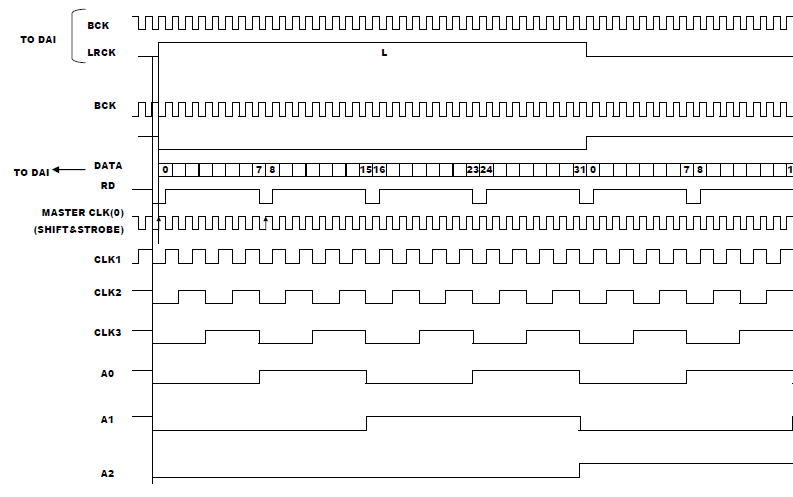

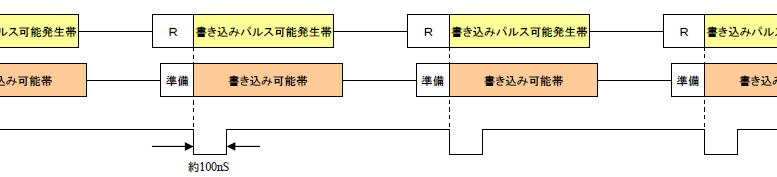

書き込み側のタイミング

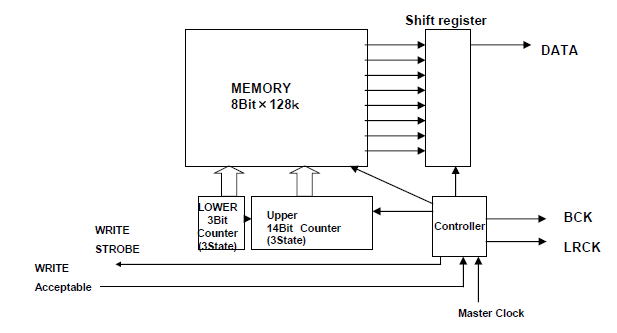

読み出し回路

基本的には書き出し回路の反対です。こちらの方がロジックとしてはスッキリするはずです。

読み出し回路のブロック図。

読み出し側の基本タイミング

ゼロ検出

データが一定期間ゼロが続けば、メモリーをリセットする回路も必要でしょう。

これについてはDAI側にまかせるのがよさそうですが、DIR9001やCS8416にZERO検出はあったかな?

ロジックでZERO検出をしようとすれば、ウオッチドドッグタイマみたいなものを用意すればいいでしょう。

BCKでゼロ以外の数値が入ればリセットをかけて、それ以外ならインクリメントをおこなって、

一定数値を超えればリセットシグナルを発します。

簡単にするためにも256bit分(4データ連続でゼロがつづけば)リセットをかけることかな。

192kHzって・・・・!!!!!2007.6.26

| 7367 |

FIFO |

小林 - 2007/06/24 12:23 - |

(中略)

あとサンプリングレートですが44.1Khzこていではなく44.1khzから192khzまで対応できないでしょうか。

もちろん自動対応では 難しいと思いますので、それぞれ製作者がサンプリングレートを

決めれるようにしておけばよいと思います。これなら少しの変更

で対応できそう。

|

|

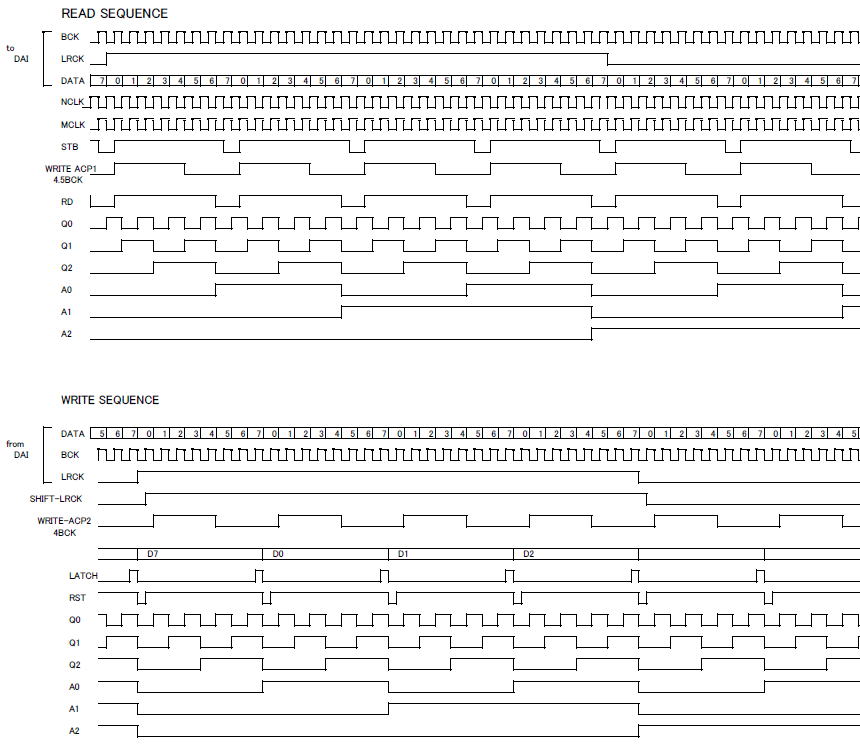

これは半分予想外。44.1kHzで設計していたので、のんびりしたタイミングチャートですから1/2BCKがアクセスタイムになっています。

ちょうど44.1kHzでは1/2Bck幅は177nSですから、いまどきのSRAMでは余裕の時間です。

でも192kHzになると45nSですからね。今使おうと思っているSRAMは55nSなのでSRAMのオーバスペックに期待しないと・・・・・・

| 7378 |

Re: 7369 |

上野@足立区 - 2007/06/26 00:43 - |

192kHzでは、1秒間に左右2chの24bitデータが192*1000(kHz)回到着して、それぞれの24bitデータで読み出しと書き込みが3回ずつですので、10^9(ns)/(192*1000)/2/(2*3)=434(ns)で55ns品のSRAMでも間に合いそうですが。

(略) |

|

いろんなコメントが入ってきます。

CS8416の出力は32Bitなので、上記の計算(434nS)よりすこし短くなって325nSになりますが、それでもSRAMのアクセスタイムの55nSより

はるかに単純計算では時間が取れることになります。

それができるなら、まるで税金が引かれずに額面通りボーナスが出る感じなんだけど・・・・(笑)。

#ちなみに今日はボーナス日。ルンルン気分で税金を見たら、ゲーという感じ。本来は325nSあるはずだけど、色々引かれて55nSを下回る気分(笑)。

アクセスタイムを今の設計の1/2BCKから1BCK幅(約80nS)には変更できそうですが、本当は他のロジックICの遅延も考えて

余裕面から2BCK(160ns)は欲しいところです。でも、残念ながらそれを確保できるロジックをどうしたら実現できるか苦労しています。

無理矢理実現させようとしたら、ダブルバッファーとかロジックが複雑になりそうです。なにか根本的な間違いをしているかな?

ちなみに、なぜアクセス時間が取れないかというと、だいぶ上の方で書いたけどSRAMへの書き込みと読み出しは排他制御が必要です。

読み出しを優先にロジックを組んで、読み出し時以外に空いた時間に書き込みパルスを生成したいけど、書き込みパルスを発生させる時には

書き込みデータがラッチされて確定していなければなりません。そのため好き勝手に書き込みパルスを生成するわけにはいかないので、

パルスを発生させる期間が限定されて、そのパルス幅も小さくなるはず・・・・・と思っているけれど間違っているのかな?

もっと簡単な方法があったりして。この辺はロジック素人の私としては頭のつかうところです。

ここは、プロのコメントを待ってみましょう(人任せモードです(^^;))。

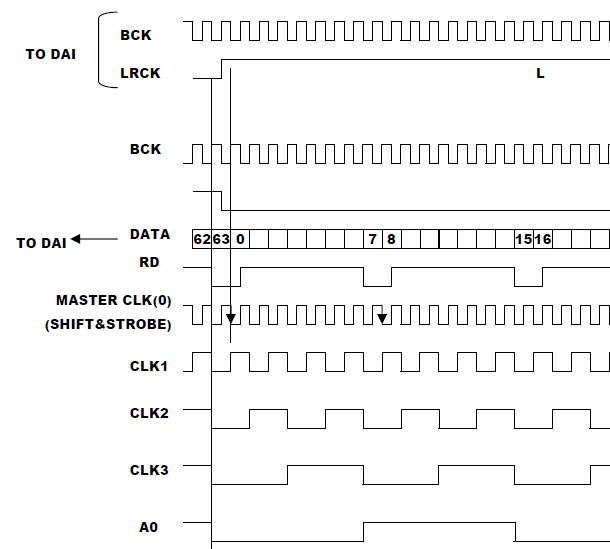

すこしタイミングを変えましょう

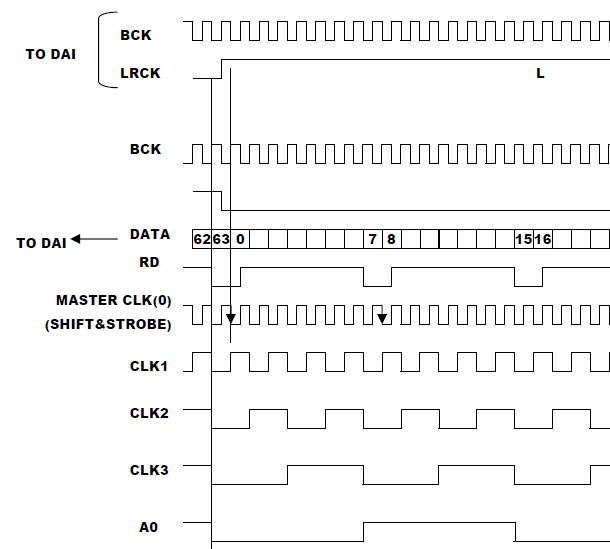

読み出し時のアクセスタイムは前回までは1/2BCKにしていましたが、1BCKまで拡大しましょう。

こうすれば、192kHzでも動作できそうです。

RDパルスを少し長めに設定。あれ、BCKがずれている?まあ、その辺はご愛嬌

もっと長くすれば?

という声も聞こえてきそうですね。RD幅をサイクルタイム(8BCK分)の半分まで長くできそうですが、

そうは単純にはいきません。というのは、あたりまえのことですがSRAM(STATIC

RAM)の書き込み、読み出しにおいて

1)読み出しと書き込みは同時にはできない(排他制御が必要)。

2)書き込み時の終了直前でデータ、アドレスが変わってはいけない。

3)書き込み、読み出しパルスは所定の長さが必要。

を守らないといけません。ふっ、この原則を忘れると、とんでもないミスをやらかしてしまいます。

とくに、よく考えないといけないのは1)排他制御です。

排他制御をどう実現するか

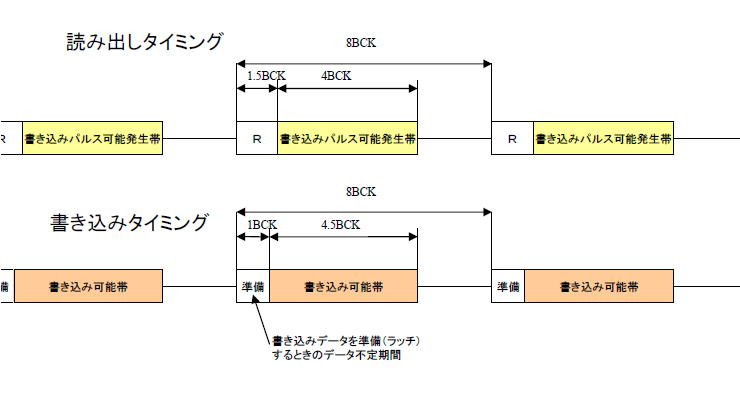

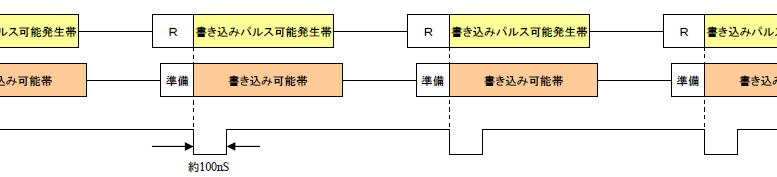

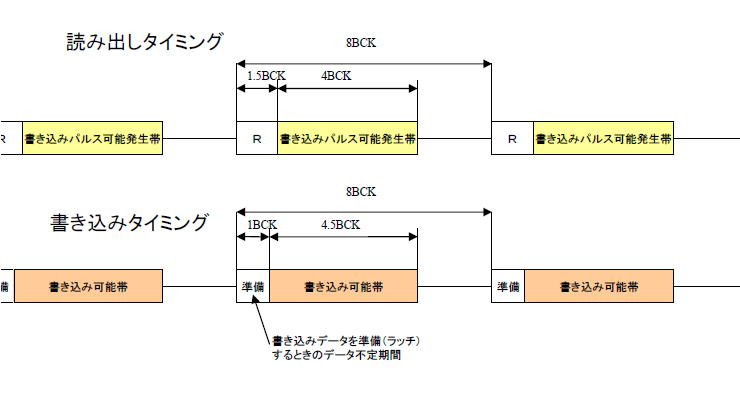

単純にこんな感じで実現しようと思っています。

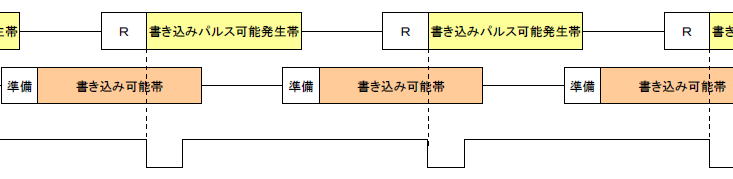

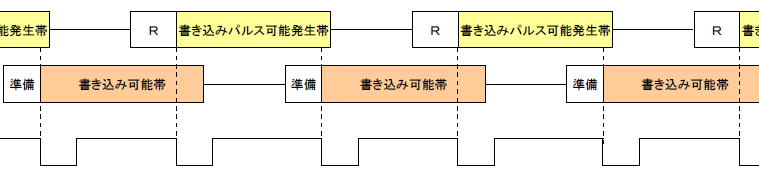

読み出し(R)の後に「書き込みパルス可能発生帯」を設けておきます。この幅は4BCK上にします。

書き込み時にはデータを揃えるときに1BCK程度データの不定な時間が生じますが、その後に「書き込み可能帯」

を設けてます。これは書き込みパルス(WR)がスタートしてもOKな時間帯で、4.5BCKにします。

読み出しと書き込みタイミングの後に設けるWRパルスの発生可能領域。

FIFOの動作において、読み出しと書き込みタイミングはバラバラです。そこで、「書き込みパルス可能発生帯」

と「書き込み可能帯」が両方ともOKなときに、ワンショットなどで100nS程度のWRパルスを発生するようにします。

そのようにすると、下図のようになります。

互いがバラバラになっても、適切なWRパルスを発生することができます。

○CASE1

○CASE2

○CASE3

なお、下図のような場合も当然あります。すなわちWRパルスが2回発生する場合も起こりますが、

メモリに同じ内容を2回書いてもまったく支障ありません。

○CASE4

すこしわかりにくいかもしれませんが、排他制御はこれで可能です。

FPGAなどのソフトでやれば簡単なのかもしれませんが、ハードだけでやろうとするとこういった形にならざるをえないのでは、

と思ってしまいます。もっと簡単な方法があるかな?

いずれにしても、メモリへのアクセスタイムの確保はギリギリになりそうな感じです。

これはいただき?2007.7.3

さて予約基板の発送も1陣終わってすこし余裕ができましたから、検討再開です。

electrartさんのHPでは鮮やかにFPGAをつかったFIFOが実現されていますが、これは真似できそうにありません。

そのなかで、タイミングチャートをみていて、これはいただき!と思いました。

ref:http://homepage2.nifty.com/electrart/DAI/dai.xls

ロジックタイミングをエクセルで書けば簡単そう!

です。いつもパワーポイントで書いていましたが、エクセルだともともと方眼紙みたいなものですから、書きやすそうです。

というわけで、早速書いてみました。

|

いや〜、これは楽です。

タイミングチャートから回路図を作ろう!

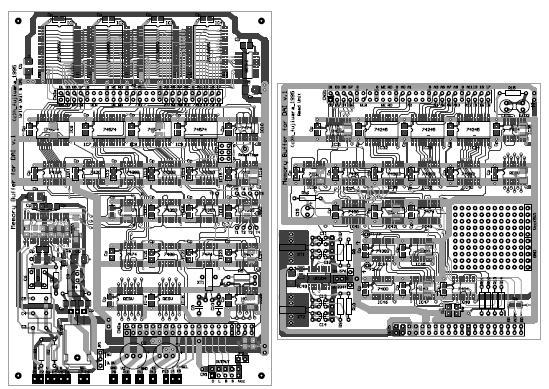

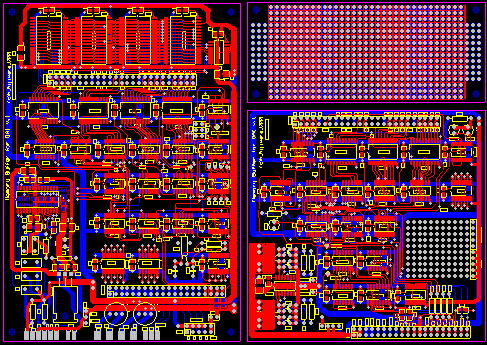

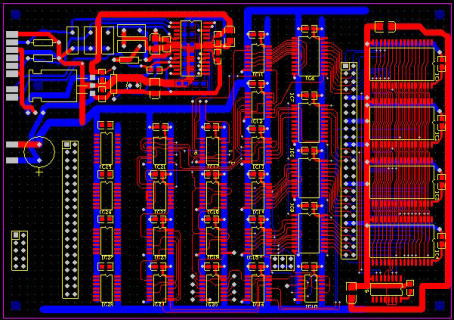

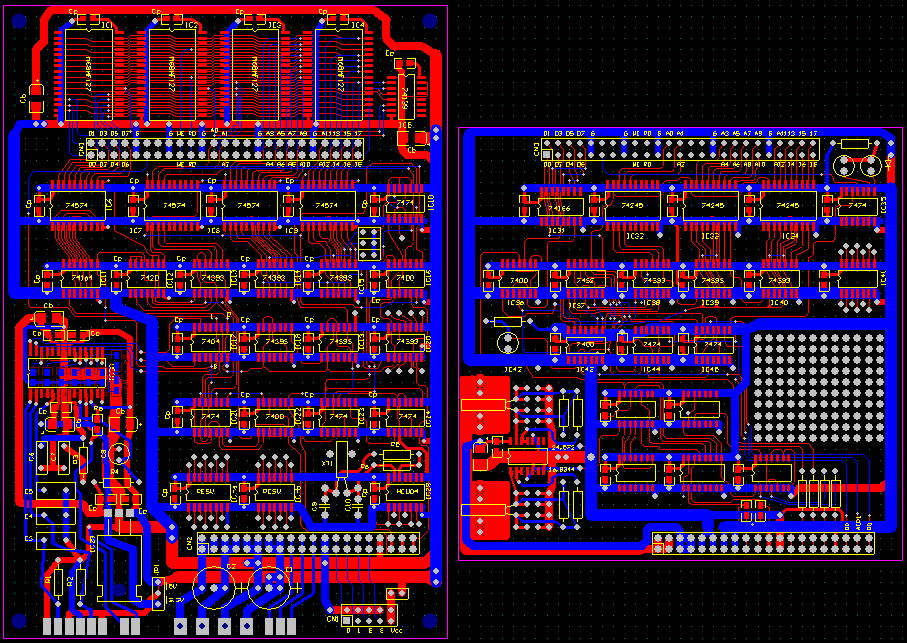

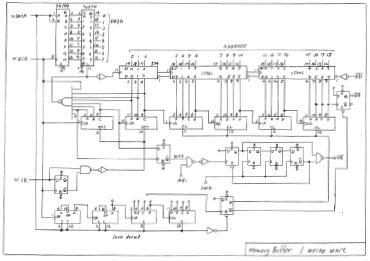

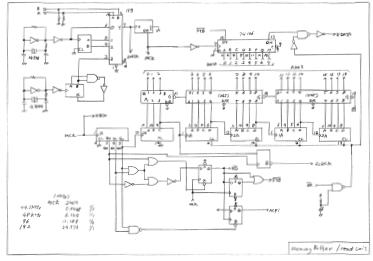

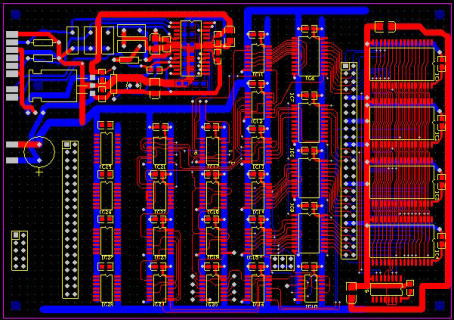

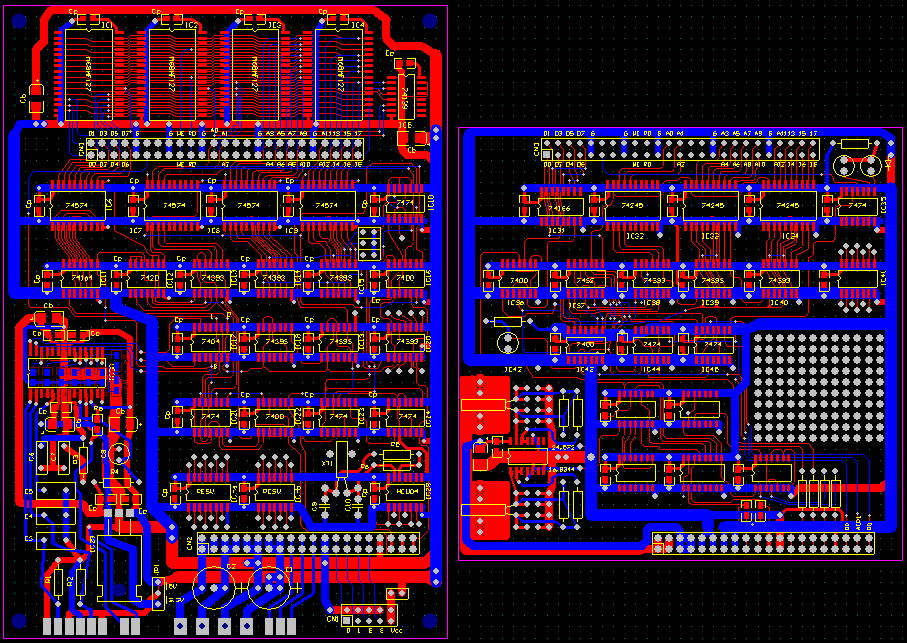

回路図は3枚くらいにおさまりました。特殊なものは使わず、ほとんど汎用品で構成しています。

ロジックICの多くはピン番号を入れていませんが、これはPCBのアートワークを描きながら配線し易いように

番号をつけていく予定です。

しかし、ICの数はメモリも含めて50個弱になりそうな感じで結構多いな〜。

ただ、ほとんどは16PinのSOPなので、実装面積はさほど大きくはならないとは思っていますがどうだろう????

さて、どのように進めるかな?

まず論理(設計)が合っているかどうかが一番重要なところですので、

最初にユニバーサル基板でDIP−ICをつかって確認したいところですが、

作業が大変そうです。いきなりPCBを設計しても、ミスがでるのはわかっていますが、

どうせ1、2回の試行は必須なのでまずは描いてみましょう。

あ、その前にせめて論理がタイミングチャートにあっているかどうかはチェックしておかなくっちゃ。

アートワーク作成?

回路図はちょっと間違いがありましたが、チョコチョコと直してアートワークにかかりましょう。

基板は2枚構成を予定しています。基板サイズはDAC1794woDAIと同じにする予定です。

構成はこんな感じです。

| ベース基板 |

書き込み回路+メモリ+(DAI) |

| ドータ基板 |

読み出し回路+発振器 |

ベース基板にDAI回路をのせるつもりはなかったのですが、スペースに余裕ができそうなので

CS8416をつかったDAIをのせようかと思っています。のせるとなると窮屈だし、ないとスカスカだし・・・・

どうしようかな?ちょっと、思案のしどころ。外付けDAIにすると、ケースに入れるのが面倒だし・・・

CS8416の入力を4ch→2chに変更すれば比較的余裕できるかな?

ちょっと作業をやめて考えましょう。

アートワーク途中で作業がとまっちゃいました。

水晶発振のジッタはどのくらい?

こんなコメントをいただきました。

| 7485 |

メモリーバッファー考 リード回路のクロック |

ma - 2007/07/08 01:17 - |

具体的な回路図までできてきましたね。

非同期バッファを用意した肝は、PLLによる周波数変動の除去、低ジッタ実現ですよね?

となると、水晶振動子を使って、自前の回路で発振させるだけでなく、

http://www.fujicom.jp/Xtal/FPO-700.pdf

このような、ジッタが保証された水晶発振器も使えるようにした方が良いのではないでしょうか?

パターン的には、

http://www.fujicom.jp/Xtal/FCO-100,200.pdf

この辺りのものも使えるようになっていると良いのではないかと。

また、次のようなものを使いたい人もいるでしょうから、接続可能になっているといいかと。

http://www.soundden.com/dentec/clock/lc-lock.html

|

|

もともと、メモリーバッファーを検討しはじめた理由はDAIのPLLジッタ低減(DIR9001で50ps)を目的としていたのですが、

一般的な水晶発振におけるジッタはどんなもんでしょうね。

紹介いただいたURL: http://www.fujicom.jp/Xtal/FPO-700.pdf

を覗いてみましょう。

一番下の欄にジッタの記述があります。1psのようですね。PLLよりは随分よくなります(あたりまえ?)

でもよくわからない記述があります。「Fj=12kHz to 20MHz 」とありますが、これってなんだろう?

そもそもこの発振器が70MHz〜200MHzの範囲なのに、12kHz to 20MHzとあるのは多分発振周波数とは

違うものを指し示しているようです。

ちょっとネットサーフィンをして、他の水晶発振器のジッタの記述を調べて見ましょう。

村田製作所さんのHPをみていたら、ちょっと興味ある記事がありました。

ちょっと抜粋してみました。

<引用URL:http://www.murata.co.jp/articles/ta0441.html>

(5)ジッタは同程度

高速通信用、高速演算用ICの場合、クロック信号のジッタ(ゆらぎ)が問題となる場合があります。(図8)一般にセラミック発振子は水晶発振子より周波数精度が悪いため、ジッタもセラミック発振子のほうが悪いと思われがちですが、実際にはジッタ測定結果に差は見られません。

図9は汎用ゲートIC 74HCU04APを使ってショートターム・ジッタ(ピリオド・ジッタとも言う)を測定した結果です。8MHzのセラミック発振子と水晶発振子のいずれも標準偏差σは約10ppmとほぼ同じ結果になりました。また、図10に示すようにロングターム・ジッタ(n周期間隔のジッタ)においても差が見られませんでした。

図8 クロックの大敵ジッタとは信号エッジのゆらぎ成分のこと

|

図9 ショートターム・ジッタの比較結果

セラミック発振子のほうが悪いと思われがちだが、実際には有意差はみられない

|

|

ここではセラミックと水晶発振子のジッタは基本的にはかわらないということを結論づけたかった記述ですが、

目を引いたのはこれが汎用ゲートIC 74HCU04APを使った結果ということです。ということは、

簡単な発振回路でも1ps程度のジッタの実現はできるということになります。

話をもとに戻して、他のメーカのジッタの記述を探してみましょう。

位相ノイズという言葉のようだ。

ジッタという時間軸よりは周波数軸での位相ノイズの方が一般的のようです。

ちょっと概念的にわかりにくいところがありますが、参考になるHPが色々とあるので、勉強してみようかな。

タイミングジッタの要因となるランダムノイズ―理論と実践 - マキシム-ダラス

位相ノイズ測定(LECROYの資料)

PLL_発振器の設計法

位相雑音について

だいぶできたかな?

まだWRITE UNITだけど、細かいところの配線は大体おわりそう。

もうすこし密度を上げてもよかったくらいだけど、部品配置に余裕があった方が組み立ては楽だ。

結局CS8416をつかったDAIをのせることにしましたが、入力は2chのみにしました。

#この3連休はどうも雨模様だけど、恵みの雨になるか、それとも災禍の雨になるか・・・・

一通りの配線完了!

といっても、チェックはこれからなので、まだまだ完成度70%くらい。

しかし、配線チェック面倒そう。配線チェックがOKでも論理に間違いがあれば動かないだろうし・・・

本当に動くのかな?

当初の回路は変更して、水晶発振回路は別電源で動作するようにしてみた。

ここに安定した電源を投入すれば好結果が得られるかもしません。

あと、ドータボードにはユニバーサルスペースを配置。市販の発振器も搭載可です。

ようやく70%は完成したかな?

結局のところ、ロジックICはメモリも含めて全部で43個。

思ったよりは少な目です。

バグ取りのときに、さらに必要なICが増えてしまうかもしれませんが・・・・・

アートワークに合わせて回路図も若干修正し、こんな感じで完了?

チェック用の端子とかの追加、最終パターンチェックがのこっていますが、ほぼ最終形です。

パターンと回路を見比べてながらチェックすると、出るわ出るわ!間違いだらけ。

つなぎ忘れているところが山の様にでてきました。おまけにつないじゃいけないところとつないだりしているのがあったりして、

結構チェックに時間かかりました。それに、今回は基板設計のデザインルール(パターン幅とパターン間隔をを0.2mm(メーカ仕様は

0.15mm)にしていますが、それを割り込んだところがあったりして、パターン修正も時間がかかったところです。

やっぱFPGAのプログラミング勉強しようっかな・・・・

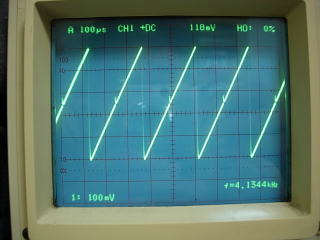

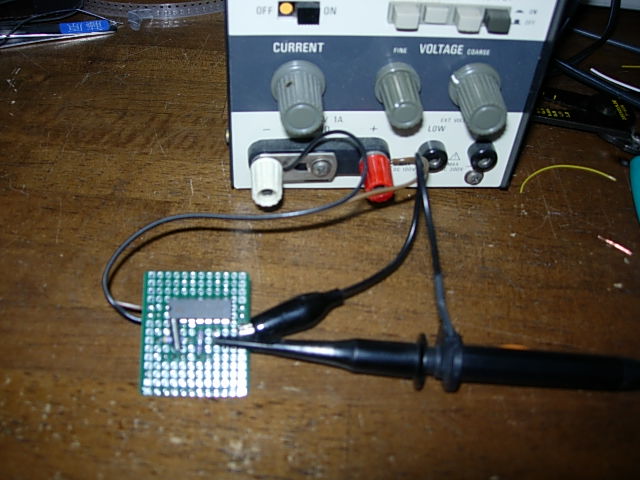

ちょっと実験!

ディスクワーク(?)ばっかりしていると疲れてくるので、ちょっと半田ゴテで遊んで見ましょう。

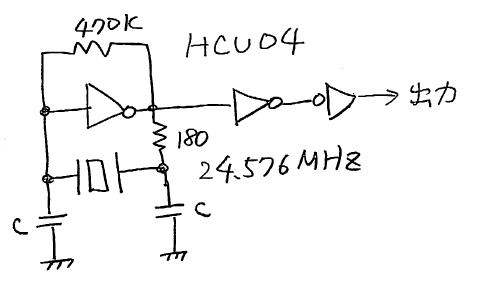

今回の回路では水晶発振子を74HCU04をつかって発振させますが、24MHz以上のものが、発振できるのか一度も確認したことがありません。

ということで一度試しておきましょう。そして、ついでに負荷容量によって発振周波数がどの程度変わるのか確認しておきましょう。

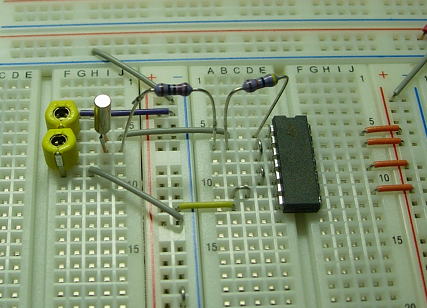

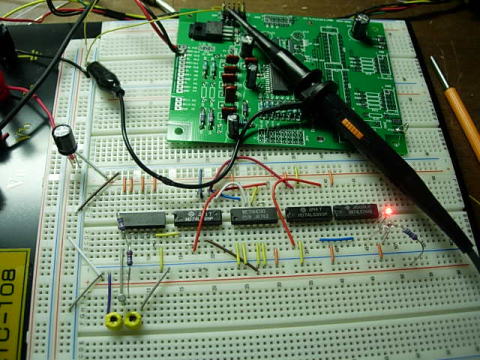

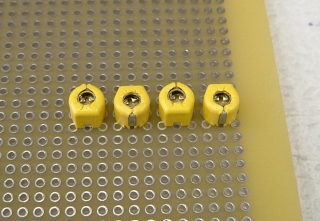

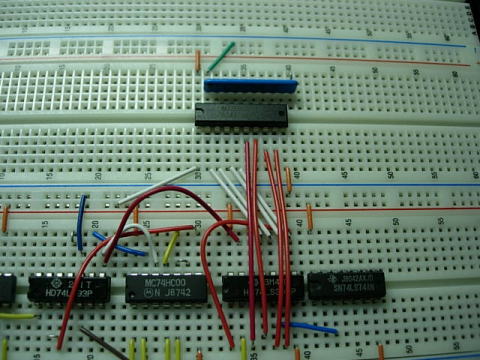

回路と試作物はこんな感じです。まだこのときはコンデンサをつけていません。

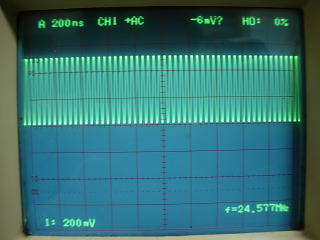

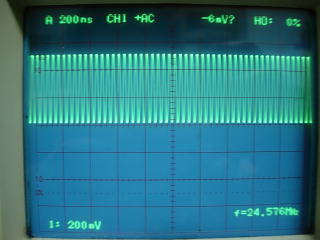

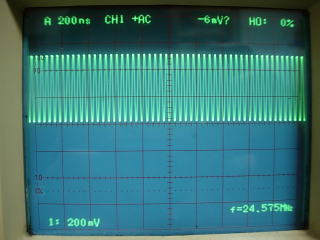

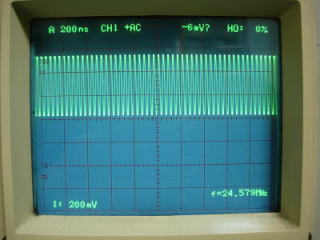

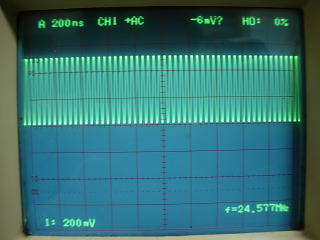

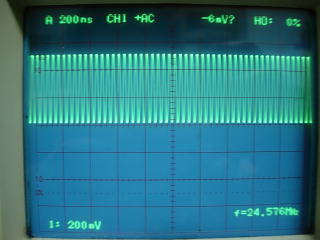

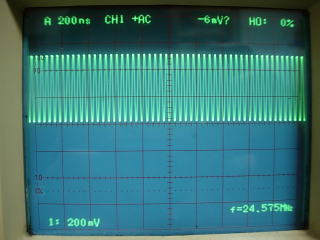

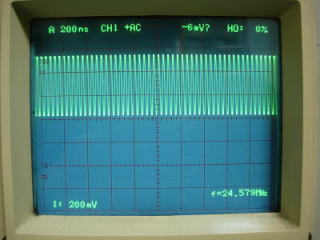

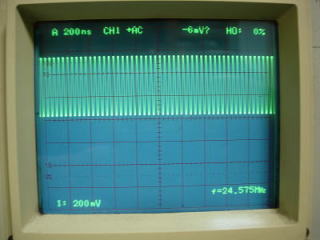

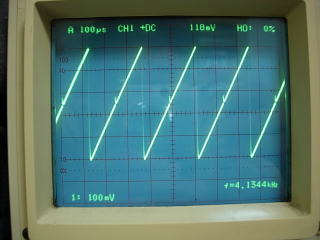

コンデンサの容量を変えて周波数を測定してみました。オシロの周波数カウンタの精度がわからないので、

相対値のみの比較になります。

実験の様子

測定結果

コンデンサは手持ちのセラミックコンデンサをつかっています。そのため容量精度はあまりよくないと思います。

|

|

| コンデンサなし 24.587MHz |

C=22pF 24.577MHz |

|

|

|

|

| C=44pF(22pF×2) 24.576MHz |

C=144pF(22pF×2+100pF)

24.575MHz |

オシロの帯域が低い(20MHz)ので、矩形波としては観測できませんが、周波数カウンタとしては大丈夫でしょう。

まずコンデサが無いと発振しないかと思いましたが、発振するんですね。

しかし値が24.587MHz(水晶の公称値24.576MHz)と比べると大きくことなっています。うまく共振点で発振できないようです。

コンデンサを22pFいれると安定した動作になるようで、周波数も24.577MHzになりました。

そのあと、コンデンサを追加していくとわずかながら周波数が低下します。

144pFとすると、24.575MHzとなりました。22pFに比べると、81ppmの低下です。

44.1kHz換算すると約3.5Hzになります。うまくコンデンサを選べば手持ちのCDPと周波数を合わせることは出来そうな

感じがしてきました。

コンデンサの容量が変えられやすいように、パターンは少し余裕を持たせています。

負荷コンデンサの取り付けパターン

基板発注!

パターンを書いたのは勿論CADの上だけど、画面の上ではその具体的な大きさをあまり

イメージする事無しにパターンを書いてしまいます。そして実物サイズにパターンを

印刷してその小ささにちょっと引いてしまいました。

考えてみれば当たり前で、この基板サイズ(一応2枚ありますが)

ICが50個弱乗っかる訳ですから、配線密度もそれなりに高くなります。

さらにSOP(1.27mmピッチ)のピン間を配線を通すようにしているので、配線も細くまた

配線間隔も狭くなっています。

今回のデザインルールは0.2mmとしました。この値はプリント基板製造メーカの仕様である

0.15mmに比べれば余裕があるのですが、修正を前提とした線の太さはありません。

パターンを剥いで半田付けするには少なくとも0.5mmくらいは欲しいところです。

それにICの下の配線を修正しようとすればもうお手上げです。

という訳で、折角配線をしたものの、本当に試作して完動までもっていけるか急激に自身が

なくなってきました。せめて、DIPで組んで正しい回路を確認できれば、あとはなんとか

なるのですが、SOPの基板での修正作業はやっぱり大変そう。

そうこう思っているうちに発注する気力が下がってきましたが、

こういうときはアルコールが一番(笑)。

少し飲むと、ちょっとやって見ようという気がおこってきました(爆)。

さらに、もう一杯やったところでWEBから発注をかけていました(爆爆)。

これが発注した基板の面つけ。空いたスペースにはユニバーサル基板を押し込みました。

発注した基板の面付けの様子。

さて、基板を発注すれば後にはひきませんね。ついでに必要なIC類も注文しちゃいましょう。

なんと、10種類以上のICが必要です。それぞれの個数は大体3枚以上の試作にひつような

数を目処に頼んでおきました。おそらく、最低でも2枚はつくってぐちゃぐちゃにすることにはなるでしょう。

もっと買っておけばよかったかな〜。

あ、ICのついでも周辺部品も秋月電子に頼んでおきましょう。

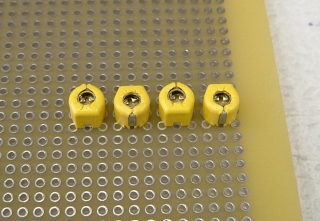

秋月のワンコインコーナをみているとトリマーコンデンサが目につきました。

容量は45pFとちょうど、水晶発振の調整によさそうです。100円で4個なので、これも2袋ほどGET。

ref:http://akizukidenshi.com/catalog/items2.php?c=100yen&s=popularity&p=1&r=1&page=160&cl=1#P-01325

しかし、酔っぱらった状態だと注文する部品の予備数が多いこと。

ついつい、多めにかってしまいます。こんなことしているから、部品箱が一杯になるんだろうな・・・・・

部品箱で思い出しましたが、重宝しているのがこれ。

100均で売っているプラ箱。

100円均一のダイソーで買えるパーツボックスです、といいましたが以前は100円で買えましたが

今は200円です。値段は倍になりましたが、いわゆるHOZANなどのパーツボックス(1000円以上?)

に比べると安いです。ただし蓋の閉まりが悪いので、ひっくり返さないように注意が必要です。

さて、基板ができあがるまではしばし休憩です。

秋月から荷物到着?2007.7.18

出張から帰ったら届いていました。あれ?箱が大きい。何頼んだんだろう?

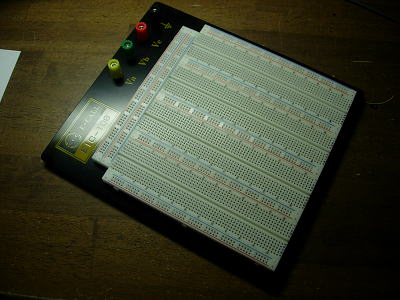

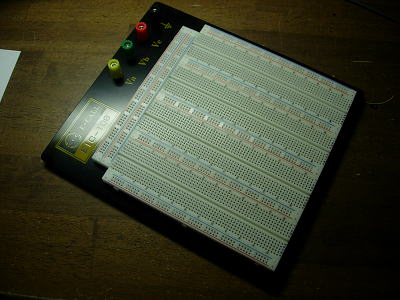

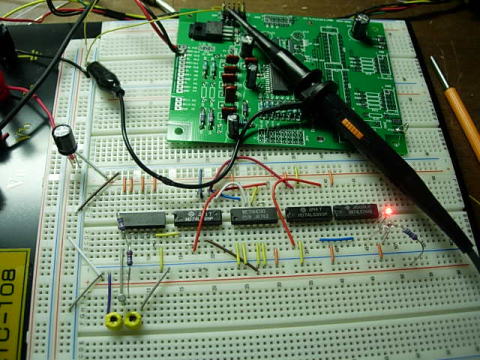

本人も忘れていましたがブレッドボードを頼んでいました。

いつも店頭で気になっていたのですが、ケースが大きいので持って帰るのには躊躇していたのですが、

通販なら気になりません。

一度はつかってみたかったブレッドボード

折角なので、ちょっとつくってみましょう。

ちょっと前に実験した水晶発振の実験をしてみました。

ついてにトリマーコンデンサ(45pF)をつないで、どこまで周波数が変わるかも併せて測定してみましょう。

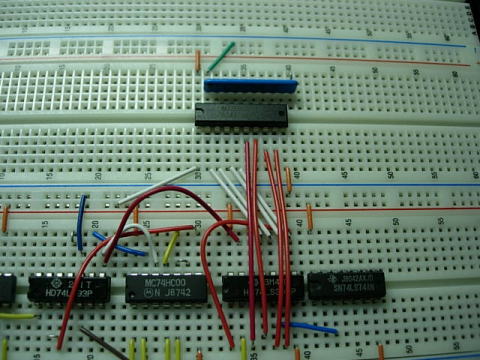

早速簡単な回路を組み立て。

じつはトリマーコンデンサって初めてつかいましたが、VRのように最大、最小値のところで止まらないですね。

くるくる回って、どこか最大で最小かわかりません。ん・・・・こんなもんかな?

とりあえず、実験の結果は24.575〜24.579MHzまで可変できそうなことがわかりました。

しかし、ブレッドボードって便利だな〜。部品の再利用もし易いのもメリットです。

最大周波数は24.579MHz 最小周波数は24.575MHz

半田付けしなくて済むので、机の上もあまりちらかりませんし、

何よりも簡単な回路なら素早く組めます。

もっと早く買っておけばよかった。

あ、メモリバッファーもこのボードをつかって動作確認をする手があった(汗)。

ただ、ICの数が多いので、これではサイズが足りないし、それに組むのもやはり大変かな・・・(半分負け惜しみ)。

でも、ブレッドボード楽しいな〜遊んでしまいそう。

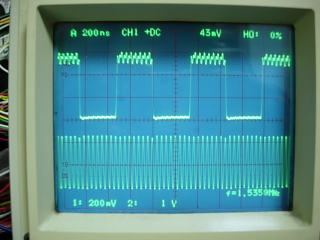

クロック出力に7493(分周器)を挿入 波形はリンギング多い。電源ラインが弱いかな?

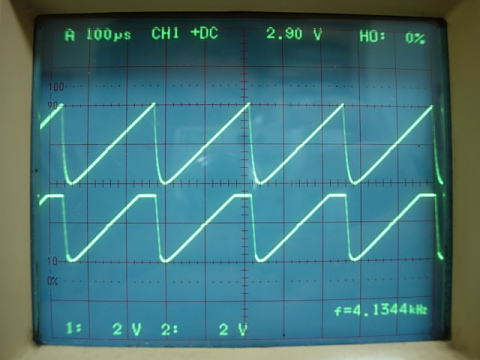

思わずあそんじゃいそう・・ 2007.7.19

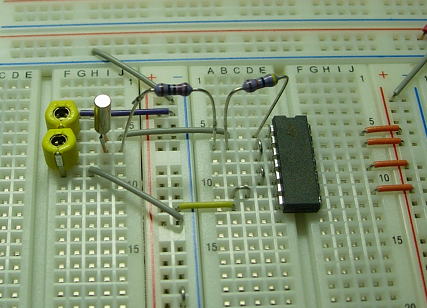

ブレッドボードで遊ぶついでに、もう少し実用的(?)な実験をしてみました。

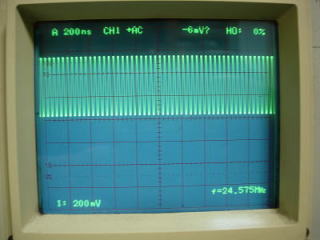

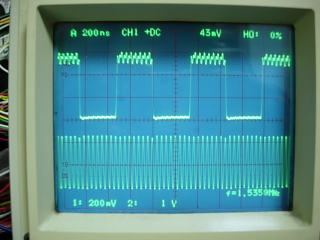

といっても、水晶発振を16.9344MHzに変更して44.1kHzを作成して。手持ちのCDPとの周波数の差を確認するためです。

元の発振周波数を16.9344MHzに変更して、1/384に分周するカウンタを組みます。

これは7493と7400をつかって1/3に分周したあと、74393にてさらに1/128に分周します。

これで、44.1kHzのできあがりです。

CDPのWORD CLOCKを確認するためにはDAIが必要ですがCS8416をつかったDAIがあったので、

これを使いました。

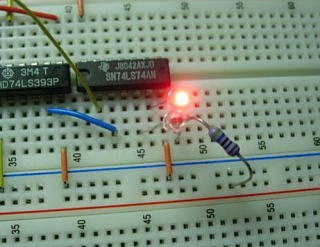

テストの様子。ブレッドボードがあれば半田付け不要で実験できるので便利!

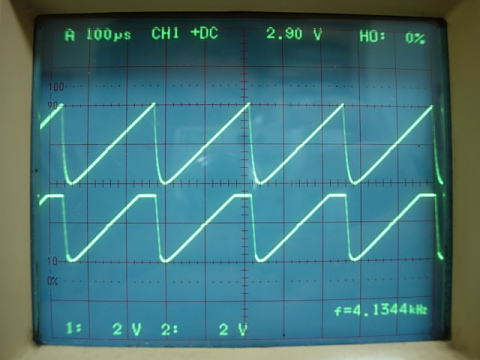

さて、どのくらい周波数がずれているか見てみましょう。下のオシロは上側がCDP側で、下側がブレッドボードで

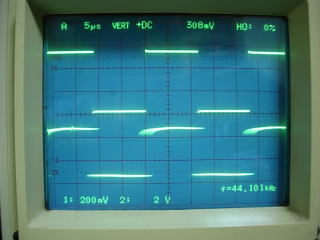

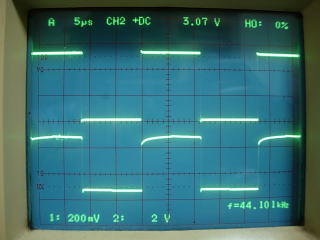

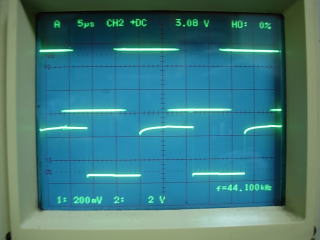

作り出した44.1kHzです。互いの周波数はそれぞれ44.101kHzと44.100kHzですので、ほぼ1Hzの誤差がありした。

オシロに表示すると、互いに流れて表示されますから写真を撮った時に画像がぶれてしまいます(流れて見える)

CDPを基準にした場合。 ブレッドボード発振を基準にした場合。

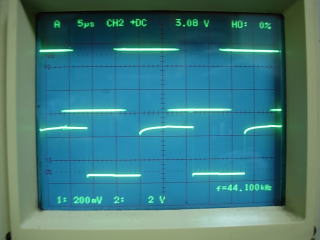

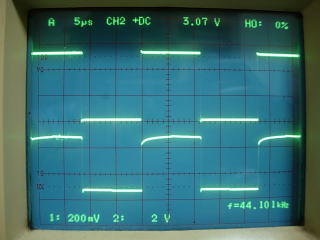

そして、お互いの周波数を合わすためにトリマーコンデンサを調整すると、ほぼドンぴしゃで周波数を合わせることができました。

周波数がほぼ一致すれば、メモリーバッファーの容量がすくなくても、オーバーフローやアンダーフローは生じません。

しかし周波数を合わせるためにオシロがないとなると、不便です。

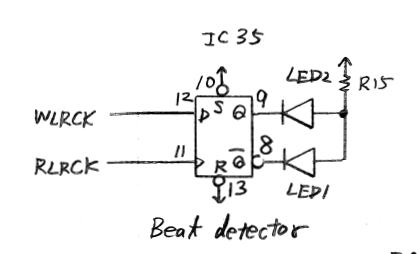

ということで、ビートチェッカーなるものを入れています。これは互いの周波数のずれを

2個のLEDの点灯間隔しわかるようにしたものです。この点灯周期が例えば1Hzあったなら、

周波数の差が1Hzということになります。

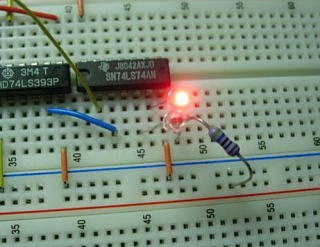

組み込んだビートチェッカー

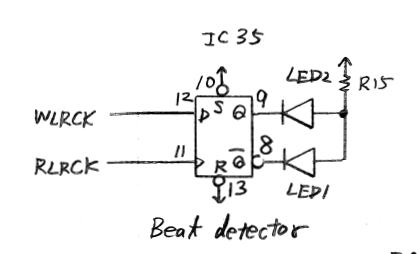

ビートチェッカーといっても大した回路ではなく、こんな感じでD-FFを1個つかっただけです。

ビートチェッカーの回路 |

この回路はもちろん今回試作しているメモリーバッファーの回路に組み込んでいます。

LEDの点灯周期が1Hz以下になるようにトリマーを調整すれば、問題なしです。

じっくり調整すれば点灯周期0.1Hzくらいにはすぐに設定できます。

調整後に波形を再度撮影すると、お互いに止まって見えます。

ここまで調整できるのなら、メモリーバッファーも安心してつかえそうです。

CDPと発振周波数を合わせるとぴたりと止まって見えます。

ちょっと話しは変わって 2007.7.22

先日、秋葉で集合抵抗(プルアップ用)を探していたら日米商事の店先で袋売りをしていた。

ほとんどが数10Ωと低い値だったが、根気よく探したところ50kΩのものがでてきました。

足の数を見ると10本あるので9素子だろうと判断。

欲しかったのは8素子ですが、不要な部分は切り取ればOKということでゲットしました。

100個はいって210円ですから、たとえ使えなくても安いものです。

でも、まったく使えなかったら単なるゴミになってしまいますが・・・・

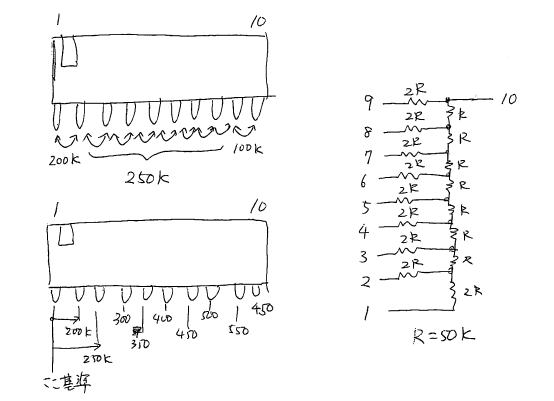

とりあえず手に入れた集合抵抗 10本足があるから9素子かな?

内部解析?

メーカはKOAで型番は「MRGC」とあるのですぐにネットで検索できるかと思いましたが、

どうも見あたりません。古い型番で製造中止品なんでしょう。

ということで、抵抗値を直接はかってみましょう。

あ、R−2R用だ!

ピン間の抵抗と、1番ピンを基準として抵抗は計ってみましたが、かなり変則的です。

「50kΩ」と書いてあるのに、どこを計っても50kΩの値がでてきません。

それに、両端で値が変則的です。

どうも、R−2Rラダーにつかう抵抗ネットワークのようです。そう仮定すれば、両側の抵抗値の変則性は理由がつきます。

実際に試してみましょう!

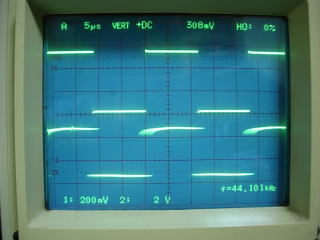

74AC245をバッファとしてR-2Rを駆動してみます。74245の入力は74393からの8Bitカウンタの入力を入れますから、

ちょうど三角波が得られるはずです。

テスト中の様子。最近ブレッドボードをよくつかいます(お気に入り)

予想通り、三角波がでました。やはりR−2Rネットワーク抵抗のようです。

ちょっと出力レベルの真ん中でノイズみたいなものが見えますが、オシロプローブを直接つないでいるのが問題かな?

とにかく、出力抵抗が高いので色々な影響を受けやすいのでしょう。

予想通り三角波が出ました。

ノイズをとるために、出力にLM358(オペアンプ)を入れてみました。電圧は5Vで駆動しているので、

最大電圧は3.5Vくらいになっていますが、出力レベルの真ん中でのノイズは小さくなりました。

あれ?元信号のノイズも小さくなってるぞ?単にオシロのプローブのGND位置が悪かっただけかな?

上:R-2R出力 下:オペアンプ通過後出力

いずれにしても、この抵抗器はプルアップ用には使えそうにありません。

R-2R用として、マイコン等につないで簡単なアナログ出力を作るには便利そうですが、

あまり用途もないよな〜・・・・

ということで結局捨てられないゴミになりそうな予感!!!

(つづきは後編へ)

書き込みユニット

書き込みユニット