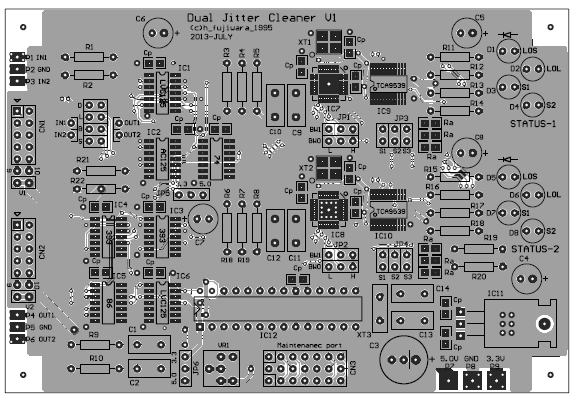

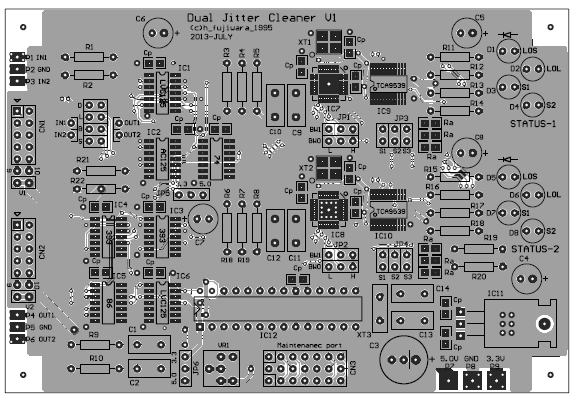

DUALジッタクリーナは実現するか? 2013.7.20

DACにジッタクリーナは必要だな〜と思って時間が経ちますが、どの信号ジッタクリーナにかけるか悩みます。

PCM信号ならばらBCK信号が必須かなとはおもいますが、システムクロック(SCK)もやはり必要でしょう。

2信号をジッタクリーナにかけるには現状のジッタクリーナ基板を2枚使えばいいのですが、

どうしても配線が複雑になってしまいます。ということももあり、2信号が1枚でジッタクリーナできるように

2回路分を実装したDUALジッタクリーナを考えてみることにしました。

しかし、1ch分ならまだ部品のレイアウトに余裕がありますが、2chでは結構実装密度が高くなってしまいそうです。

でも、一度アートワークを描いてみましょう!

とりあえずアートワークを描いてみました。

でも・・・・

結構ソフトが大変そうな予感です。実現するかな?

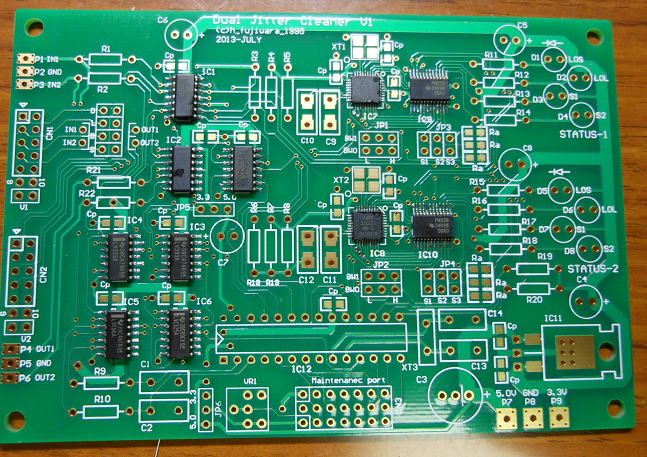

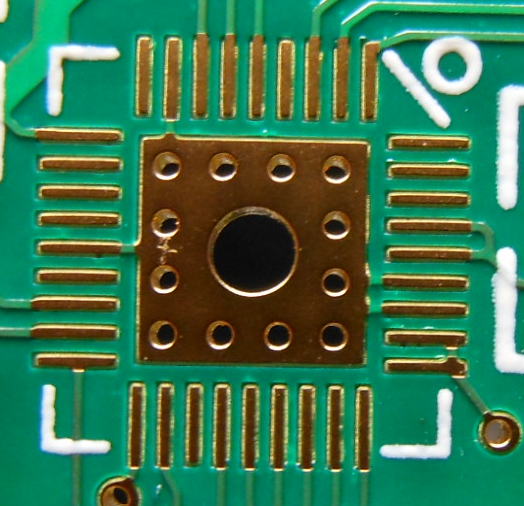

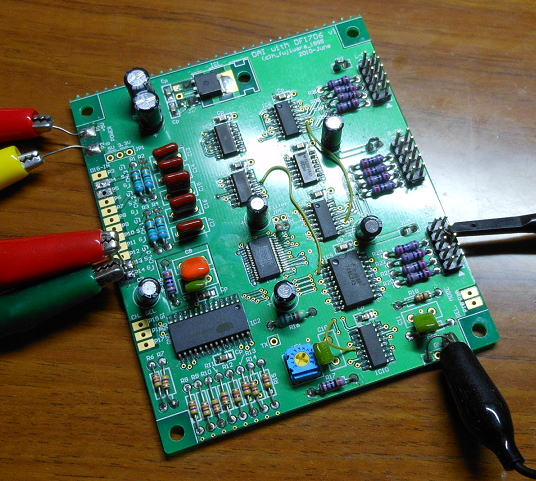

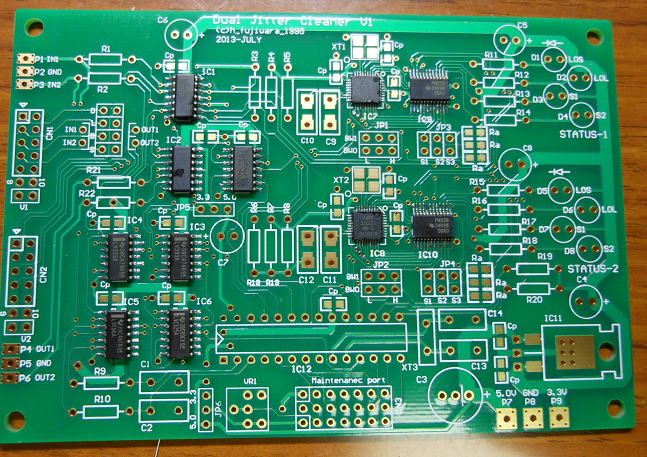

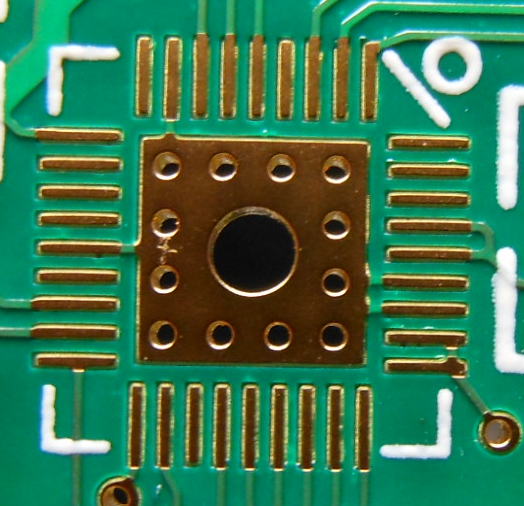

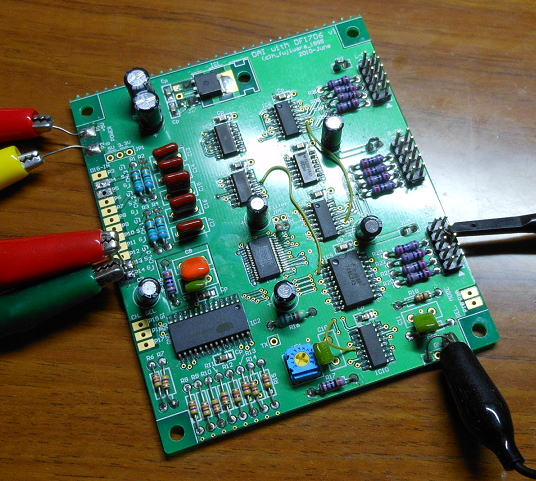

基板到着! 2013.8.6

そうこうしているうちに基板が到着しました。

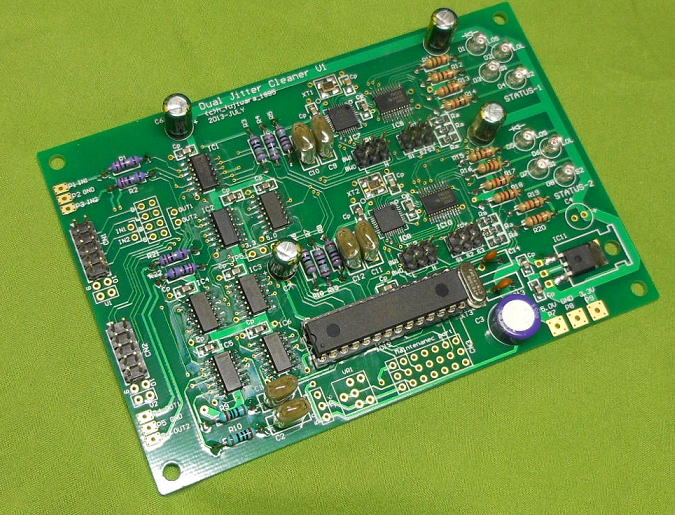

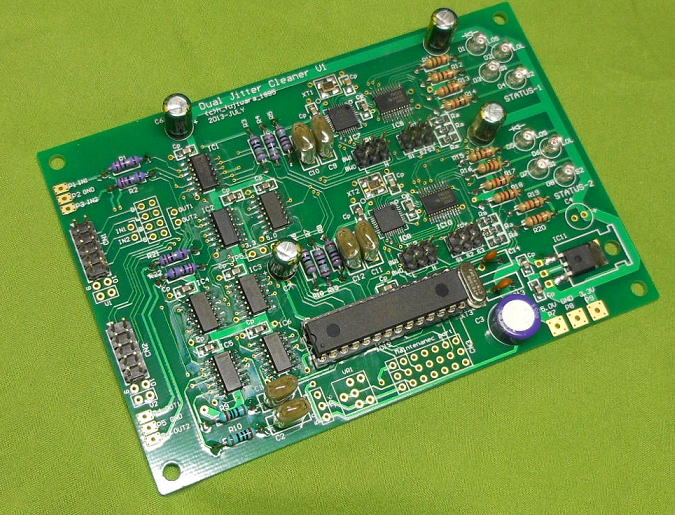

基板が出来上がりました!

一気に作ってしまいましょう。表面実装部品が多いので、意外と製作時間はかかりません。

面倒といえば、部品を探す手間です(笑)。

まずは表面実装部品を中心に取り付けました。

すべての部品が取り付いた段階でお出かけ用の写真を撮りました。

動作確認していきましょう! 2013.8.16

動作確認にはソフトが必要ですが、まずは備忘録かわりにIOポートを定義しておきましょう。

IOエクスパンダー(PCA9539)

| IO0-0 |

FREQSEL3 |

|

IO1-0 |

LED S2 |

| IO0-1 |

FREQSEL2 |

|

IO1-1 |

LED S1 |

| IO0-2 |

FREQSEL1 |

|

IO1-2 |

LED LOL |

| IO0-3 |

FREQSEL0 |

|

IO1-3 |

LED LOS |

| IO0-4 |

Si5317 LOL |

|

IO1-4 |

N.C |

| IO0-5 |

JUMPER S1 |

|

IO1-5 |

Si5317 RST |

| IO0-6 |

JUMPER S2 |

|

IO1-6 |

FREQTBL |

| IO0-7 |

JUMPER S3 |

|

IO1-7 |

Si5317 LOS |

PIC16F887

| A0 |

Phase ERR 2(AN1) |

|

B0 |

SI5317 Ch.2-DEC |

|

C0 |

CLOCK-IN |

| A1 |

Phase ERR 1(AN0) |

|

B1 |

SI5317 Ch.1-INC |

|

C1 |

LCD-D5 |

| A2 |

N.C |

|

B2 |

SI5317 Ch.1-DEC |

|

C2 |

LCD-D6 |

| A3 |

LCD-RS |

|

B3 |

PHASE CHK 2 |

|

C3 |

LCD-D7 |

| A4 |

LCD-E |

|

B4 |

PHASE CHK 1 |

|

C4 |

SDA |

| A5 |

LCD-D4 |

|

B5 |

IOE-RST |

|

C5 |

SDL |

| A6 |

OSC1 |

|

B6 |

N.C |

|

C6 |

IOE-RST(NOT USE) |

| A7 |

OSC2 |

|

B7 |

CLOCK-SEL

H:CH1 L:CH2 |

|

C7 |

SI5317 Ch.2-INC |

まずは

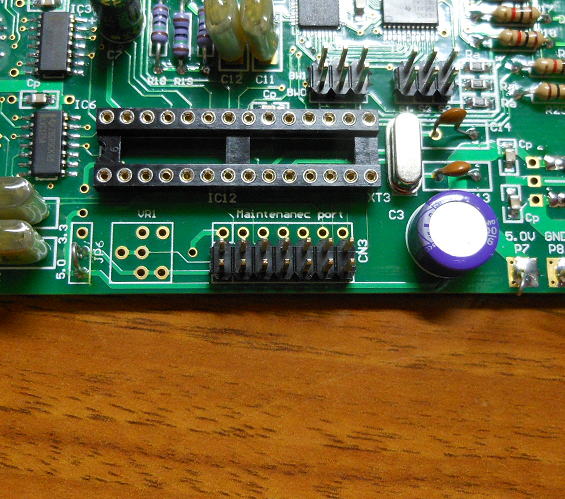

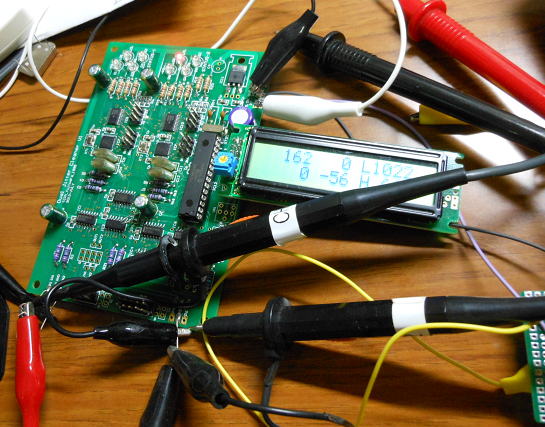

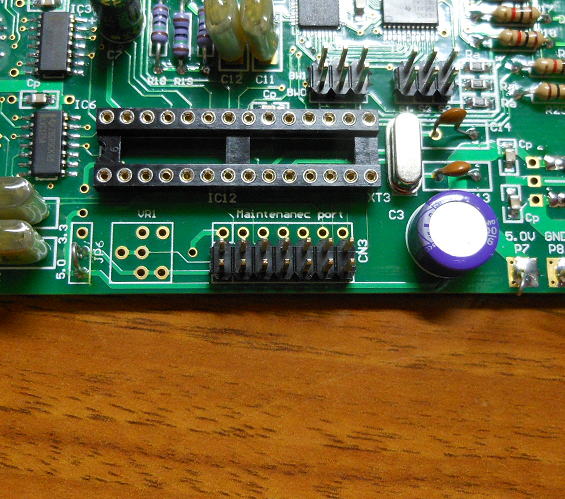

ソフト作成のためには、状況を表示しないと手探りでのデバッグになるので、メンテナンス用に取り付けておいた

LCDポートにピンをたてました。そして、PICにLCD表示用のプログラムを書いて動作確認。

これで、すくなくともPICが動いているかどうかはわかります。

メンテ用のLCDポートにピンをたてました。

あわせてLCDの動作のみ確認です。ここまでは難なく到達!

電源ON!動かない・・・・

まずは簡単なプログラムを書いて電源ONです。動かない・・・・・。

まあ、いきなり動くとは思えないので想定内といえば、想定内ですが少し焦りがでてきます(^^;)

.

デバッグもまた楽し!

まずは電源から確認です。5Vを入力して内部で3.3Vを生成していますが、

電源電圧ラインの電圧を測ってみると、なんと本来3.3Vのところの電圧表示が5Vに

なっています。あちゃ〜!!!!!

動かない(その1)

原因を調べてみると、なんと出力バッファーの74AC125の電源の引き回しにミスがありました。

この基板自体は主に3.3Vで動作しますが、出力信号の振幅を変更できるように、出力バッファーの

74AC125については、電源電圧を3.3Vと5Vから選択できるようになっています。

そこで74AC125には5Vを供給するようにジャンパー設定していましたが、VDDにすでに3.3Vを接続

するパターンが存在していたのでした。そりゃ、3.3Vラインに5Vがのることになるな〜。。

原因はわかったので、切り替えジャンパーを3.3Vに設定しなおして、出力も3.3Vになるようにしました。

しかし、3.3VのロジックIC等に5Vが作用したんだよな〜。

ジッタクリーナIC壊れてないかな〜・・・・・(焦)。

単純な間違いだけど、下手をすると致命的な間違い・・・・・・

動かない(その2)

電圧オーバーでジッタクリーナが壊れている可能性を気にしつつ、とりあえず作業を進めます。

たぶん大丈夫でしょう(と、自分の折れそうな心に言い聞かせながら・・・)。

さて、ジッタクリーナの制御ICにはIOエクステンダーのPCA9539をつかっていますが、これらは

I2C制御をしています。しかし、PICとこれらのICとの通信がうまくいかず「I2C ERROR」の表示が・・・。

半田付けは大丈夫だし、パターンも大丈夫そうなんだけど・・・・。

ひょっとしてPCA9539が過電圧でいってしまったのかな?

とマニュアルをみてみると、PCA9539は5Vでも動作するようです。これは助かりました。

さてオシロで信号を確認すると、SCL(クロック)が出ていません。 これは、ソフトのミスでした。

PICのSCL出力を出力として定義していなかっただけのポカミスでした。

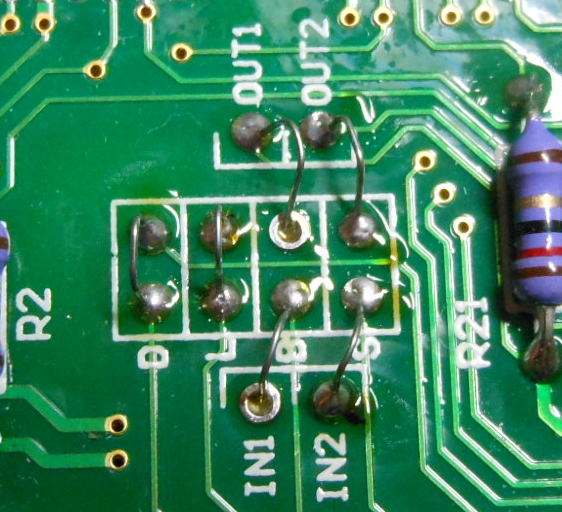

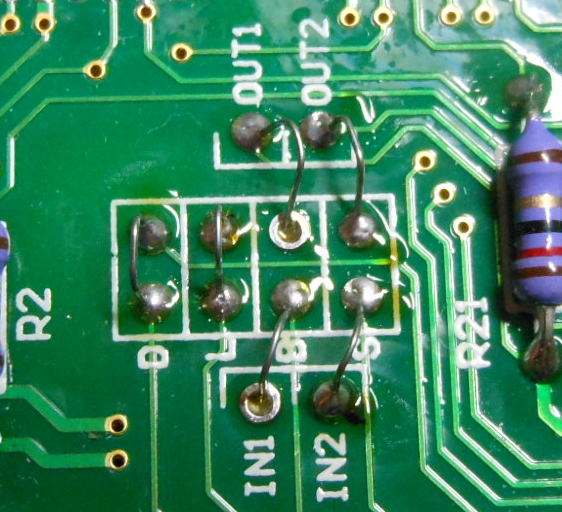

動かない(その3)

PCA9539との通信は回復(?)して、ジッタクリーナの1つは動きだしましたが、もう1つのジッタクリーナからは

音信不通です。いや、LOS(信号喪失)、LOL(ロックはずれ)の信号は正常にでているのですが、

なぜか出力だけがでてきません。よくパターンをみると、出力制御端子のパターンにミスがありました。

2つのジッタクリーナは同じように描いたはずなんだけど、なぜ間違えてたんだろう?

正しい接続(IC7)出力がCMOS設定。 配線が抜けています(IC8) これでは出力がでません。

修正はこんな感じで、隣のピンと半田ブリッジをさせました。どこかに線を引き回さないとなると、

すこし面倒になりそうでしたが、このくらに修正で済んでたすかりました。しかし、修正には結構テクも必要

なので、リリースするときは修正版にしなくっちゃ。

となりとの接続で済んで助かりました。

ようやく動きだしました!!

ひととおりのハードウエアの機能を確認するプログラムを組んでチェック完了です。

あとは、じっくりソフトをくみ上げていきましょう!

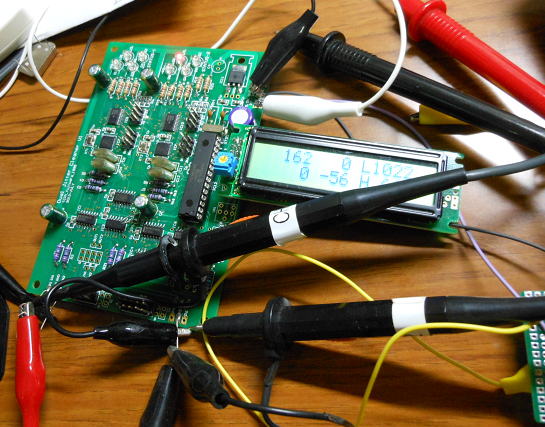

テストの様子です。LCD表示には状態を表す意味不明な数値が・・・・

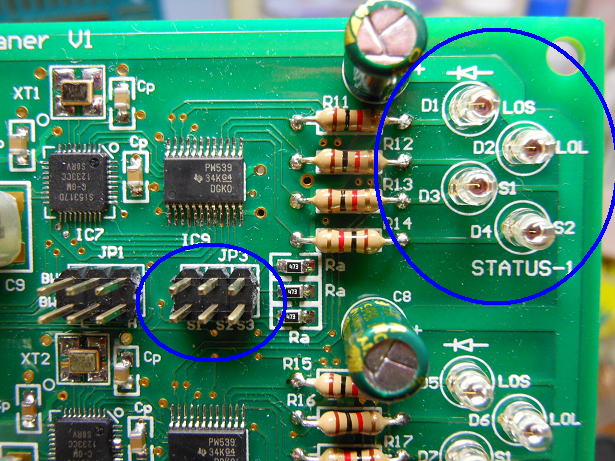

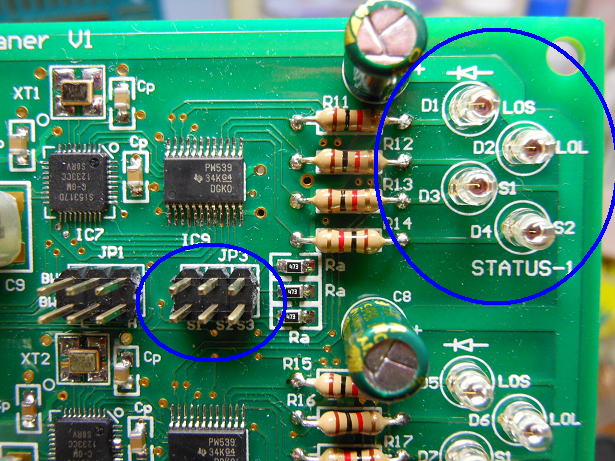

ジャンパー機能とLED表示の定義

今回のジッタクリーナ基板では状態を表示するためのLEDと動作モードを設定するためのジャンパーを

つけました。ちなみに、バンド幅は下図ではJP1で設定します。

ここで、それぞれの機能について定義しておきましょう。

ジャンパー(動作モード)

|

開放 |

接続 |

説明 |

| S1 |

強制位相調整機能 無効 |

強制位相調整機能 有効 |

周波数が変化した場合に、強制的に入力と出力の位相を一致させるための機能です。

たとえばBCKを入力とした場合で、入力周波数(FS)が44.1→48kHz等に変化した場合

にてでも、すばやく位相を一致させるための機能です。システムクロックなどには不要

ですが、BCKでは必須になるでしょう。 |

| S2 |

経時位相調整 無効 |

経時位相調整機能 有効 |

入力と出力信号が、時間が経つにつれて微妙に位相がずれてくる可能があるので、

それを長周期で修正するための機能です。とくにBCK信号などには必要になると

思われます。 |

| S3 |

経時位相調整時間 継続的 |

経時位相調整時間 約1分 |

上記の経時位相調整機能を動作させるための時間を設定します。一定時間たつと、

機器も安定すると思われるので、一定時間後にこの機能のON/OFFを設定します。 |

LED

|

点灯時の説明 |

| LOS |

ジッタクリーナに入力信号が欠落した場合に点灯(入力信号なし) |

| LOS |

ジッタクリーナのロックが外れている場合に店頭(ロックはずれ) |

| S1 |

位相ずれが10%以上の場合に点灯 |

| S2 |

位相調整機能が動作している場合に点灯 |

モード設定用のジャンパーと状況表示用のLED。

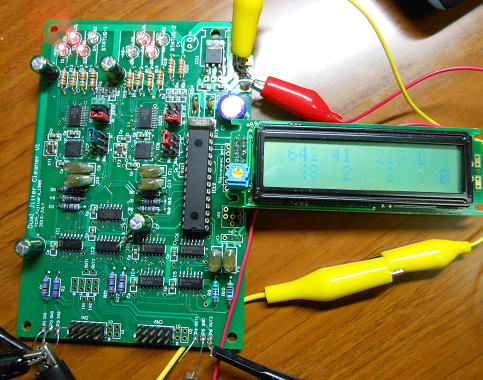

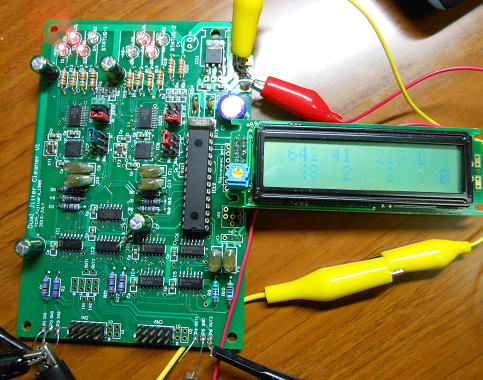

ソフトもほぼ完成! 2013.8.25

2ch分のソフト構成もほぼ完成しました。前作のジッタクリーナでは1チャンネル分だけなったので、

ソフトの流れはあまり考えなくてもよかったのですが、今回は2ch同時に動かす必要があるから、

すこしアルゴリズム的には変更しています。

動作チェックにはやはりLCDがあるととても便利です。位相のずれや、現在のソフトの動作状況が

把握できるので、メインテナンスポートをつけておいてよかったです。

ソフト作成時の動作の様子。

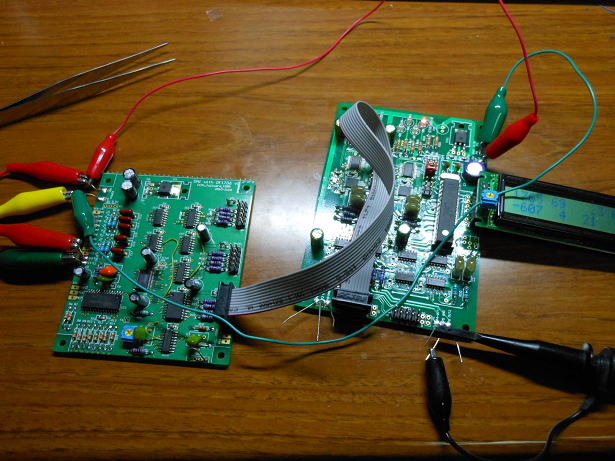

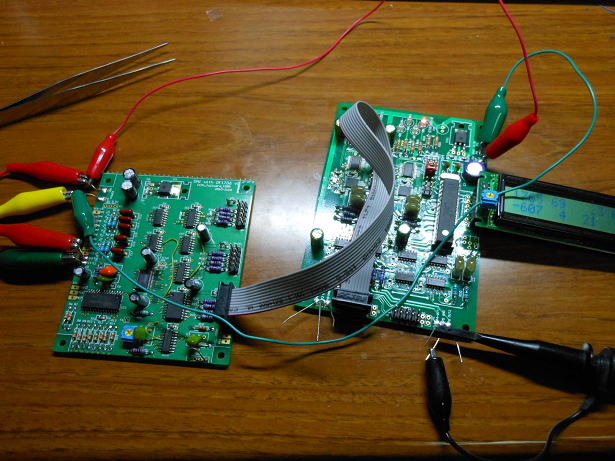

DAIと接続してみましょう!

ソフトがほぼ完成したこともあるので、DAIと接続して動作確認をしてみましょう。

DAIはDAI for DF1706を用意してきました。ちょうど、この基板についてはリニューアル版を作成中です。

しかし、久しぶりに動かすな〜!!

DAIを用意しました。

DUALジッタクリーナの接続は

DAIの出力信号のなかのビットクロック(BCK)とシステムクロック(SCK)の2つをジッタクリーニングするので、

下図の様な接続としています。

ジッタクリーナの接続

DAIとジッタクリーナを接続してみました。接続は1本の10Pケーブルで接続します。

DAIとジッタクリーナの接続の様子。

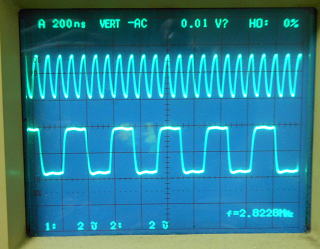

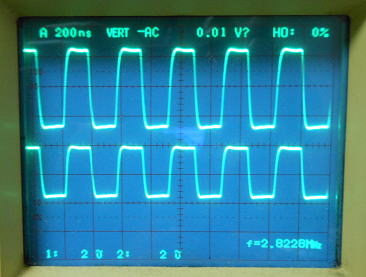

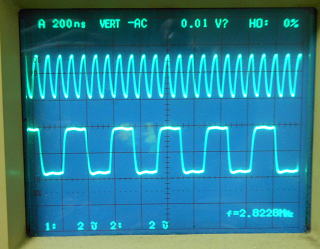

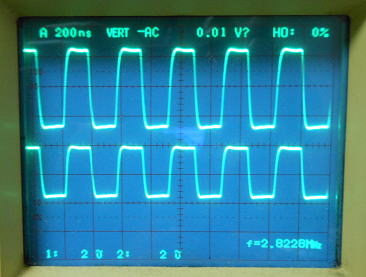

信号を確認しておきましょう。入力は44.1kHzの標準的なSPDIFをDAIに入れています。

このとき出てくる信号の周波数はビットクロックが2.8224MHz、システムクロックは11.2896MHz

になります。とくにBCKについては入力と出力の位相の一致が必要です。

オシロの波形から位相もよく一致していることを確認しました。

ジッタクリーナの出力(上:システムクロック、下:ビットクロック)

出力(上:入力のBCK、下:出力のBCK) 位相はばっちりあっています。

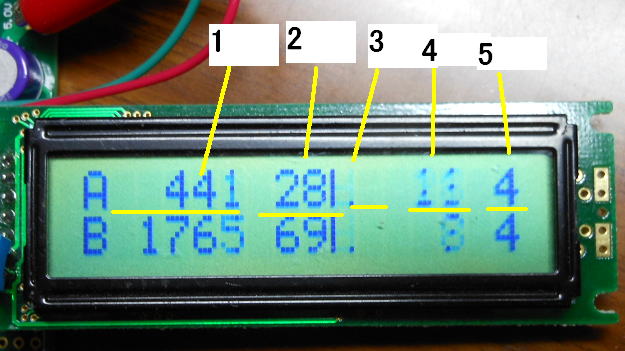

メインテナンスポートの出力は?(備忘録)

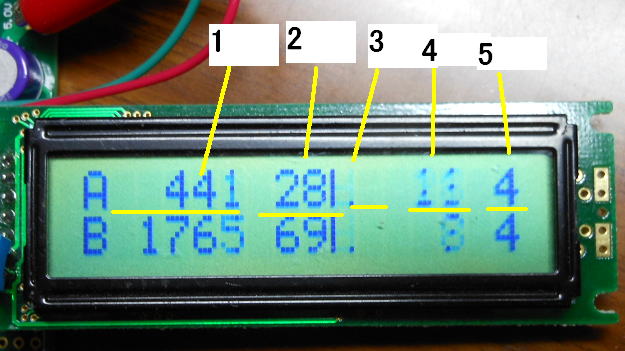

ほぼ完成版のソフトにおいてメインテナンスポートにLCDを接続した場合の出力表示は

下図のようになります。備忘録のためにまとめておきましょう

備忘録用。メインテナンスポートのLCD表示

表示内容はそれぞれ下記のようになります。

1.周波数測定値

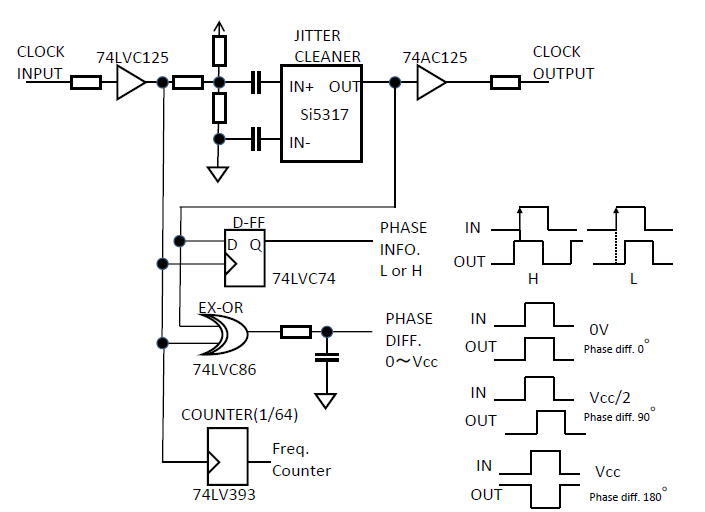

周波数測定は実際の周波数を64分の1に分周し、その後に10mS間でのカウント数を周波数測定値として

表しています。図の例で1CH(A)441だと441÷(1/64)÷(1/100)=2822400(Hz)になります。すなわち

FS44.1kHzでの64FSですね。2CH(B)1765だと1765÷(1/64)÷(1/100)=11.296(MHz)になります。

この周波数測定が数値で4以上(約26kHz)変化した場合に、周波数が変更されたと認識してジッタクリーナの

再調整にはいります。

2.プランNo

これは周波数測定値からSi5317に設定するプランNOを表示します。プランNOはSi5317のマニュアルに

詳しく掲載されていますが、図の例で28は2.7〜2.9MHz、69は11〜12MHzでの範囲でロックするとなっています。

このソフトでは1〜100MHzでロックできるようにすべてのプランNoのデーブルをもっています。

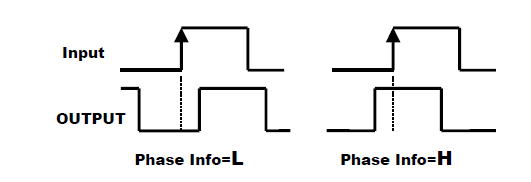

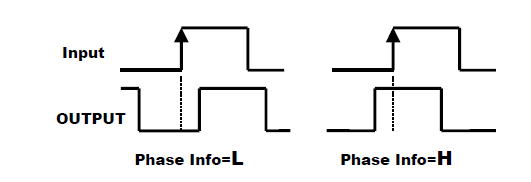

3.位相情報

位相情報は入力と出力のどちらが位相が遅れているか、進んでいるかを示します。出力信号の位相が遅れて

いる場合はL、進んでいる場合はHとなります。

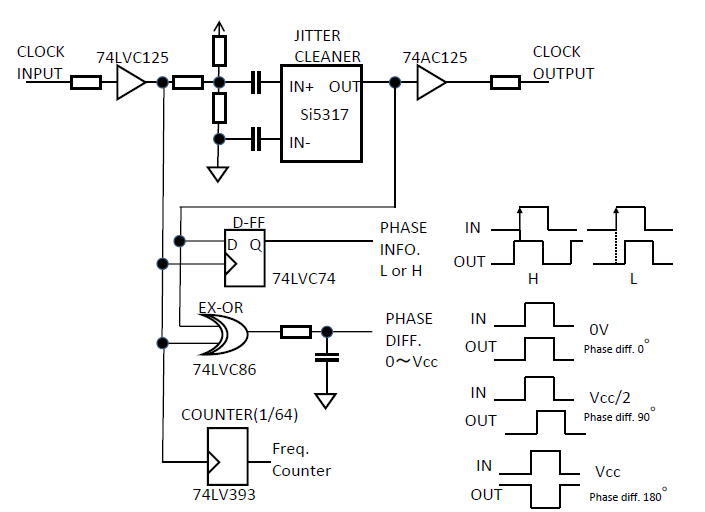

4.位相差情報

位相差情報は下図のように、位相差に応じた出力が得られます。これは入力と出力をEX-ORをとって、

その出力にLPFを通すことで実現できます。入力と出力の位相差がゼロであれば位相差情報は0、

位相差が180°であれば位相差情報は1023になります(実際にはEX-ORのロジックICの遅れ等で

完全なゼロや1023になることはありません)

5.ステージNo

これはソフトウエア内での処理状況を表すもので、下表のようになります。ジッタクリーナがロックして

位相調整をするプロシージャを示します。

| ステージNO |

動作状況 |

| 0 |

周波数測定が完了し、ジッタクリーナに所定の定数を設定。

入力周波数が変化した場合は、ステージNo.0から開始する。

|

| 1 |

PLLのロック待ち。具体的にはLOLが”H"レベルの間待機。 |

| 2 |

位相差情報が安定するまで待機。PLLがロックしても、実際には入力と

出力の位相差の変動があるので、位相差情報(AD値)を監視し、

その値が安定するまで待機。 |

| 3 |

入力と出力の位相差が一致するように強制的に調整。

(JP3あるいはJP4のS1が短絡されている場合に動作)。 |

| 4 |

入力と出力の位相差が一致する方向に定期的に微調整

約20ms毎に0.2nSの位相を調整する。。

(JP3あるいはJP4のS3が開放されている場合は継続動作。

短絡されている場合は約1分程度動作した後は、ステージNo.5に以降) |

| 5 |

PLLはフリー動作 |

ついでに

ジッタクリーナの基本的な回路です。詳しくは製作マニュアルに記載します。

ソフトの修正も進み動作もだいぶ落ち着いてきました。

さて、そろそろリリース?

この基板はこちらでも、登場しています。

↓

RenewDAC1704は復活するか? の巻き

(おしまい?)