ロジックテスターとはロジック回路のHigh/LowレベルあるいはHi Impedance状態を検知してLED等

で知らせてくれるプローブです。それほど高いものでもありませんし、自作しても知れています。

それに、手元にオシロやテスターがあれば、必須というものでもありません。

いわゆるロジックテスターです。2000円もだせば購入できます。

ちょっと Tea Time!? ロジックテスター考(頭の体操) 2025.9.7

ロジックテスターとはロジック回路のHigh/LowレベルあるいはHi Impedance状態を検知してLED等

で知らせてくれるプローブです。それほど高いものでもありませんし、自作しても知れています。

それに、手元にオシロやテスターがあれば、必須というものでもありません。

いわゆるロジックテスターです。2000円もだせば購入できます。

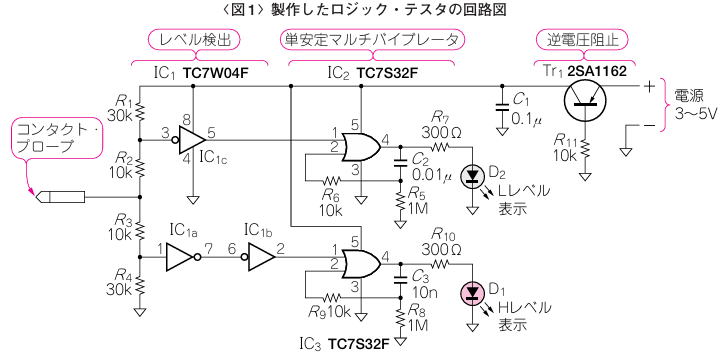

引用: https://www.cqpub.co.jp/toragi/TRBN/trsample/2002/tr0211/0211sp8.pdf

自作しても、大した部品ではありません。点滅させる必要がなければ、前段のレベル検出だけでいいでしょう。

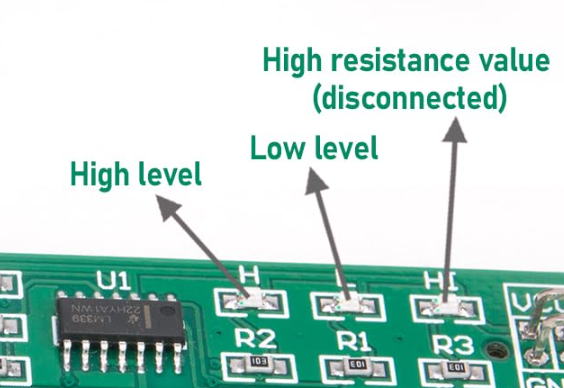

安価なものも出ています。ほとんどキットみたいな感じだなあ〜。

安価なものですが、3STATEの検出ができるようになっています。

LM339だから4回路のコンパレータが使われています。

必要性は突然に!

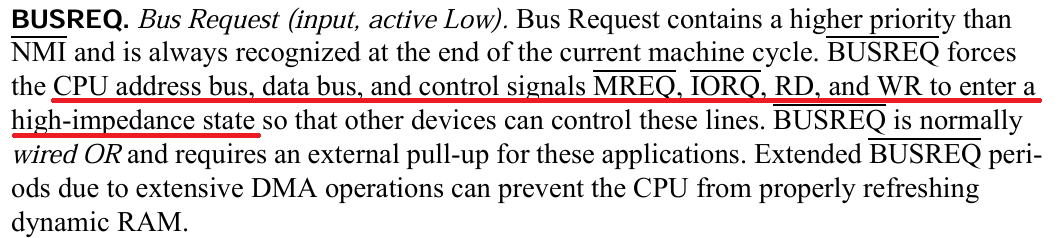

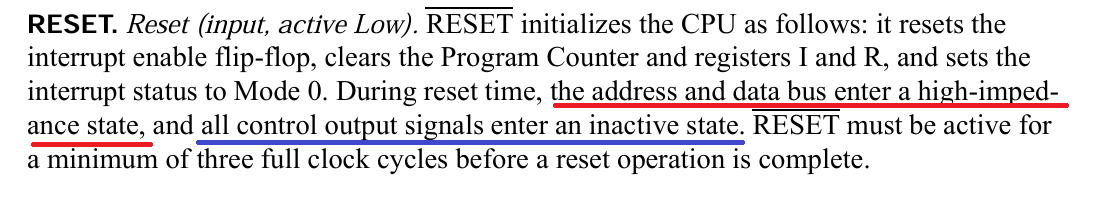

以前にZ80を使ったときに、RESETをかけた場合は、データとアドレス線に加えて、

制御線(MREQ、IOREQ,RD,WR)もハイインピーダンスになるかと思っていたのですが、

どうやら違うようです。BUSREQの場合は、そうなるのですが、RESETの場合は、

制御線については非アクティブ(Highレベルのまま)になるようです。

BUSREQをかけた場合は、データとアドレス線に加えて、制御線(MREQ、IOREQ,RD,WR)もハイインピーダンスになります。

RESETをかけた場合は、データとアドレス線はハイインピーダンスですが、制御線(MREQ、IOREQ,RD,WR)は非アクティブ(High)のままです。

何が問題かというと、データ線やアドレス線、そして制御線はすべてプルアップをするようにしています。

そうすれば、入力端子がフロートにならないので静電気に対しても強くなります。

しかし、単に電圧の測定では、プルアップした状態だと活線状態のレベルHighの場合と、

Hi Impedance状態でのHighレベルの区別がつきません。

そのため、RESETをかけた状態で、制御線を他のICで操作しようとしても上手く動かなくて、

デバッグに時間がかかったことがありました。

もっと高精度なロジックテスターを考える!

そこで、ロジックテスターの機能として、プルアップあるいはプルダウンが行われている環境でも、

ロジックレベルのHigh/LowならびにHi Impedanceを判別することができないかを考えてみました。

いわゆる頭の体操です。

方法としては、割と簡単です。

観測するラインに対して、すこし負荷電流をかけることで、そのときの電圧変化を調べる方法です。

すなわち、

ロジック回路から出力されている場合(低インピーダンスのとき)は、少々の負荷がかかっても電圧はほとんど変化しない。

出力はHi Impedance(高インピーダンス)のときは、負荷がかかると電圧変化が、負荷に応じて変化する。

ということを利用します。

具体的に、たとえば47kΩでプルアップされたラインの電圧が5Vとすると、ロジック出力が生きている場合は、

そこに100kΩの抵抗の負荷をGNDに接続しても、ラインレベルはほとんど5Vのままですが、ロジック出力が

Hi Impedanceのときは、ライン電圧は3.3V程度まで低下するからです。

具体的な回路を考える

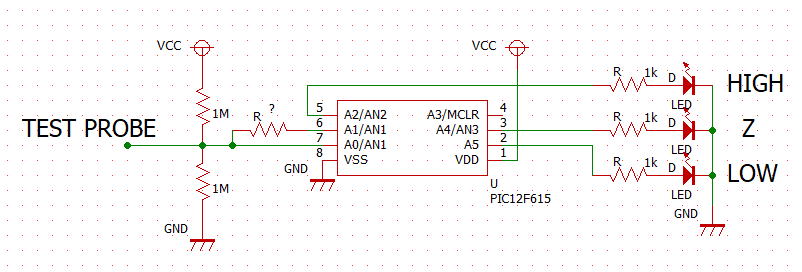

極めて簡単な回路です。要はADコンバータでの電圧計測と、負荷をかける抵抗のみです。

A0/AN1がアナログ入力で、これでライン電圧を測定します。A1は負荷をかけるポートで、

抵抗Rを介してVCCあるいはGNDに向けて負荷をかけます。もちろん、負荷なしも可能です。

TEST PROBEにVCCとGND間に1MΩの抵抗を接続しているのは、単に入力端子(A0)が

フロート状態になるのを嫌っただけです。

まずはこんな回路で考えてみましょう!

どうなるかな?

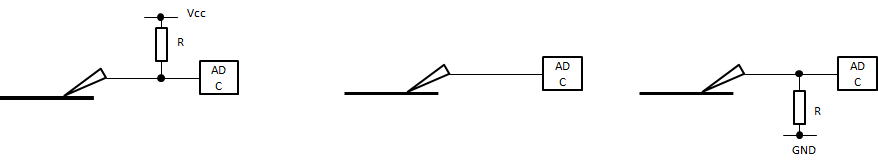

ラインへのプルアップの有無で考えてみます。

(1)プルアップ抵抗がないラインを計測した場合\

(a)VCCへ負荷有りの場合 (b)負荷なしの場合 (c)GNDへ負荷有りの場合

RΩの負荷をかけた場合の測定される電圧変化(プルアップ抵抗なしの場合)

| 測定電圧 | 判定方法 | |||

| ライン状態 | VCCへ負荷有り | 負荷なし | GNDへ負荷有り | |

| HIGH | VCC | VCC | ほぼVCC | 負荷有無でもほぼVCCであればHIGHレベル |

| LOW | ほぼゼロ | ゼロ | ゼロ | 負荷有無でもほぼゼロであればLOWレベル |

| Hi Imoedance | VCC | 不定(Vcc/2くらい) | ゼロ | 負荷有無で電位が変る場合はHi Impedacece |

(2)プルアップ抵抗があるラインを計測した場合

(a)VCCへ負荷有りの場合 (b)負荷なしの場合 (c)GNDへ負荷有りの場合

RΩの負荷をかけた場合の測定される電圧変化(プルアップ抵抗有りの場合)

| 測定電圧 | 判定方法 | |||

| ライン状態 | VCCへ負荷有り | 負荷なし | GNDへ負荷有り | |

| HIGH | VCC | VCC | ほぼVCC | 負荷有無でもほぼVCCであれば出力ONでHIGHレベル |

| LOW | ほぼゼロ | ゼロ | ゼロ | 負荷有無でもほぼゼロであれば出力ONでLOWレベル |

| Hi Imoedance | VCC | VCC(PULL-UPのため) | VCC−α | GNDへの負荷でαの電位低下があれば、出力はHi Impedance だが、ロジックレベルはHigh |

ラインがプルダウンされた場合は、プルアップの場合と考え方は同じなので省略です。

負荷をかけたときの電圧変化を観測すれば、ラインがアクティブ(High/Low)かHi

Impoedraceかがわかりそうです。

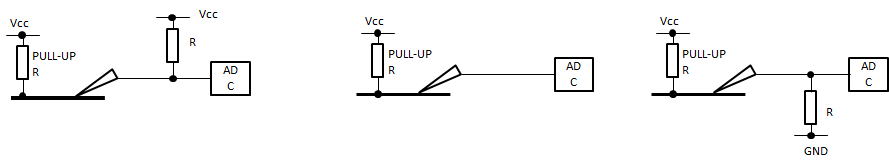

負荷抵抗Rの値はどうする?

ロジックテスターですから、パッシブでなければいけません。すなわち、本来はプローブを当てることで電圧が変ってはいけません。

しかし、今回は負荷をかけて電圧変化をみるわけですから完全なパッシブではありません。重要なことは、ロジックレベルが変る

ような負荷をかけてはいけないということです。

CMOS回路だと、Vcc/2の電位を境にしてHigh/Lowレベルがかわりますが、

メーカの保証値としては0.7xVcc以上がHighレベル、0.3xVcc以下であればLowレベルとしているところが多いようです。

とはいえ、3.3Vのロジック出力で5Vのロジックが駆動できることを考えると、実力的な閾値は0.5xVccに近いところでしょう。

かといって、あまり負荷をかけすぎるのもなんなので、負荷による電圧変化は0.1xVcc以下に抑えるようにしましょう。

となると、Rの値を試算してみます。

| プルアップ抵抗値 | Rの試算値 |

| 4.7kΩ(Wired ORだとこのくらいな?) | 42kΩ |

| 10kΩ | 90kΩ |

| 20kΩ | 180kΩ |

| 47kΩ(これが多いと思う) | 420kΩ |

となり、プルアップ抵抗が47kΩだとすると負荷抵抗Rは470kΩとかなり大きくなります。

ADCの入力インピーダンスがかなり高くないと、うまく測定できないかもしれません。

それに負荷抵抗を470kΩにした場合に、プルアップ抵抗が4.7kΩと低い場合は、

電圧電化が0.01xVccになるので.上手く変化が捕らえらえるかどうかが心配です.

回路は要再考かなあ〜

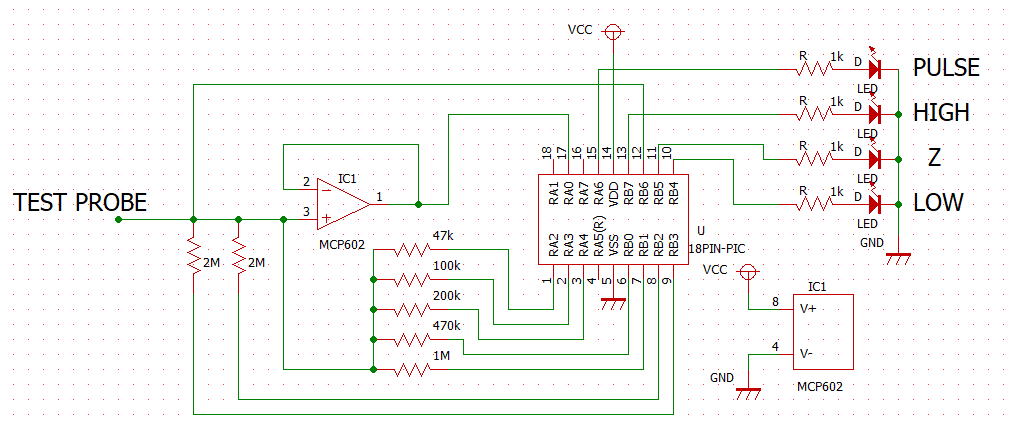

負荷抵抗を調整できるようにすることと、ADコンバータの精度を保つために

前段に単電源OPアンプを1個入れてみました。

負荷抵抗を調整する必要から8PinのPICでは足りないので、18PinのPICに変更です。

そうなると、足が余り過ぎるので、クロック判定機能も入れてみました。

負荷抵抗の調整と、ADCの前にOPアンプを挿入です。

なんか、ロジックテスターとしては回路が複雑だなあ〜。

一度試作してみるかな?

(つづく?)