ちょっとTea Time!? 分解能を上げたタイムアライメントを考える!の巻き。 2024.9.10

現在、デジタルチャンネルデバイダであるDIV5142の更新を検討しています。

あわせてホーンなどで必要なタイムアライメント機能も検討していますが、

こんなご意見をいただきました。

面白そうな話なので、おもわず反応です。

大きなDELAYはPCM5142に任せて、細かいDELAYを別途H/Wに任せるようにすれば、かなり高精度なタイムアライメント機能が

実現できるかもしれません。

まあ、私の耳はそこまで高精度でないので、ちょっと頭の体操です。

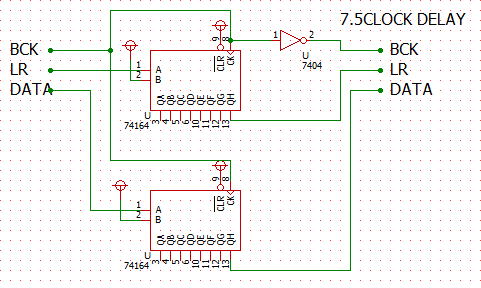

回路は簡単!

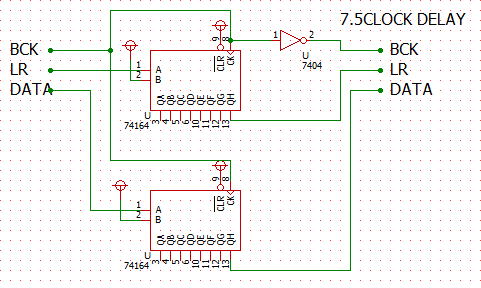

タイムアライメントといっても、回路は簡単です。PCM信号のDATAとLRクロックをずらすだけです。

ずらすためのクロックは勿論BCKを使います。ずらずためにはシフトレジスターを使います。

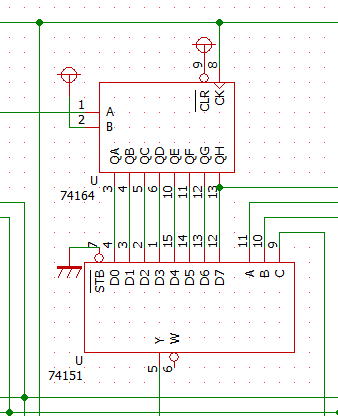

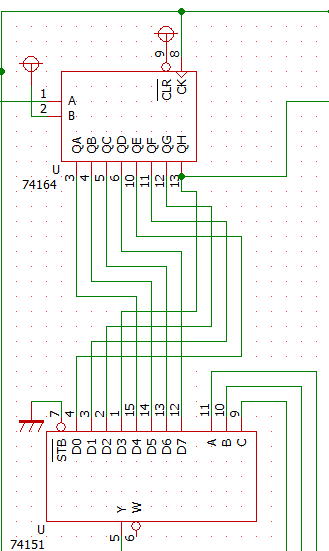

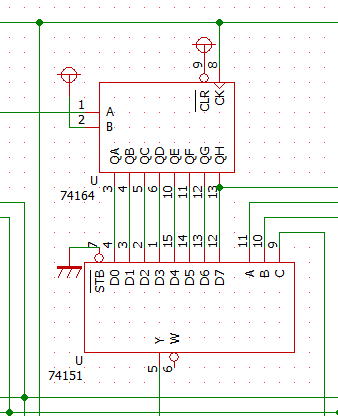

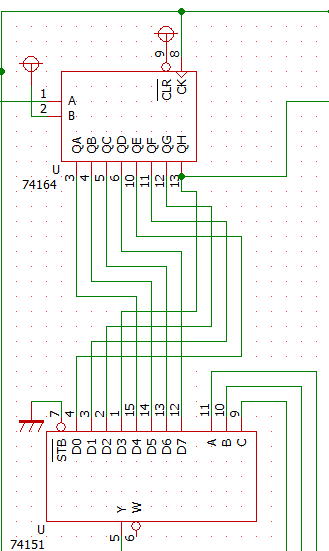

たとえばBCKで8クロック遅らせるには、下図の回路で事足るはずです。

これでBCKの8クロック分(正確には7.5クロック)の遅延

BCKで8クロックは44.1kHzの場合で時間に換算すると2.83usです。

距離に換算すると約1mmです。サンプル周波数が周波数192kHzであれば、約0.22mmです。

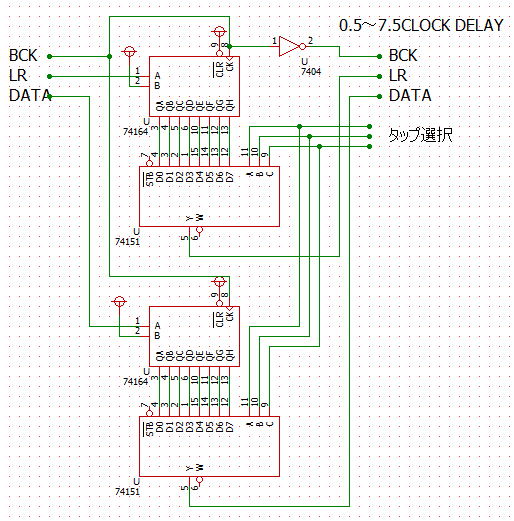

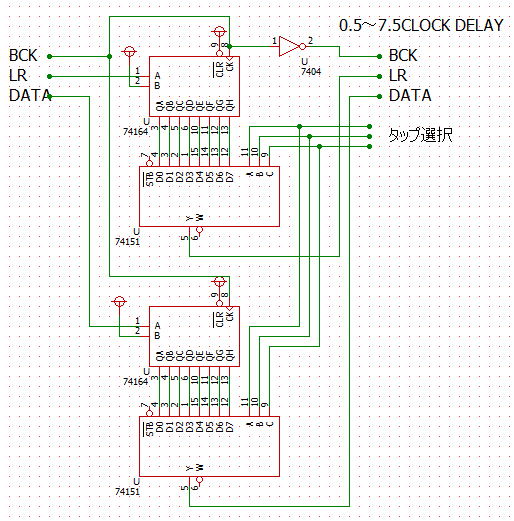

遅延時間を調整するには出力するタップを選択すればいいのですが、いちいちジャンパー線

を変更するのも大変です。ということで、タップの選択もセレクター機能を使えばスマートです。

タップの切替を追加してみる

タップの切替分解能はおそらく4タップ毎程度(0.5mm)でも十分な気がしますが、

ついでなので全てのタップで切替可能にしてみましょう。この場合は44.1kHzの場合でも

0.12mmの分解能が得られます。

タップの切替を追加してみました。

LRクロック幅で調整できるようにすると

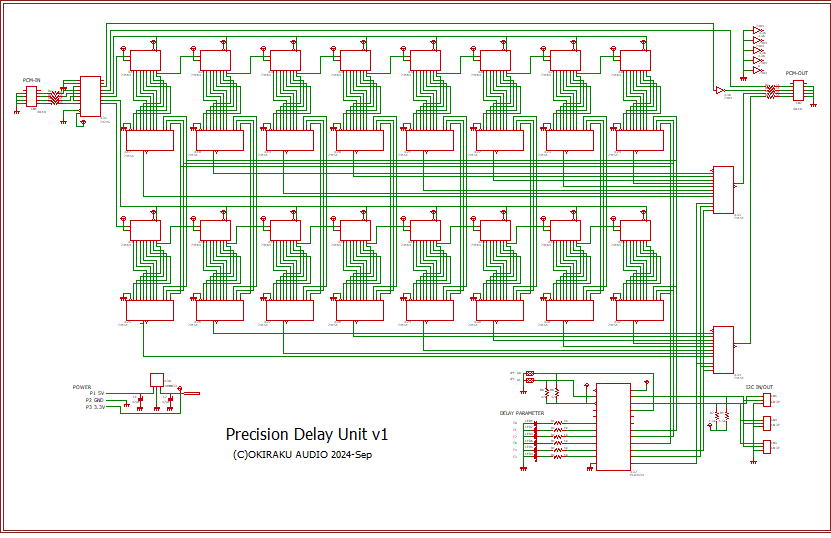

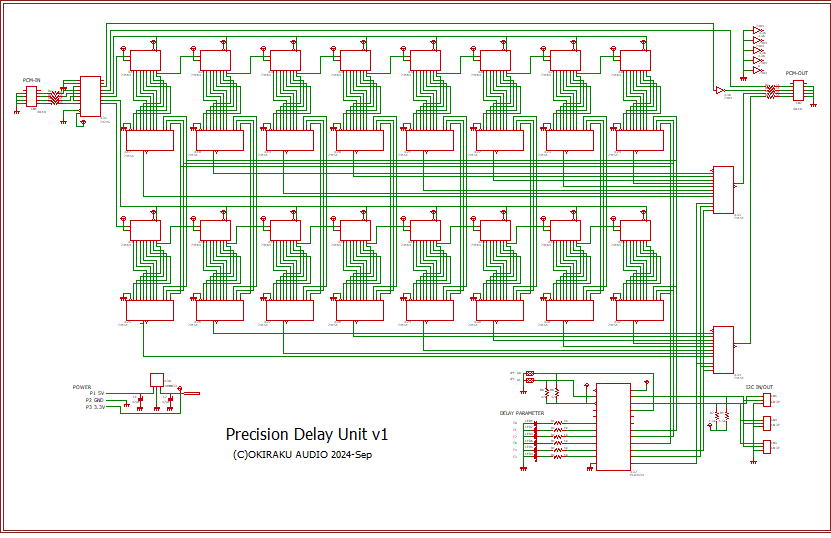

LRクロック幅はBCKの64個分ですから、8クロック遅延回路を8個を単純に並べれば済みます。

もう、完全に力技です。

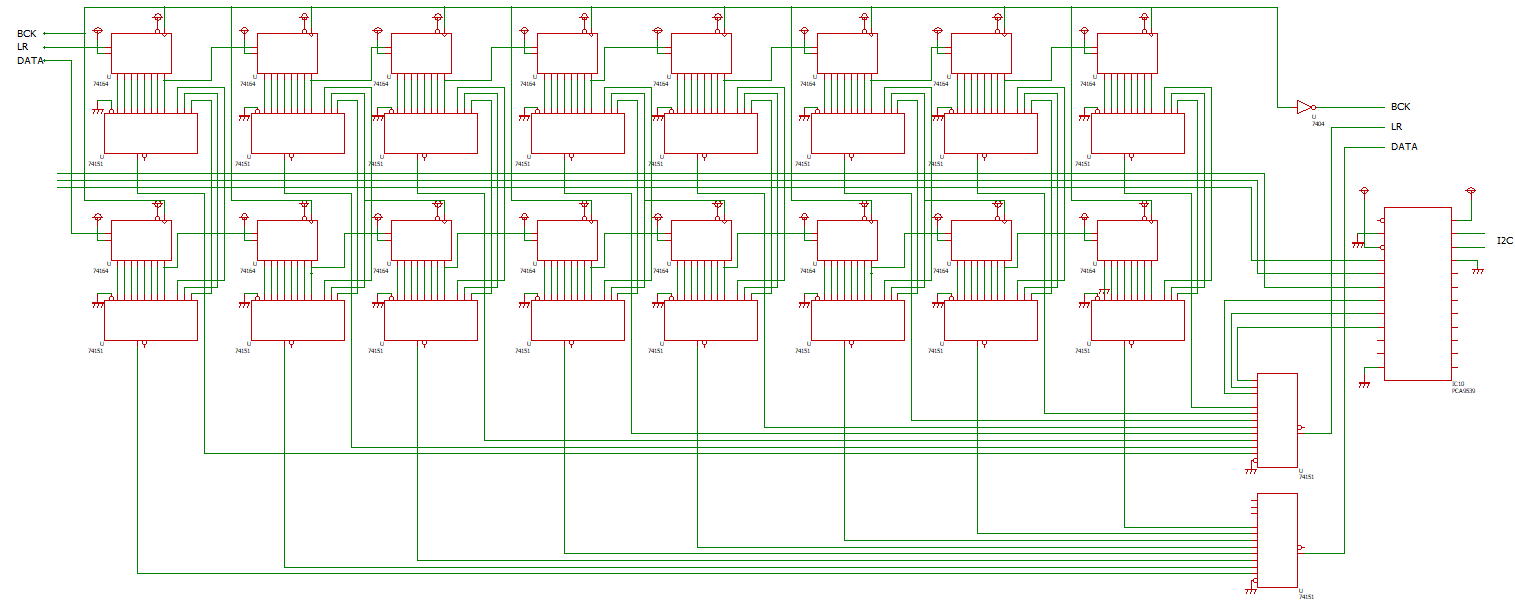

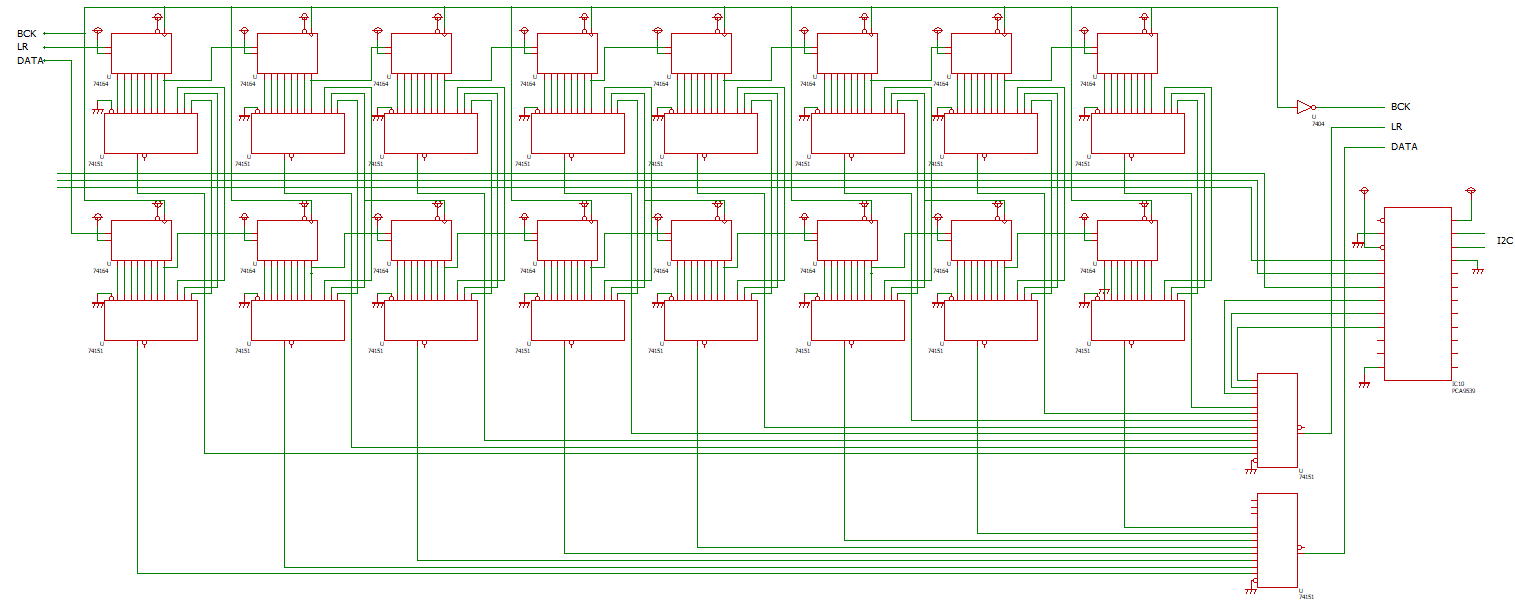

全体の回路図はこんな感じでしょうか。ICの型番とかわからないですね。

描いてみて気付きましたが、BCKのドライブがきつそうです。

全部で16個のシフトレジスタを駆動しないといけないので、8個毎に分割して

ドライバを入れておいた方がよさそうです。

トータルで35個のICが必要です。あ、ドライバを入れると合計36個かな。

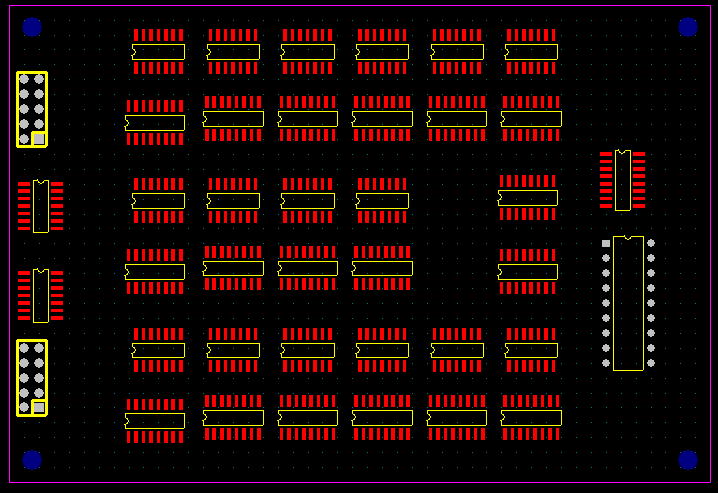

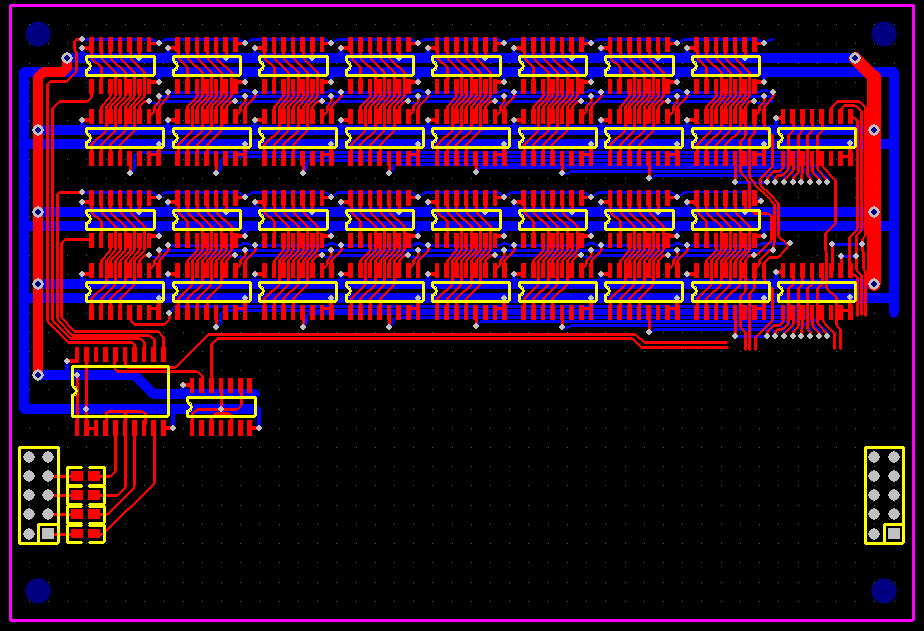

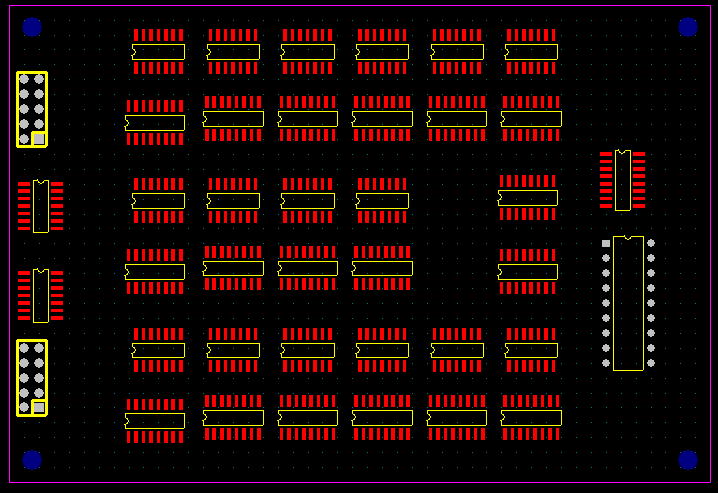

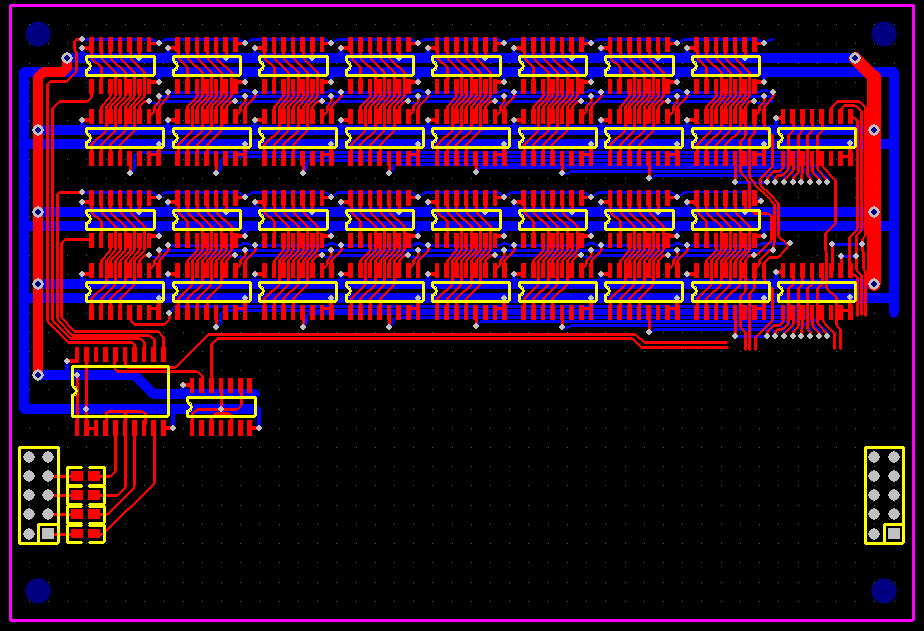

基板に載るかな?

載りそう?

35個程度のICなので載りそうです。あ、配線できるかどうかは別だなあ〜。

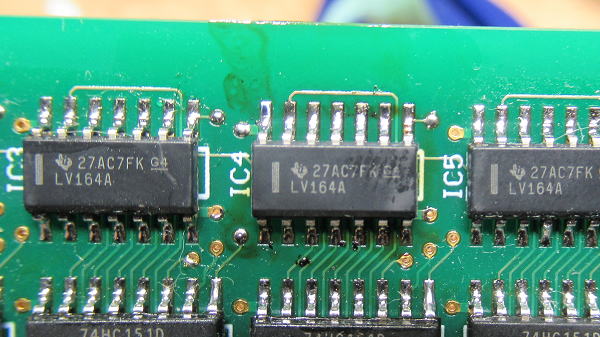

この位のICの数だと大丈夫でしょう。

配線できそうかな? 2024.9.11

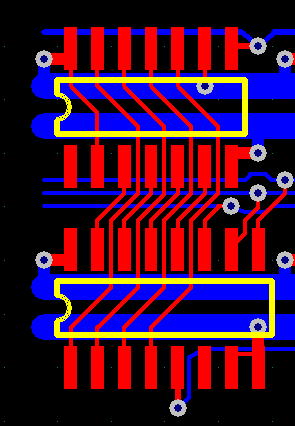

配線上の最大のポイントは、繰り返し部分となる下記の部分を以下にコンパクトに

配線するかになりそうです。

この部分をコンパクトに配線することが肝要です。

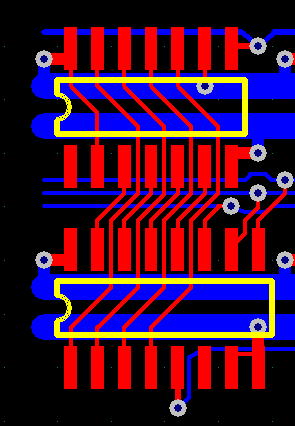

回路図は無視しましょう!

ICのピン配置を見ると、下記のように配線できそうです。

シフトレジスタ出力Qnとセレクタ入力Dnの番号が不一致になってしまいますが、

そんなものは選択時の値を変更するだけで済みます。

こんな形で配線するとコンパクトです。

パターンに併せて回路を書くとこんな形になります。

パターンに併せて回路図を変更です。

余裕で収まりそうです

繰り返しパターンのところを小さくできたものだから、それらをギュッと押し込んだらかなりコンパクトになりました。

あとは、電源部分とI2C素子だけですが、かなり余裕をもって収まりそうです。

となると、マイコンでも搭載してスタンドアロンで使えるようにしてもいいかも?と思ったりですが、

これだけで遅延できる量はわずかなので、多分使い道がないでしょうね。

かなり余裕をもって収まりそうです。

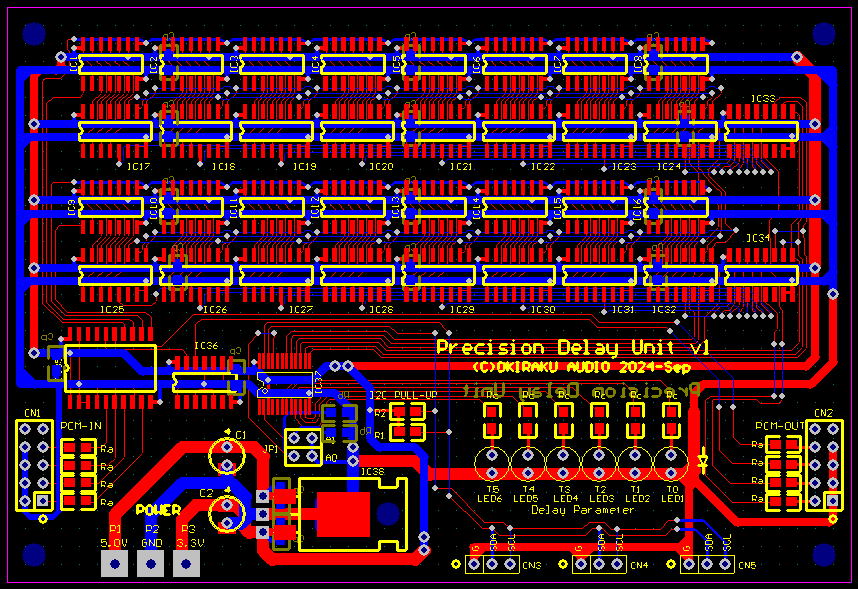

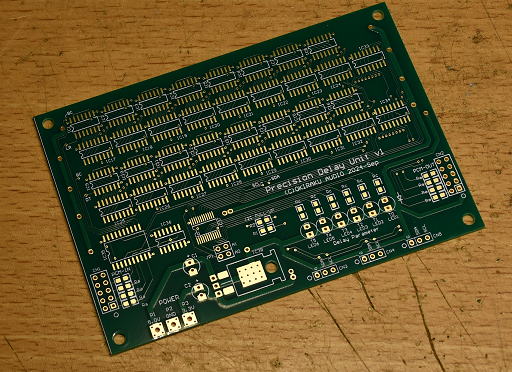

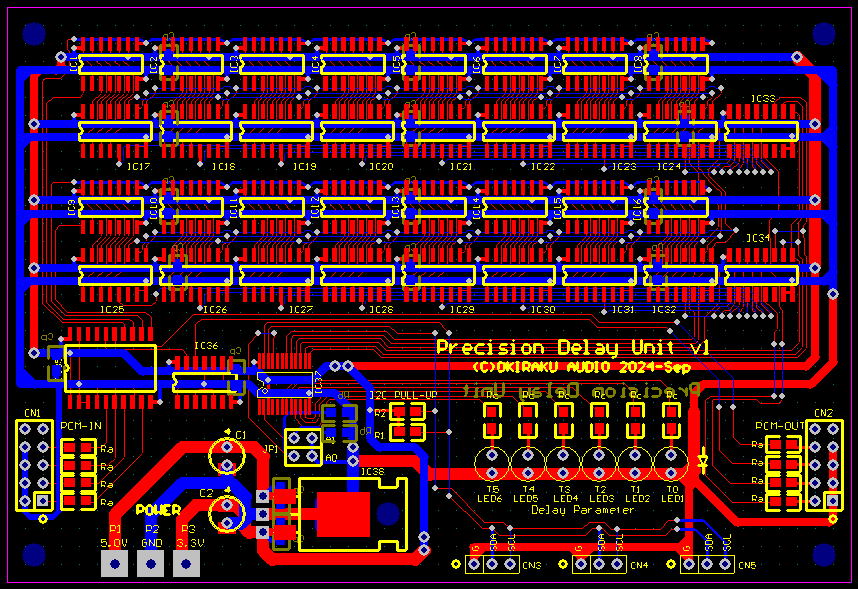

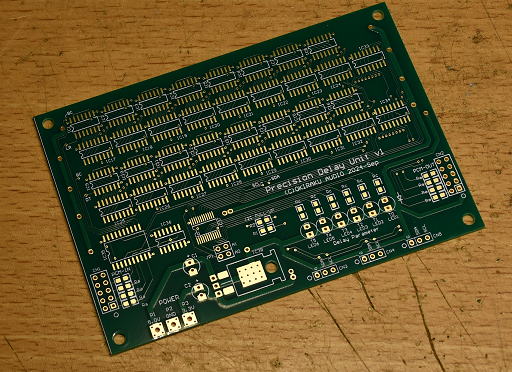

まずはアートワーク完成かな 2024.9.12

スペースが結構あまることもあり、折角なので設定値をLEDで表示する機能も追加しました。

まあ、なくても大丈夫です。というか、ケースに入れると見えなくのでデバッグ用途がメインになりそうです。

こんな形でアートワークができました。

あとは、忘れないうちに回路図を書いておきましょう。

回路図です。 PrecisionDelay.pdf へのリンク

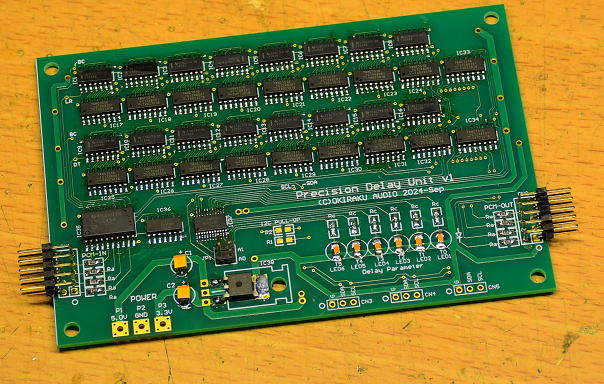

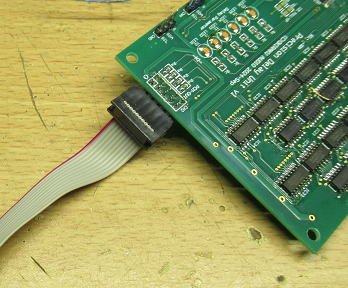

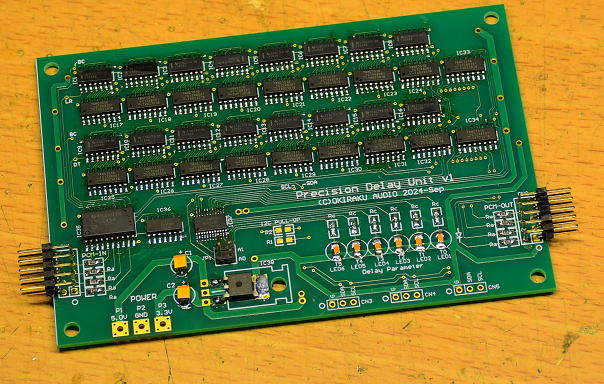

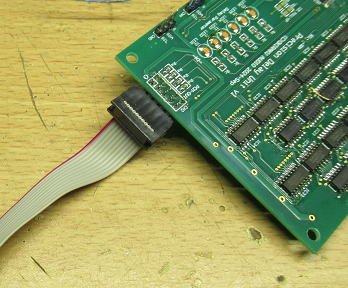

基板ができてきました。 2024.11.11

夜な夜な実装 2024.11.16

秋の夜長に、ビール片手に実装です。すべてSMDなので、リード線を切ったりする必要がないので、

お気楽な半田付けです。ただ、血中アルコール濃度が高めだったせいか、組みあがって確認したら、

ICの向きが2つ反対になっていました。 酒気帯び半田ゴテのバツだなあ〜。

一応、すべての部品が実装できました。

動作確認にかかりましょう! 2024.12.2

今回製作した基板群については、このディレイ基板を除いて、動作確認が終わりました(色々と

修正は必要でしたが)。最後に、これにとりかかりましょう。

確認方法は?

こんな構成で確認します。DACは2台使用して、その出力位相の変化を観察します。

DACはなんでも良いのですが、.手元で直ぐに動くものを調達です。

その前に、.まずは単体機能からチェックです。

まあ、そうだよね!信号が出ません(笑

まあ、案の上ですが単体で動かして信号がでるか確認のためPCMを入力に入れますが、

出力はうんともすんとも言いません。オシロで信号を追いかけて、色々と間違っているところを

潰していきます。

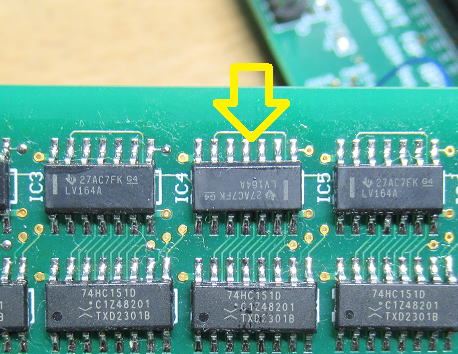

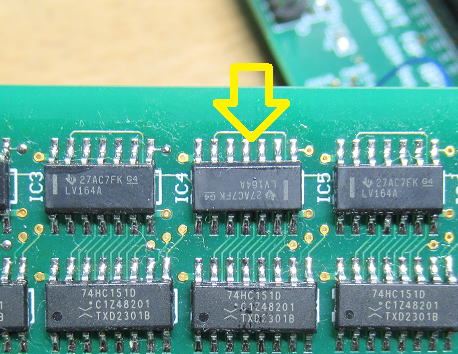

(その1)ICの向きを一つ間違えていました。

最初に電源をいれてもLEDすら点灯しないので、レギュレータを調べたらアッチチ。

出力電圧も1.5V(本来は3.3V)しかありません。電源ラインの抵抗を調べても10kΩ程度と

高いので、こりゃどれかの素子が悪さをしている可能性が高いです。

で、調べるとICが1個反対を向いていました。何度も確認したとおもうのだけど、

やっぱりミスってあるのですね。

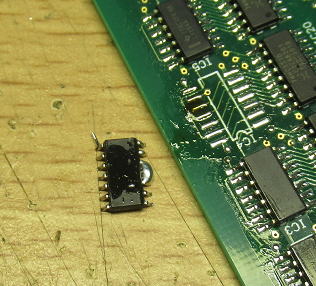

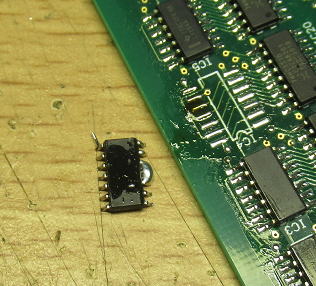

これは取り外して、交換です。流石に再利用は無理でしょう。

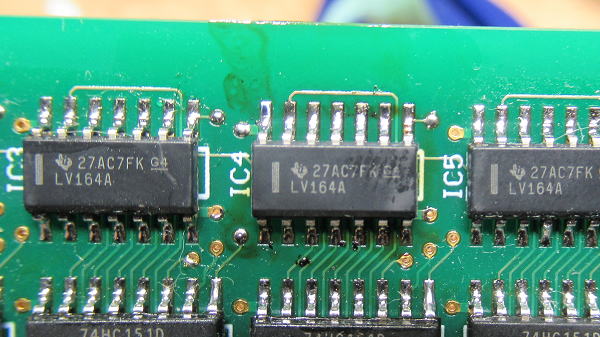

逆向きのICがありました。

向きを間違えたICは廃棄です。

これで向きは揃いました。

(その2)配線が抜けていました

ICを取り付け直したら、LEDが点灯するようになりましたが、まだ信号がでてきません。

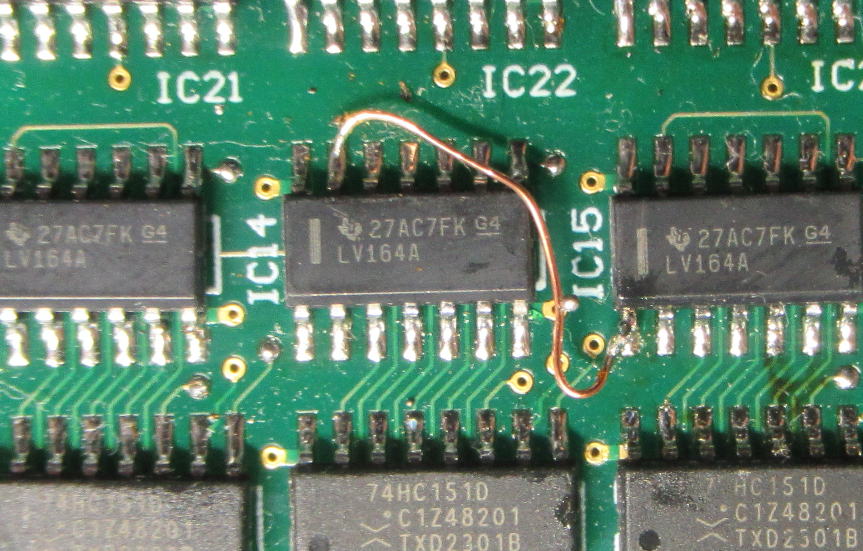

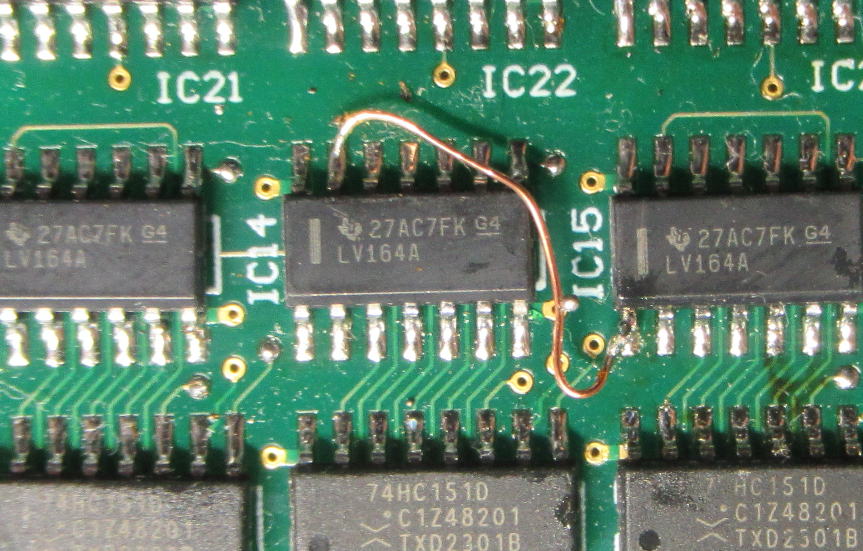

オシロで信号を追いかけると、IC14からIC15への配線が抜けていました。そのためワイヤーを1本追加です。

この部分の配線は同じようなものが続くので、コピペで作成していたはずですが、

コピーの時になんらかのミスをしたのでしょう。まあ、1.27mmピッチなので、まだ修正はできます。

これが0.65mmピッチだと、ちょっと絶望したくなります。

IC14(Pin13)からIC15(Pin1)(Pin1)への配線が抜けていたので修正です。1.27mmピッチなので、まだ修正ができます。

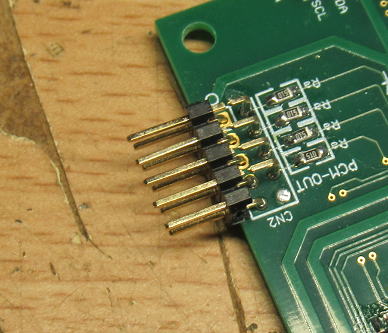

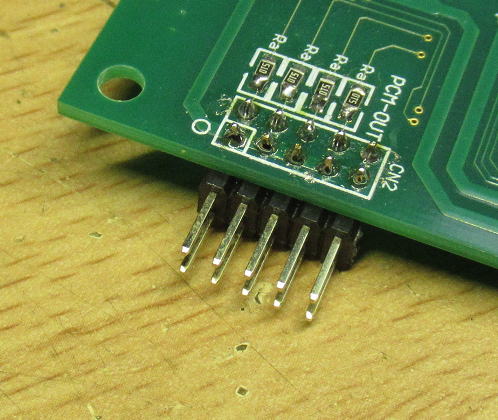

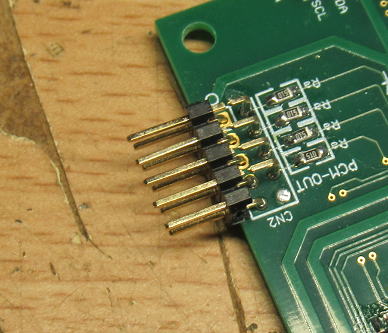

(その3)出力コネクタの列を間違えました

これは完全にポカだなあ〜。

コネクタ直前のダンピング抵抗までは信号は来ているのですが、なぜかコネクタに信号がでていません。

なんと、コネクタの偶数列と奇数列を間違ていました。この手合いのミスは初めてだなあ。

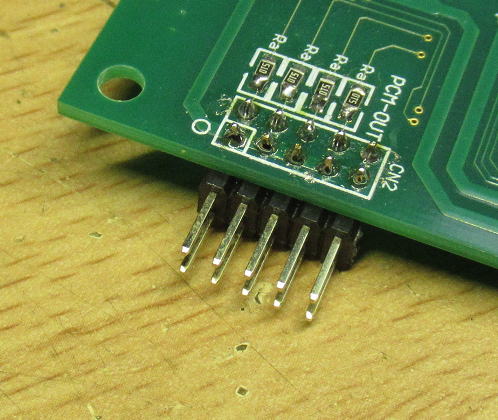

修正として、コネクタを半田面に取り付けました。これで偶数列と奇数列が入れ替わります。

出力コネクタの列を入れ違いしていたので修正です。 基板の裏側にコネクタ端子を取り付けです。これで列が入れ替わります。

こんな形でケーブルを接続です。

これでなんとか信号がでてきました。

確認には2台のDACを使います

次のような構成で接続して、2台のDAC間の信号の位相変化を観察します。

(ソース)Renew SRC4137 ->FESP5142 (基準)

|->ディレイ基板->DAC4497-2.1 (観測用)

こんな形での総動員でのチェック体勢です。

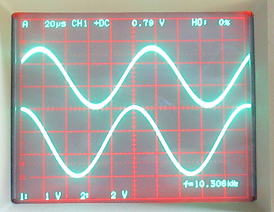

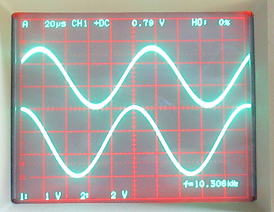

なんか変だけど、遅延はしている

プログラムでは遅延量が0から1LRクロック分まで64分割で連続的に変化するようにしているのだけど、

動きがぎこちない。でも、遅延していることは確認できました。まだ、プログラムあるいはハードにバグが

ありそうだけど、明日もあることだし、今日はこの辺でやめておきましょう。

10kHzの正弦波でテスト中。位相はずれているけど、連続的に動かないのはなぜ?

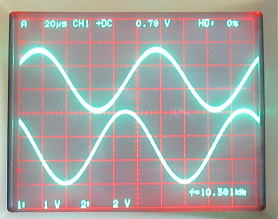

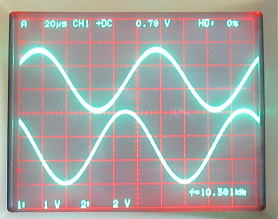

そういうことかあ〜 2024.12.3

DAC出力後のアナログ波形でみると、遅延時間の設定通りにスムーズに遅延しません。

そこで、もとのPCM信号を観察です。LRクロック信号を観察したところ、

スムーズに遅延しています。

あ、そういうことなのね。原因が分かったような気がします。

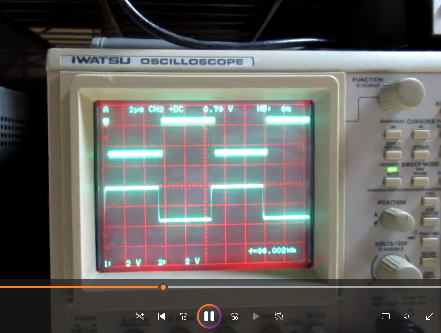

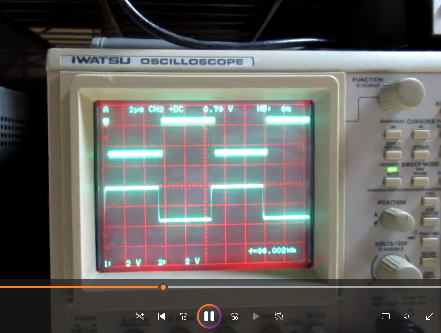

LRクロックの位相はスムーズに遅延しています。<動画>

まず、LRクロックが遅延している中でDACの出力が正常にでているということは、

DATA信号も同様に問題なく遅延しているということがわかります。なんせ、

LRクロックとデータのタイミングがズレようものなら、フォーマットが変わってしまって

いるということですから、アナログ波形は無茶苦茶になってしまいます。

そのため、まずディレイ基板としての動作は問題ないということになります。

LRクロックが遅延しても、DAC出力波形が遅延しない原因は、すなわち

DACの出力がLRクロックには同期していない!

ということがわかりました。LRクロックは単にDACがデータを取り込むために必要な信号であり、

DAC内部で処理をして出力する過程において、LRクロックの立ち上がりや立下りの位置は

関係無くなるということのようです。すなわち、LRクロックが(勿論DATA信号も含めて)多少の

時間がズレたとしても、DATAを取り込むことに関しては問題なく、DATAは一旦バッファーなどに

取り込まれる。そして、DAC内部でバッファにあるデータをシステムクロックに同期して処理がされて

DA出力されるということでしょう。

ということで、DACが稼働中にLRクロックが微妙にずれても、DACのアナログ出力は変化なしです。

ただしLRクロックがある程度大きく動くと、バッファ内のデータが違うものになりますから、

DACのアナログ出力は不連続に遅延が変化するということになります。

これらの確認にはLRクロックに完全に同期するR-2RラダーDACみたいな、ディジタルフィルタが

ないDACをつかって検証するのが良いでしょう。(どこにあるかな?)

どう使うか?

上記のことが分かったことから、このディレイ基板は通常のディジタルフィルタなどが内蔵された

DACでは使えないことになります。じゃあどうするか?

LRクロックの時間遅延を行った場合は、DACを一度リセットして、内部の動作を初期状態にすることで

対応できるかもしれません。となると、現在開発中のDAC179X-I2CやDAC4493-I2Cなどように、

外部からあるいは内部から強制的にリセットがかけられるものが必要ということになるということです。

あるいは、DACの電源を落として再起動させるという手もありそうですが、それは面倒だなあ〜。

さてさて

とりあえず、動作自体は確認できました。そろそろ、他の基板のソフト開発を本格化させましょう!

DACで高精度な遅延量を実現させるには 2024.12.4

DACを連続的に動かした状態で遅延を設定しても、それが反映できない場合があります。

遅延量を正確に反映させるためには、遅延設定後にDACをリセットして初期動作に戻す

必要がありそうです(I2CDACのページを参照)

(つづく)