話の前段はこちら(その1、 その2)

PCM5142をつかってパラメトリックイコライザやグラフィックイコライザが実現できるのがわかったので、

それをシステムに組み込めるような基板化を考えていきましょう。使える場面がいくつもありそうなので、

基板化しておけば複数台使うのに便利そうです。1台はユニバーサルで作ろうかという気になりますが、2台目以降は無理です(笑。

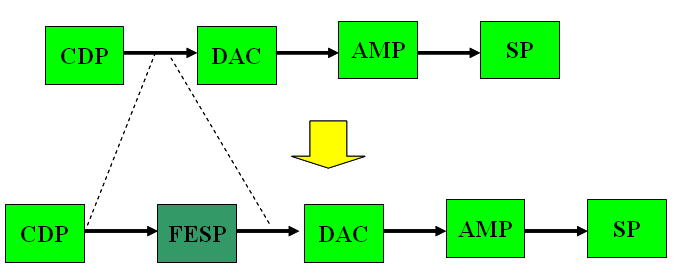

さて、ネーミングですが、文字通り音の入り口であるCDPの信号に加工を行うということでFESP(フロントエンド・シグナルプロセッサ)としました。

CDPとDACの間にこそっといれて劇的な特性の改善を図ります。もちろん内緒で(笑

で、「大作戦!」とつけた理由ですが、これは完全に「スパイ大作戦!」のパクリです(そういえば小さいとき(?)によく見たものです。)

もともと、パラメトリックイコライザやグラフィックイコライザなるものは、どちらかといえば脇役みたいなもので、あえて言えば

必要悪みないなものです。なければないで、それに越したことはないのですが、どうしてもスピーカの口径が小さくて低音がでなかったり、

部屋の共鳴がとれなかったりと、色々な課題があり、それらはこれらの対策に補うものと思っています。そのため、頻繁に弄るようなものでもありません。

どちらかといえば、人目につかずにこそっとつかうようなものではと思ったりしています(このあたりは人それぞれだと思いますが。)

やはり、システムのメインパーツはCDP、DAC、AMP、SPですからね。

で、見た目の構成にはそのメインパーツしか見えないのにしておいて、人に聞かせたときに

「このスピーカは小さい割りに低音でるな〜」

とか、

「バランスの取れた音だな〜」

と思わせたら勝ちです!(笑。

いやいや、自分で聞いたときにより心地よくなれば、それでいいのです。

ということで、スパイみたいにできるだけ目立たない小さいシステムにしようと思って「大作戦」というネーミングにしました。

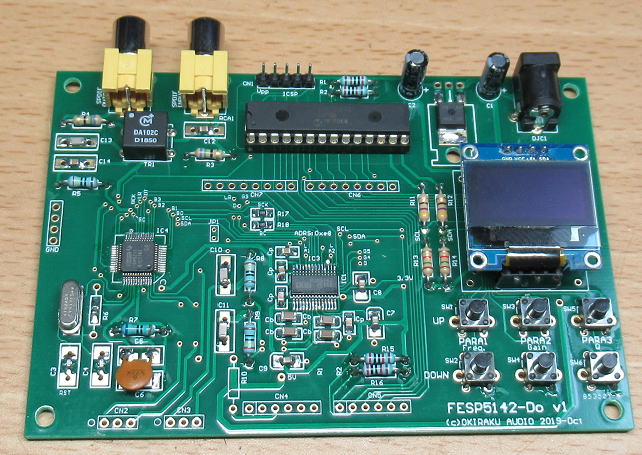

構成は

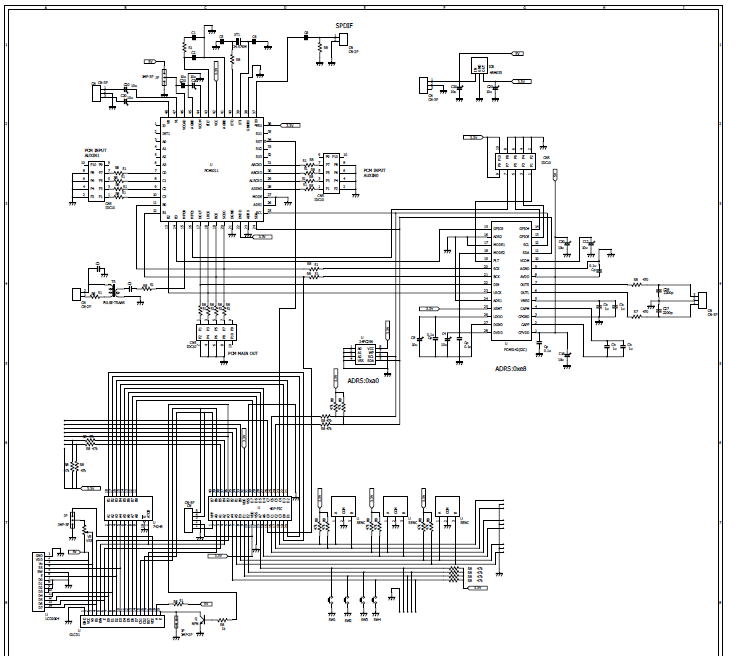

シンプルにSPDIF(同軸)で入力して、同じくSPDIF(同軸)で出力するこをと考えていますが、機器に組み込むことも

想定するとPCM信号での入出力もできると便利です。さらに、DSPとして外付けのDIV5142あたりをつないでも面白いかもしれません。

もっともこの場合ではDIV5142はチャンネルデバイダとは違う目的でつかうことになります。今後、タイムアライメントを含めた

さらに色々な処理を行うには1つのPCM5142だけでは無理なので、複数のPCM5142がつかえるように外付けのDSPとしての

DIV5142をt使うことを想定しています。

で、入出力にSPDIF(同軸)をつかうとなると、信号のエンコード、デコード機能が必要になりますが、これはDIX9211で対応できます。

DIX9211はその他に入出力のポートもいくつかあるので、それらを活用すればかなりシンプルにできそうです。

ただ、信号がDIX9211の周りをぐるぐる回るので、すこし整理しておかないと頭がこんがらがりそうです。

構成の概略は下図のようになるでしょう。

FESPの信号の流れ。DIX9211(あるいはPCM9211)をコントローラとしてつかってシンプルに仕上げます。

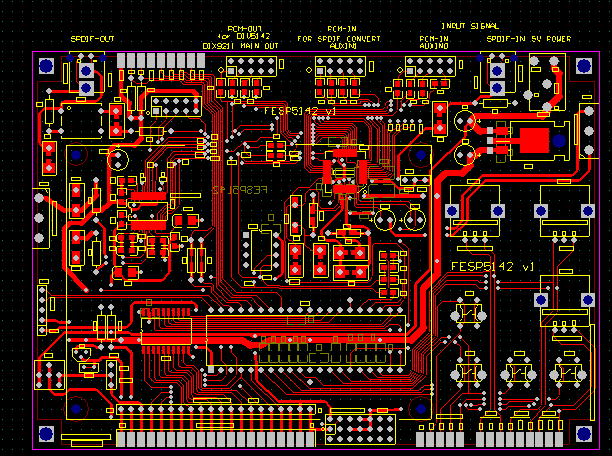

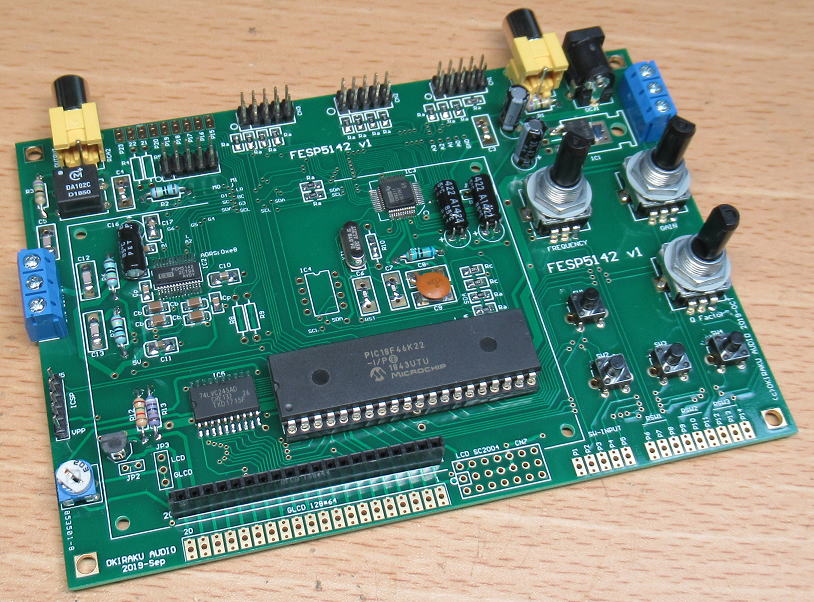

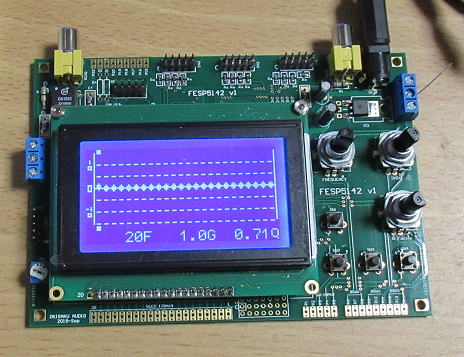

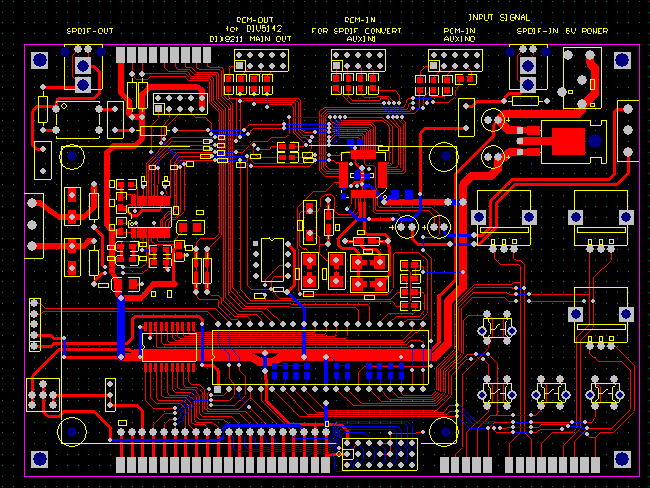

基板のパターンを描いてみましょう!

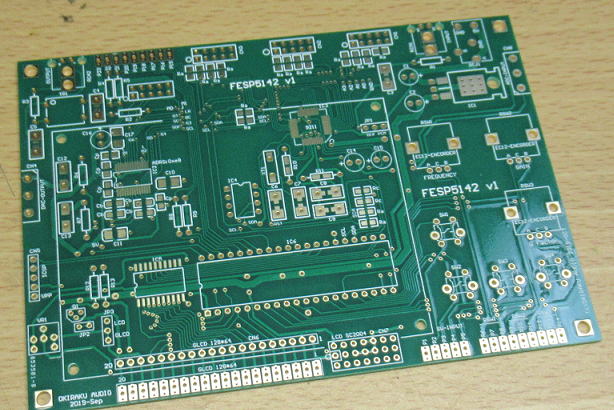

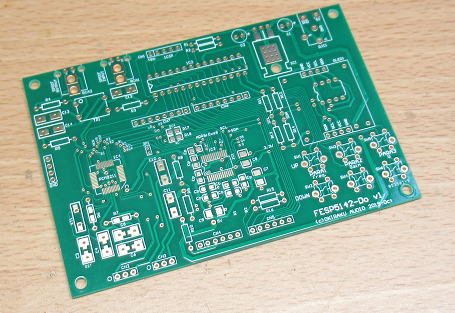

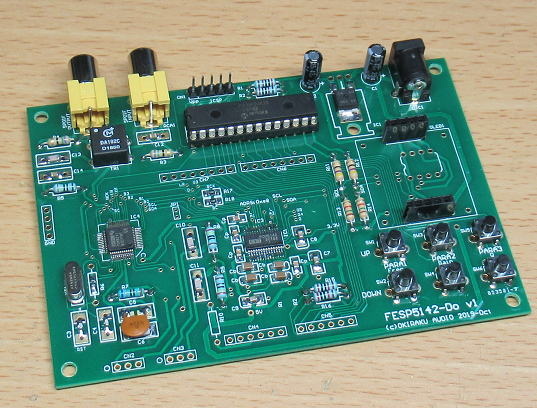

まずは必要な部品と、大まかな配線を描いてみました。

部品点数は少ないのですが、結構配線が多いです。DIV5142などとの接続などの拡張性を考えてためですが、

もっとシンプルなバージョンもあったほうが面白いかな〜と。こそっとDACの内部に入れてしまうドーピングタイプです(笑。

大まかに配線をしてみました。

ちょっとだけ確認/SPDIF同軸の出力レベル 2019.9.29

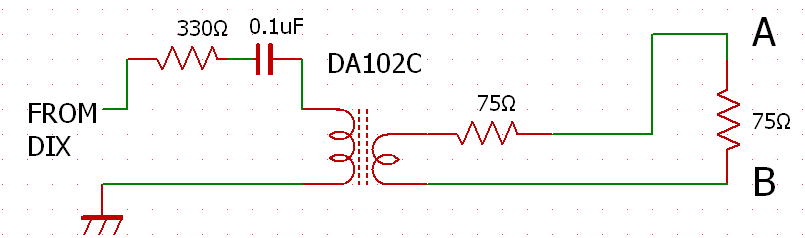

この基板はDIX9211あるいはPCM9211のMPIO(多目的IO)からSPDIF信号を取り出し、そのままパルストランスを駆動しようと思っています。

で、その駆動回路はDIT9211とほぼ同じ回路にして次のようなものです。IOポートの電流制限のために330Ωの抵抗を入れています。

この回路でどのくらいの出力がでるかを確認しておきましょう。

出力インピーダンスは75Ωで、終端抵抗も75Ωとします。

このような回路でどのくらいの出力電圧が得られるかを確認です。A-B間の電圧を観測します。

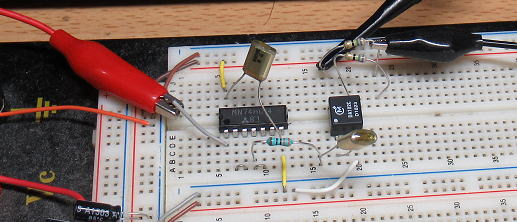

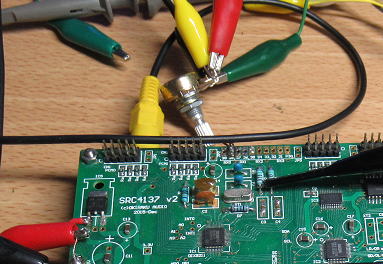

実験の様子です。

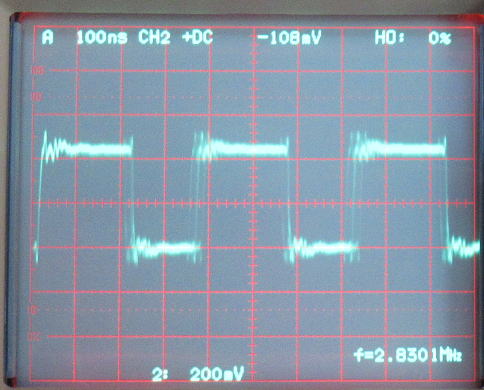

SPDIF信号レベルは規格では0.5V±0.1Vppのようです。いままで、あまり気にしたことはなかったです(笑。

ちなみに、DIX9211の入力レベルは最小で0.15Vppです。これは保証値であり0.15Vppなら大丈夫ですよ、ということですから

実際にももっと小さい値でも動くはずです(試したことありませんが・・・)。

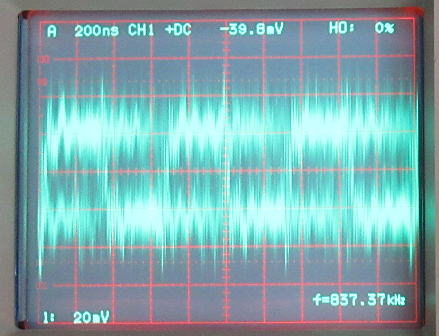

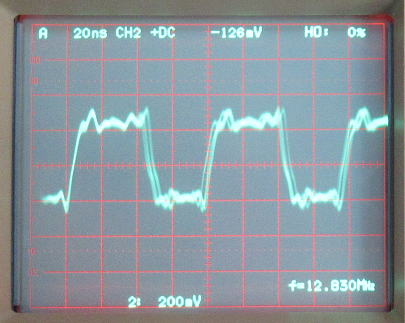

実験結果ですが、下のオシロの波形からみると、0.44Vpp程度の出力が得られるようです。ちょうど規格にはいっていますね。

ちょっとホットしました。

なお、SPDIF信号の周波数帯はFSの約64倍ですから44.1kHzだと2.82MHzになります。

約2.82MHzでの結果

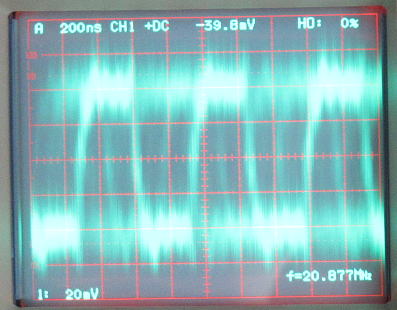

192kHzだと、約12.3MHzになりますが、その周波数でも大丈夫かみておきましょう。

下の写真の通り、約12.8MHzでも問題ないレベルですね。波形としても綺麗です。

約12.8MHzでの結果

DIX9211だとどこまでレベルまでロックするか?

後学のために、DIX9211の場合だと、どこまでレベルが下がっても信号をロックできるか

調べてみました。仕様では0.15Vppですが、それ以下の最低限を調べる目的です。

SRC4137を用いてDIX9211の入力最低レベルを調べます。

調査の結果は下限の閾値が50mVppくらいです。そのため80mVpp以上あれば安定してロックがかかります。

データシートの150mVppはやはり保証値ですね。

今回の基板の出力が440mVppとして、ケーブルの損失等があっても少なくても400mVppはでるでしょうから、

まったく問題のないレベルでしょう。