# DAC9018S 用逓倍クロック基板 製作マニュアル

#### <注意>

本キットをつかって生じた感電、火災等の一切のトラブルについては、当方は責任を負いませんのでご了承ください。また、基板、回路図、マニュアル等の著作権は放棄していませんので、その一部あるいは全体を 無断で第3者に対して使用することはできません。

#### 1. はじめに

本基板は DAC9018S にアドオンして使用する逓倍クロック基板です。DAC9018S で PCM あるいは DSD 入力したときに内蔵の 100MHz のクロックでは DPLL の設定が LOWEST ではロックしない場合があります。この基板は PCM あるいは DSD 入力時に DAC9018 のシステムクロックを内蔵のクロックから切り離し、LOWEST の設定でも安定してロックできるようにクロック供給する機能をもっています。クロックの生成は外部クロック (BCK) を逓倍することで得ており、ES9018 の最大周波数である 100MHz にもとも近くなるように逓倍の倍率をマイコンにて制御しています。

DAC9018S での性能を遺憾なく発揮させるアクセサリーとして面白いとおもいます。

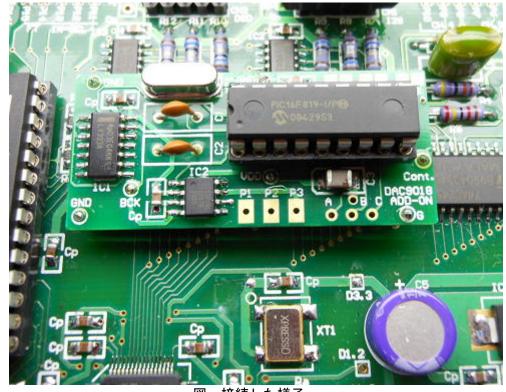

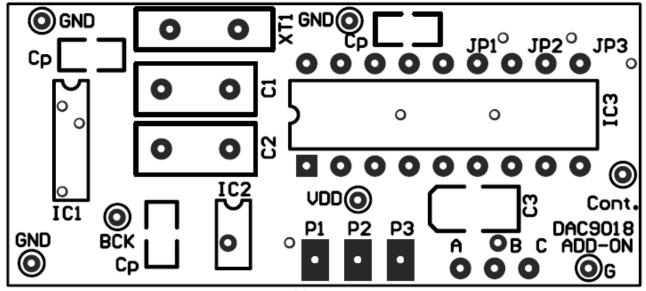

図 完成例

### 2. 仕様

表 主な仕様

| 機能       | DAC9018S 用のアドオンクロック基板                                                        |

|----------|------------------------------------------------------------------------------|

| 電源電圧     | 3.3V 単一(DAC9018S より供給)                                                       |

| 対応周波数    | FS 換算で 16 から 390kHz(ただし 192kHz を超える周波数では未確認)。                                |

| FS (kHz) | 16, 22. 05, 32, 44. 1, 48, 64, 88. 2, 96, 128, 176. 4, 192, 256kHz は 1%以内で判定 |

|          | して 最 適 逓 倍 率 を 設 定 。 そ れ 以 外 は 300-390kHz で は 逓 倍                            |

|          | 4(FSx64x4), 390kHz 以上では逓倍 2 (Fsx64x2)に設定。上記に当てはまらな                           |

|          | い周波数のときはDAC9018S内蔵の水晶発振器に切り替えます。                                             |

| 使用 IC    | ICS570 (クロック逓倍用 IC)                                                          |

| 基板       | 47mm×21mm、1.6mmt、70um 銅箔厚, FR4                                               |

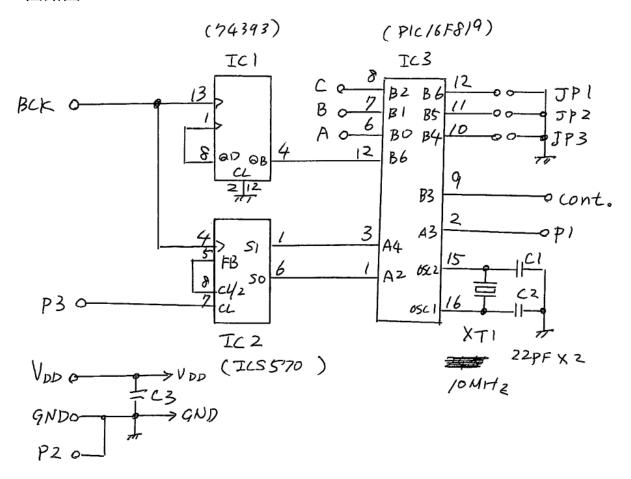

## 3. 回路図

図 回路図

### 4. 部品表

表. 部品リスト

| 部品    | No    | 規格          | 仕様        | 個 | 備考         |

|-------|-------|-------------|-----------|---|------------|

|       |       |             |           | 数 |            |

| コンデンサ | C1, 2 | セラミックコンデンサ  | 22pF      | 2 |            |

|       | C3    | チップセラミック    | 10uF      | 1 | 3216 サイズ   |

|       | Ср    | チップセラミック    | 0. 1uF    | 3 | 2012 サイズ   |

| 水晶    | XT1   | HC-49/S サイズ | 10.000MHz | 1 |            |

| IC    | IC1   | カウンタ        | 74LV393   | 1 | 74AC393 など |

|       | 102   | 逓倍用 IC      | 1CS570    | 1 |            |

|       | 103   | マイコン        | PIC16F819 | 1 | プログラム済み    |

### 5. ジャンパー

本基板には JP1~JP3 があります。JP1 のみ使用します。

表 JP機能

|     | 開放           | 接続                |  |

|-----|--------------|-------------------|--|

| JP1 | 基板の機能をアクティブ  | 基板の機能を停止し、常に      |  |

|     | にします(通常はこの設定 | DAC9018S の内蔵クロックを |  |

|     | とします)        | 使用します。            |  |

| JP2 | RESERVED     |                   |  |

| JP3 | RESERVED     |                   |  |

### 6. 基板端子

本基板には P1~P3 があり、DAC9018S の内蔵水晶発振器(XT1)を制御するために用います。DAC9018S との接続については 7. を参照ください。

表 基板端子

|    | 機能および接続先                               |  |

|----|----------------------------------------|--|

| P1 | 水晶発振器の動作制御端子。DAC9018SのXT1のPIN1に接続します。  |  |

| P2 | GND。通常は未接続でもかまいません。                    |  |

| P3 | クロック出力端子。DAC9018S の XT1 の PIN4 に接続します。 |  |

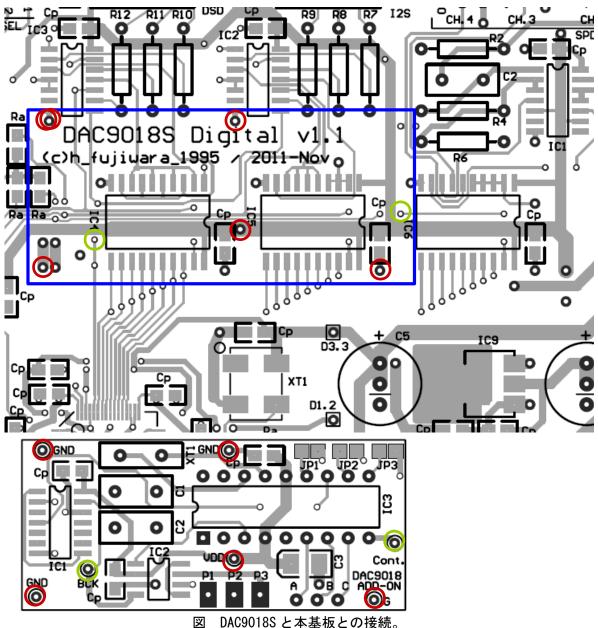

### 7. DAC9018S と本基板との接続

下図を参照して接続ください。図中の丸印の部分を互いに接続します。緑丸については DAC9018S 側 のランド径が小さいため、細い線で接続します。その他は抵抗のリード線の余り等で接続すればよいで しょう。

図 接続した様子。

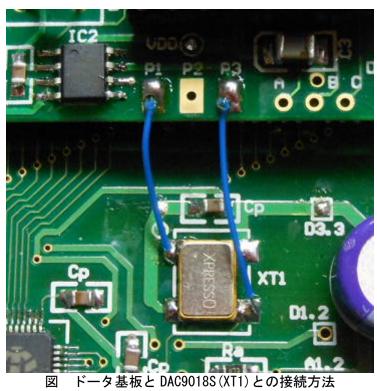

基板間の接続が終われば本基板の P1,3 と DAC9018 の XT1 を接続します。下図を参考にしてください。

### 8. 基板パターン

(a) シルク

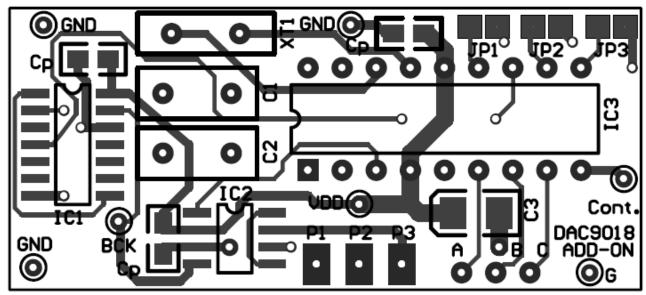

(b) 配線パターン(部品面)

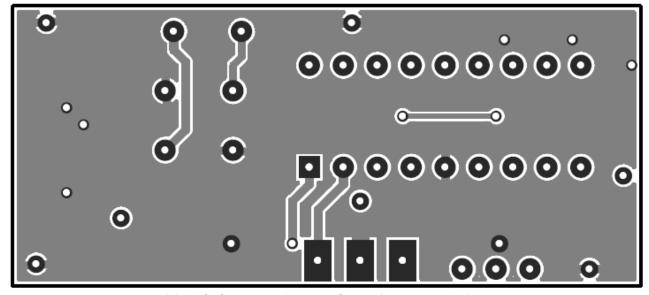

(c) 配線パターン(半田面:部品面側からみた場合)

9. 更新記録 2012.3.3 R1 初版