ジッタクリーナーの切り替え器を考える!の巻き。 2013.1.7

やはり要るかな〜?

ジッタクリーナはDACなどのディジタルオーディオにおけるクロックの揺らぎを抑制するもので、

その効果はご承知の通りでしょう。活用している素子はシリコンンラボ社のSI5317を用いて

いますが、設定にも依存しますが異なる周波数のクロック信号が入力されてから、

出力信号(クロック)が安定するまでに、かなりの時間がかかります。そのため、

周波数を変更した場合はDACから盛大なノイズが出てしまいます。たとえばPCを音源にしていて

48→44.1kHzにサンプル周波数を変えた場合などです。また、ASRC等でアップサンプリング

あるいはダウンサンプリングした場合も同様です。

そこで、この周波数変更時のノイズを抑制するために、ジッタクリーナの出力信号が

過渡応答にあるときは、入力信号をバイパスして出力することが考えられます。

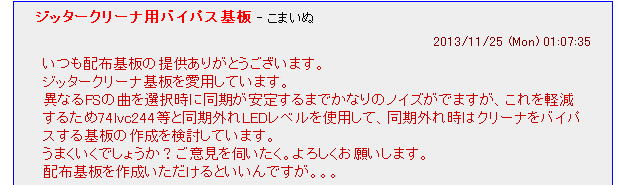

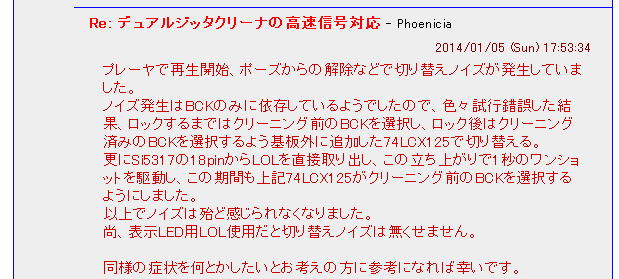

すでに、実行されておられる方もいますが、かなり必須に近いものではないかと思ってしまいます。

たとえば、このような書き込みもあります。

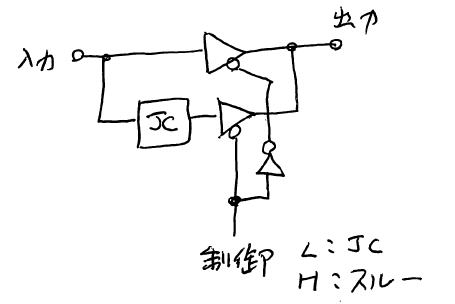

切り替えは簡単?

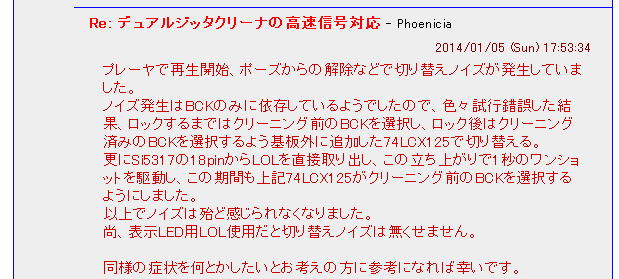

切り替え自身は簡単で、下図のようにバッファーを2個並べて切り替えるだけでよいでしょう。

問題はどうやって切り替えに必要な制御信号を作るかです。

結構難しい?

過渡応答のノイズを極力抑えるためにはSI5317のLOL(LOSS OF LOCK)信号を直接引き出して

それで信号を切り替える方法が提案されています。しかし、これってかなり半田付けの技術が必要になりそうです。

入力信号だけでロックが外れたことがわかるロジックが出来れば、単純なアドオン機能として

つかえそうなので、考えてみまししょう。

回路のポイントは?

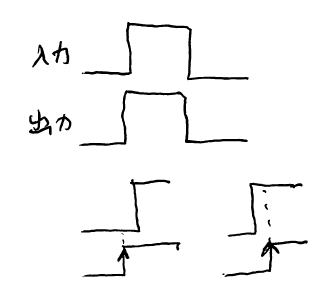

回路のポイントは入力信号と出力信号の位相差がずれた(ずれているそのものの状態ではなくて、

ずれ出したこと)を検知するロジックをどのように組むかです。

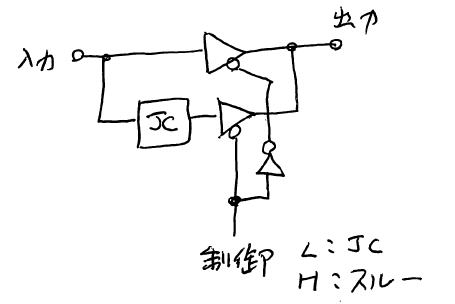

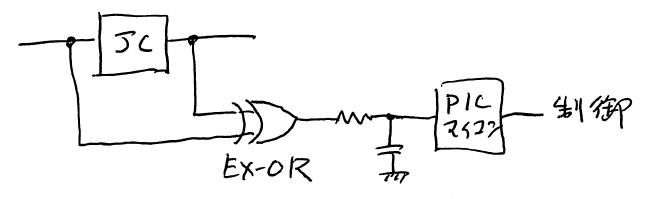

ソフトロジックが利用できるなら、EX-ORをつかって、そのLPF出力のアナログ値の変化を

監視すれば簡単ですが、LPFの時定数やソフトの処理時間で、信号の切り替えに数m〜数10mS程度の

時間がかかる可能性があり、この間のノイズを抑えることができません。専用のソフトを組めば

なんとか1mS以下に抑えれれると思いますが、やはりハード的になんとかすべきかな〜という

気がします。

ソフトロジックで実現するなら簡単ですが、時間遅れが気になるところです。

簡単にできる?

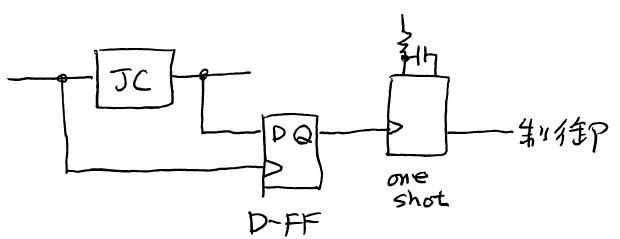

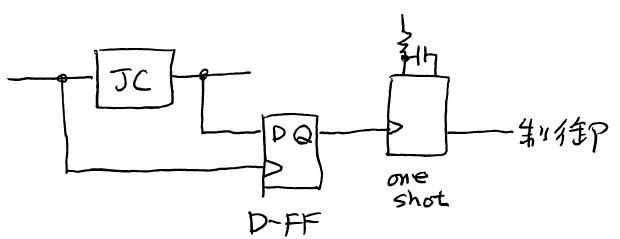

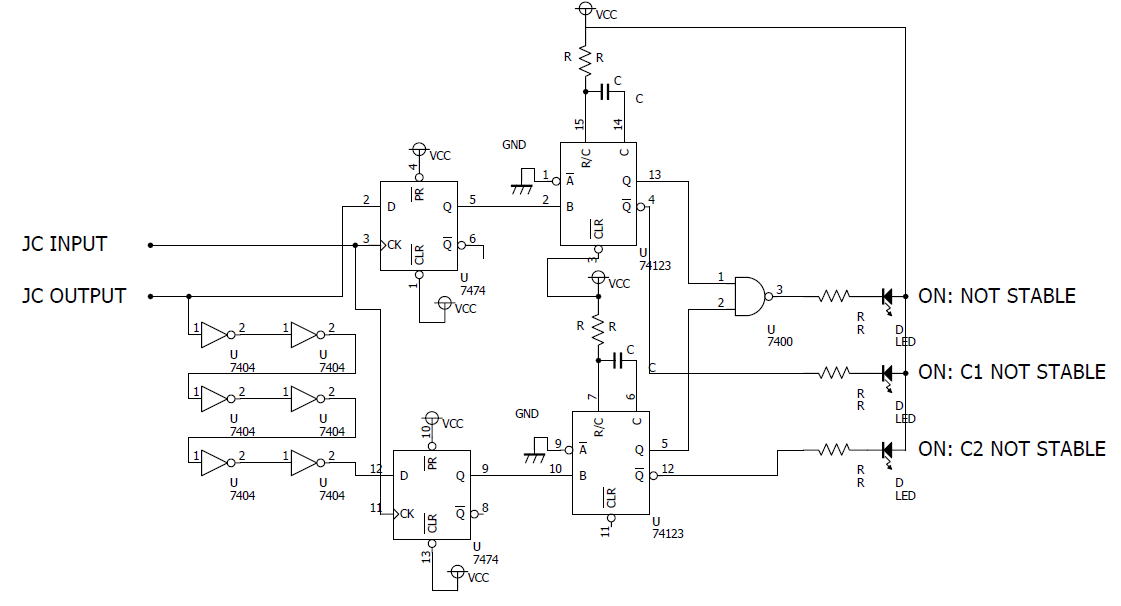

簡単に思いつくのが、このようなものでD-FF(7474等)で位相差を抽出して、その出力を

ワンショット(74123等)に入れれば、位相差がずれ出したことを検知することができます。

ただし、このままだと入出力の位相差がほぼ同じの場合だと、誤作動してしまいます。

なぜかといえば、図のように同位相の信号は入るとD-FFの出力はLとHで不安定になるからです。

この現象も含めて位相のずれを検知することが必要です。

こんな回路でいいはずだけど・・・入力と出力の位相が同じだと、誤動作します。

同位相といってもD-FFはディジタル的にはL,HのどちらにLATCHされるかわからない。

こんな回路?

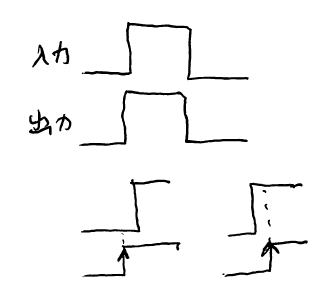

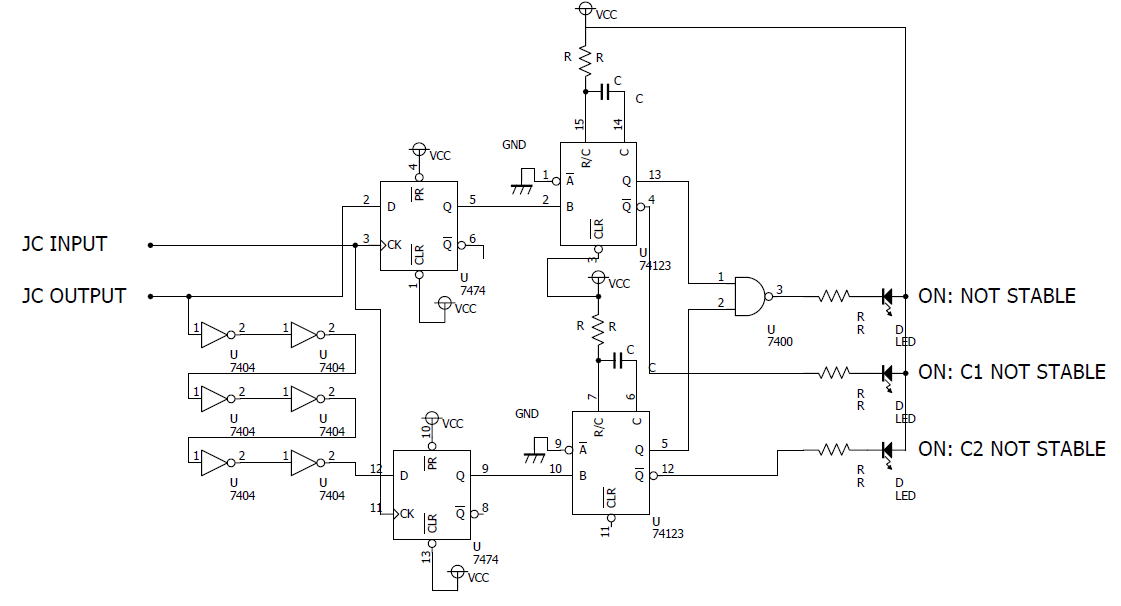

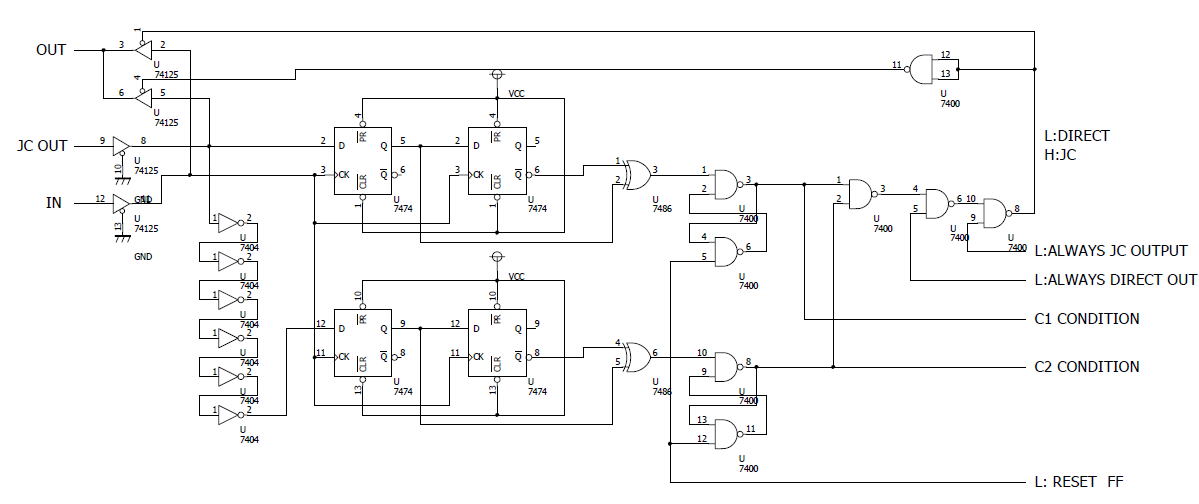

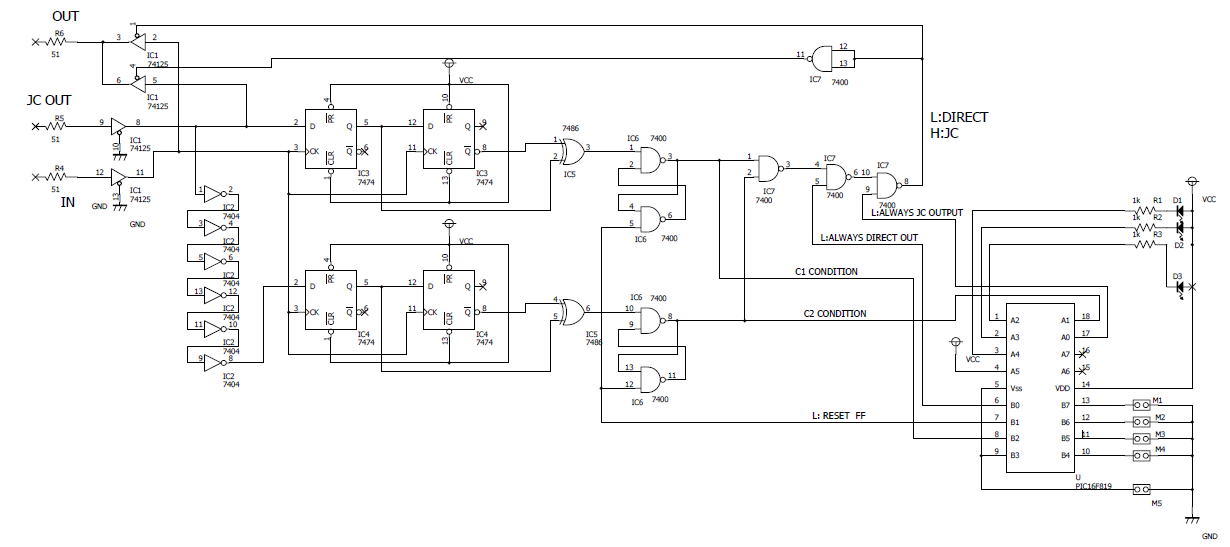

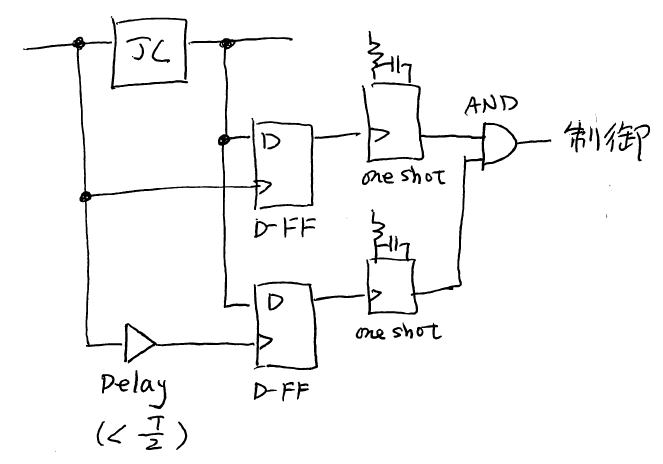

そこで考えたのが、下のような回路です。

こんな形でいいかな?

2個のD-FFを用意して、入力でするデータを片側だけ数10nSずらしていれてやります。

そうすれば、すくなくともどちらのD-FFの出力は位相変化がなければHあるいはLに安定

して落ち着きます。したがって、2個のD-FFの出力をそれぞれワンショットに入力したのちに、

両方の出力がHになった状態であれば位相差に変化があると判断できます。

検出速度は入出力の周波数差に依存し、例えば48kHzと44.1kHzであれば約4kHz(250uS)で切り替えが可能です。

これなら十分に高速でしょう。ただし、ジッタクリーナの出力が安定するにはどうしても時間が

かかるので、そのための位相差が安定してからジッタクリーナの出力に切り替えるために

やや時間遅れを設ける必要があります。この機能は別途設ける必要があるでしょう。

デレイは?

これはロジック素子を直列に並べてやれば勝手に信号は遅延してくれます。

でも、あまり遅らせてもいけません。ジッタクリーナの適用周波数が100MHz(周期T=10nS)ですから、T/2未満に

押さえる必要があります。ですから2〜5nSで十分です。74LVC04の遅延速度をみてみると、3.3V動作時に

min 1ns, Typ 2.5ns, max4.3nSです。ちょっと微妙だなあ?

BCKに適用することを考えると最高速度はおよそfs=384kHzで24.576MHzだから

T=40nsだから20nSとみて、2段、4段、6段の組み合わせでいいかな?

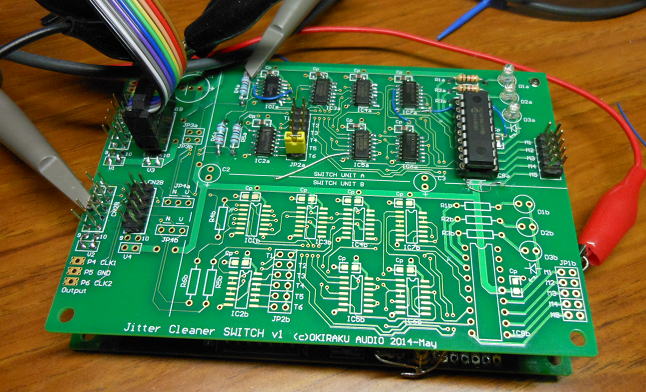

思い出したように作業再開! 2014.4.27

DAC1241-2などの作成で、この企画を忘れていましたが思い出したように再開です(笑)。

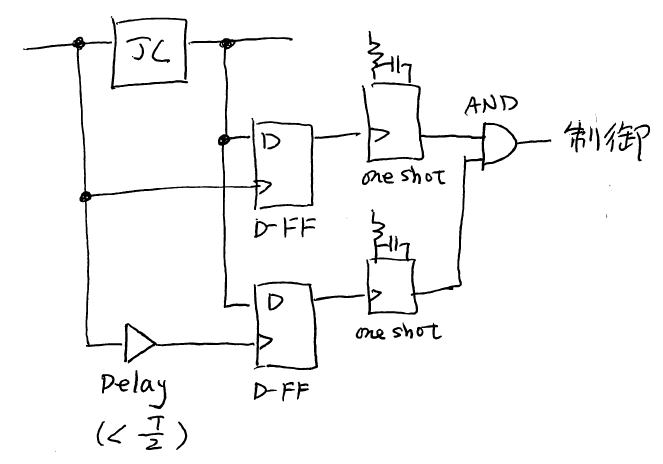

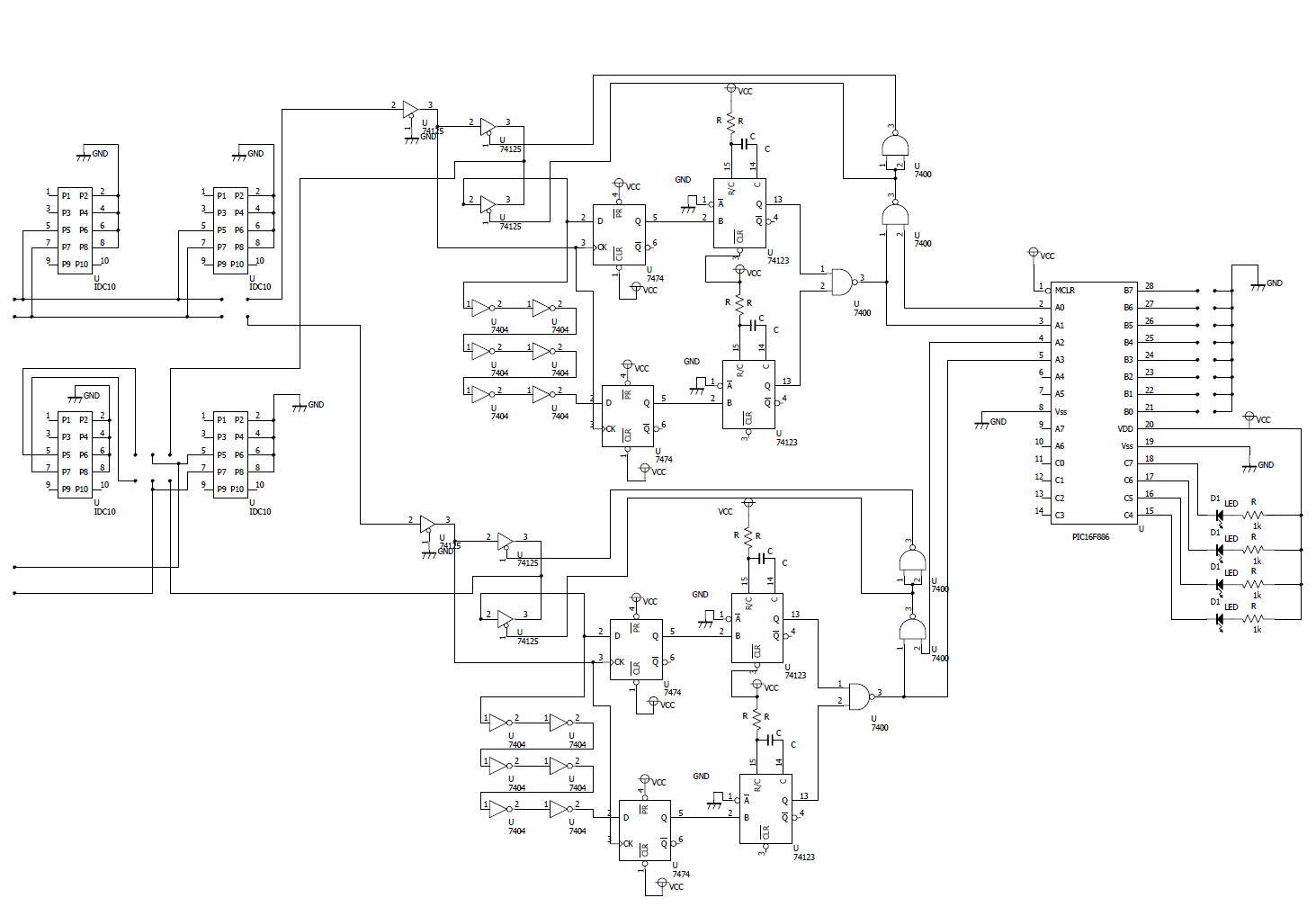

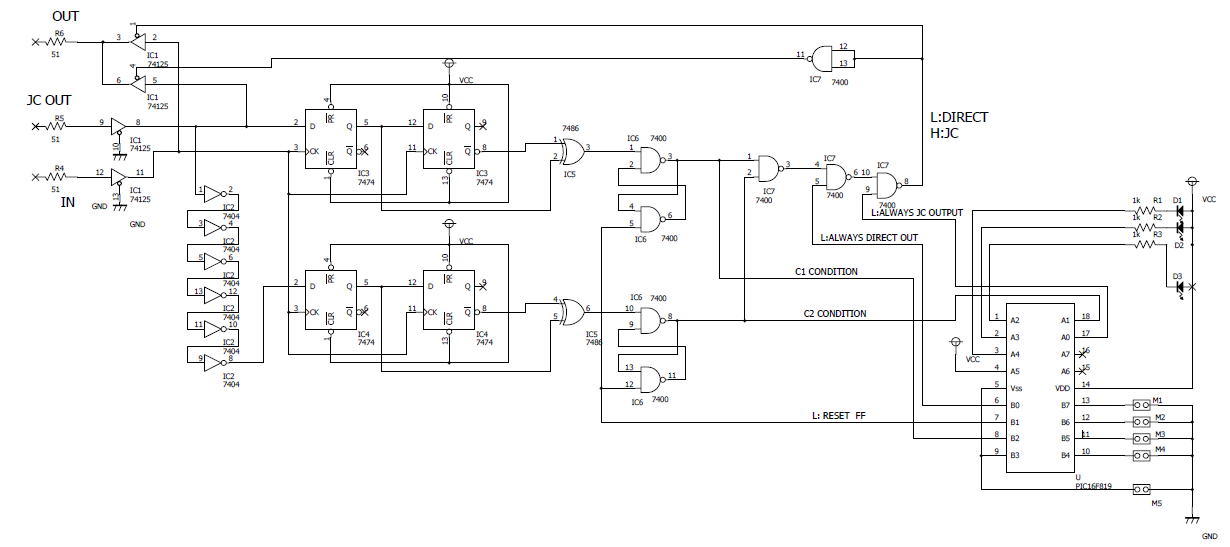

まず、回路図をきちんと描いてみましょう。ワンショットの定数はこれからです。

こんな感じですね。

回路は2回路あります。これはDUALジッタクリーナへの対応を考えたものです。

でも、まずはこの回路が問題なく動作するか、実際に組んで確認してみましょう!

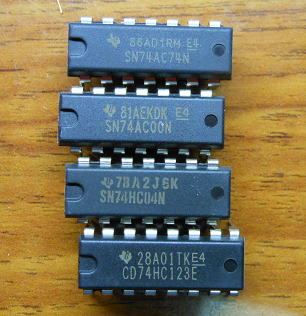

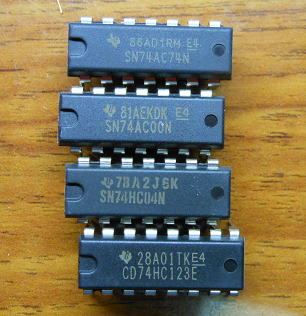

まずは部品探し!

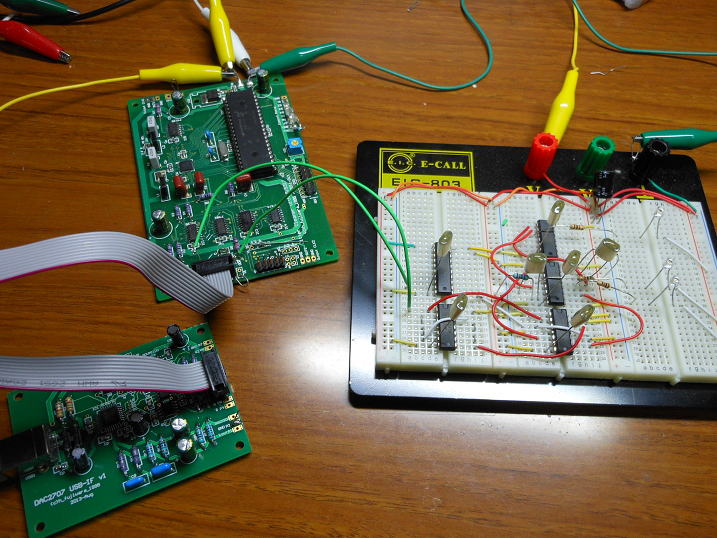

試作するにはブレッドボードを使いますが、そのためにはDIPタイプのICを準備必要です。

部品を探してみましょう。

必要なICは74HC123,74AC74、74HC04、74AC125です。

74AC125はあったかな〜。

部品箱の大捜索です。

やっぱりないか〜

74AC125は予想通り部品箱にはありませんでした。なんせ、買った記憶がないですからね(笑)。

まあ、機能を確認するのに必要なICはそろったのでこれらを使いましょう。

部品箱から探し出したIC類です。

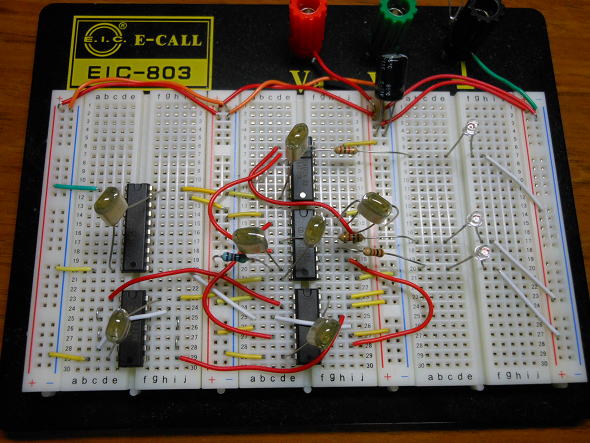

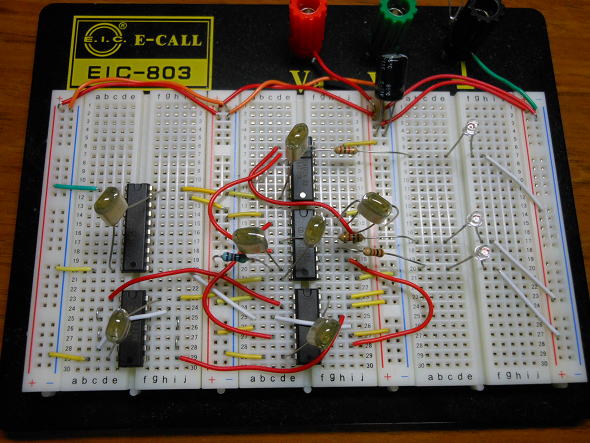

ブレッドボードで組み立てましょう!

ICの数も少ないので、小さいブレッドボードで組み立てましょう。

機能の確認のためのLEDも取り付けいます。

こんな感じで組みあがりました。

確認している部分の回路図はこんな感じです。

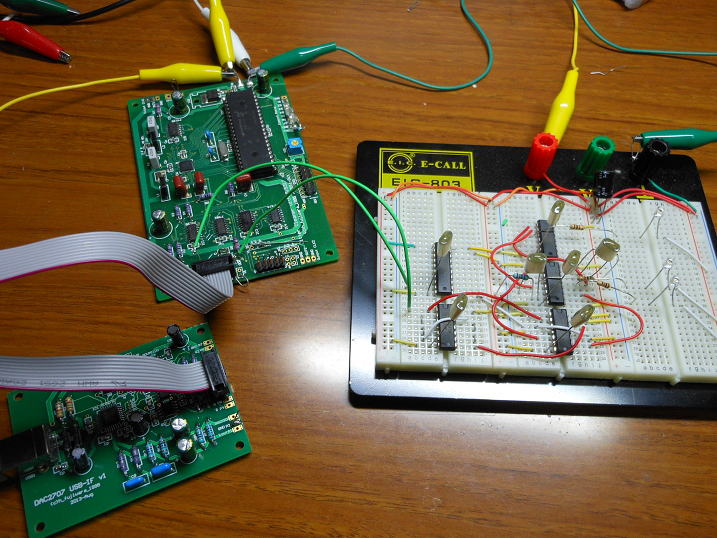

動作確認です

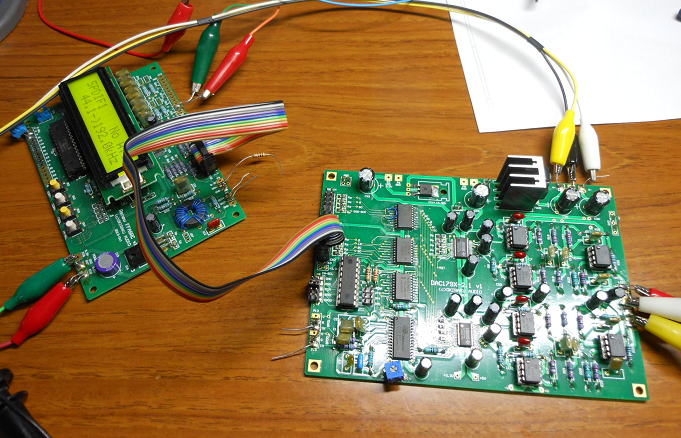

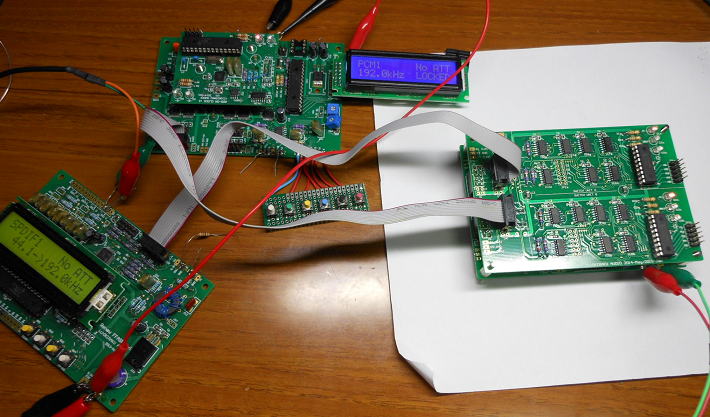

クロックのソースはDAC2707を使いました。それをジッタクリーナに接続して、ジッタクリーナの入出力信号を

試作回路に入れています。

確認のポイントは周波数や位相が切り替わったときに、試作回路の出力が即座にONになるかどうかです。

動作確認の様子です。

74HC04の遅延時間は 2014.4.28

74HC04のインバータを6個並べてると、どのくらいの時間が遅れるかみてみました。

オシロメモリの読み取り精度があまりないけと、0.2目盛りくらいかな?

ということはだいたい50nsなので、1段あたり8nSくらいになります。

ほぼカタログの標準値と同じです。

74HC04の6段接続後の波形の遅れ。

わ!GWだ〜

ひさしぶりにのんびり帰省しました。

体も頭もぼにょぼにょ(笑)。さて、平常生活に向けてリハビリしましょう〜

作業再開 2014.5.6

帰省中に考えていましたが、ワンショットをつかうと定数調整とかが面倒そうなので、

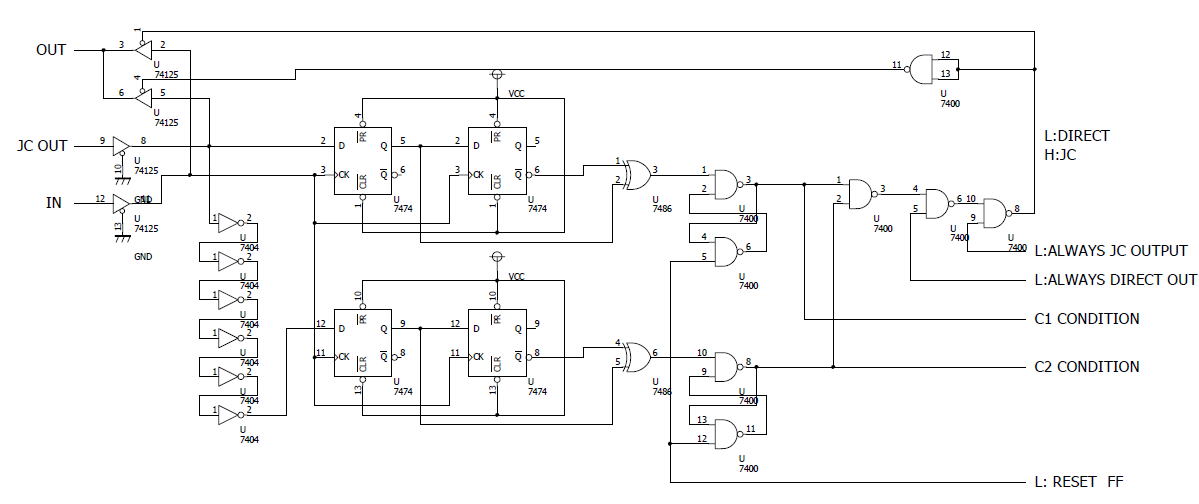

すこし回路構成を考えなおしました。

すこし回路を変更です。ワンショットの代わりにFF(フリップフロップ)をいれました。

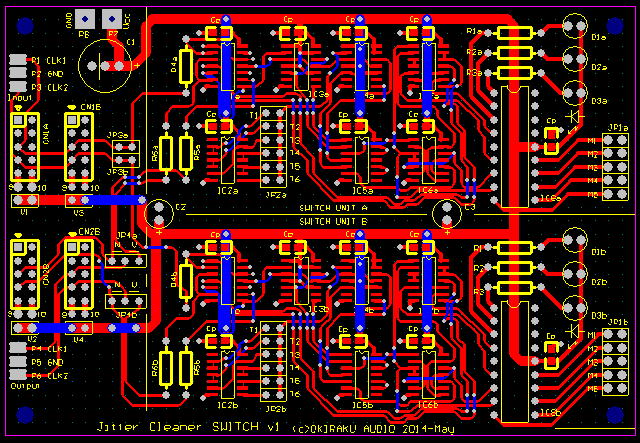

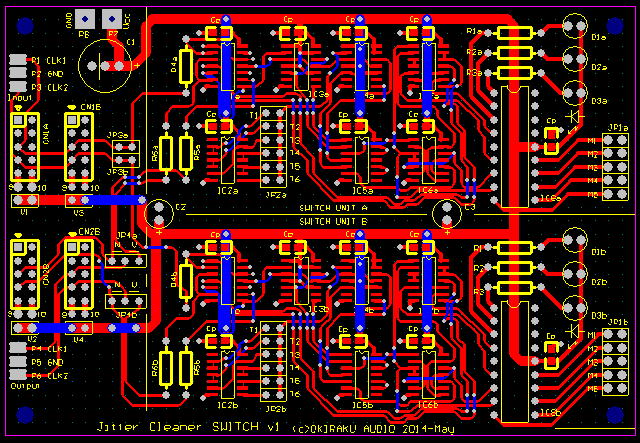

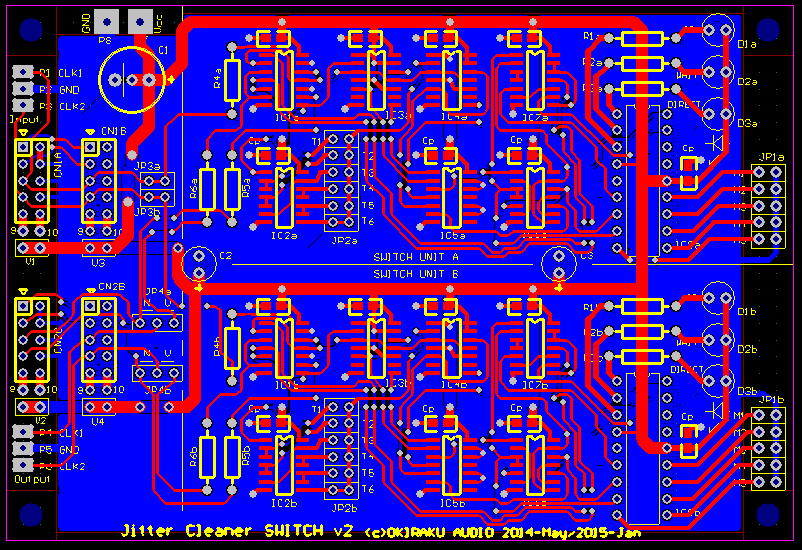

たぶん動作的には大丈夫なのでパターンを書いてみました。

ほんとに大丈夫かな?という不安はあれども・・・・。

まずは描いてみました。

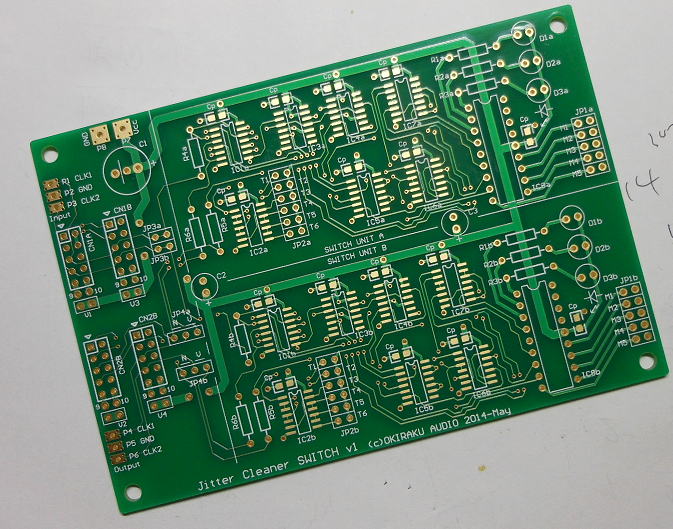

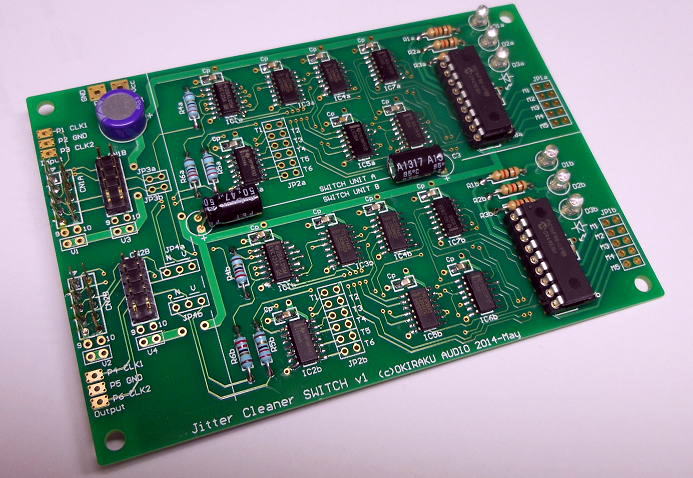

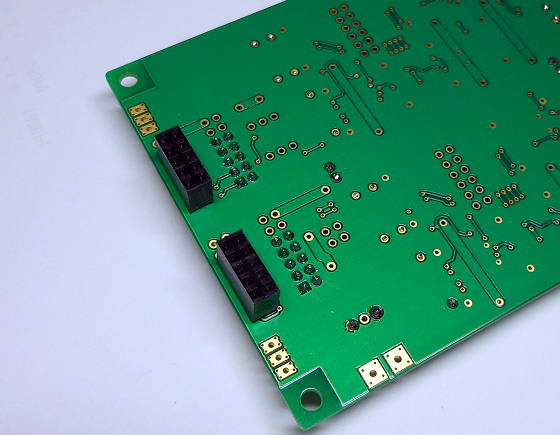

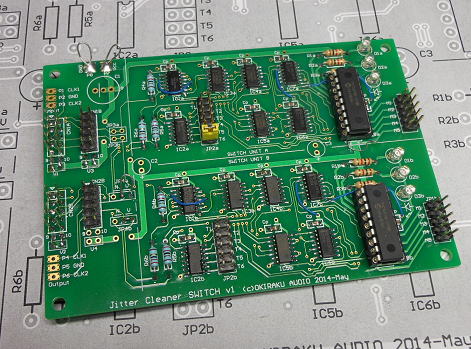

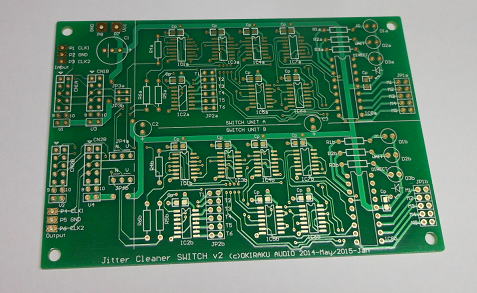

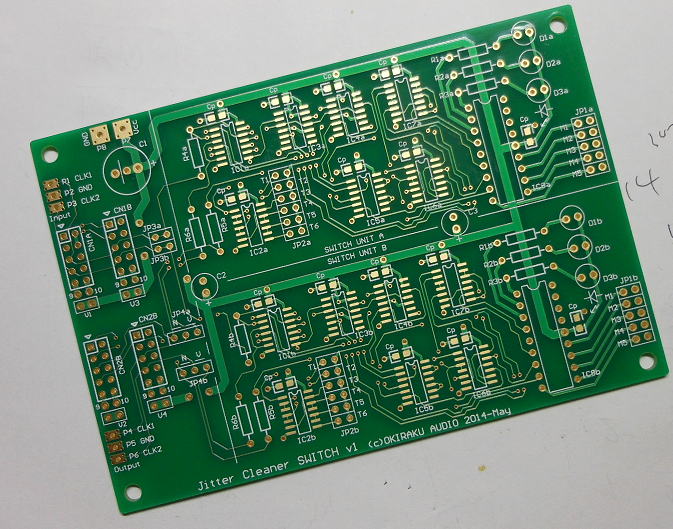

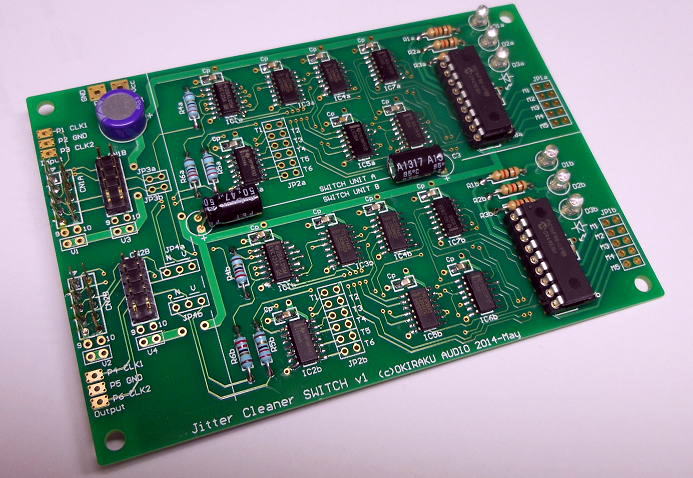

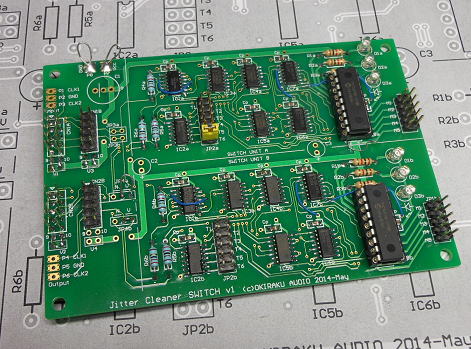

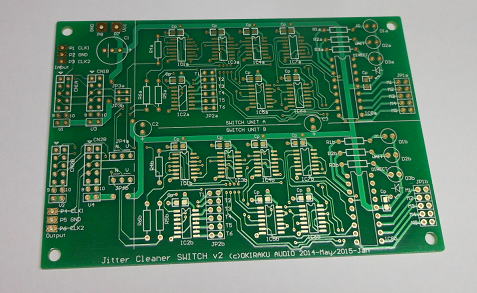

基板ができました。組み立てよう! 2014.6.3

基板が納品されました。

部品は少ないので短時間で完成です。PICはお飾りです。

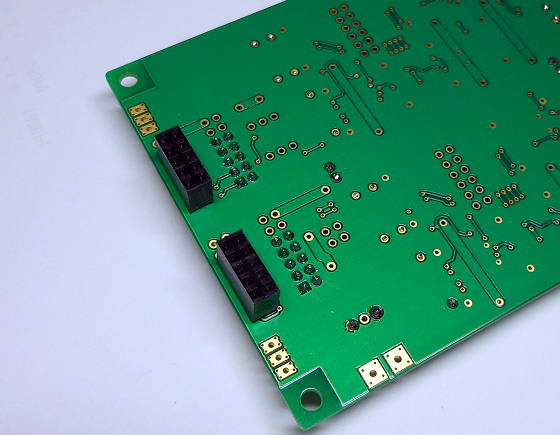

裏面のコネクタです。これとジッタクリーナを接続します。

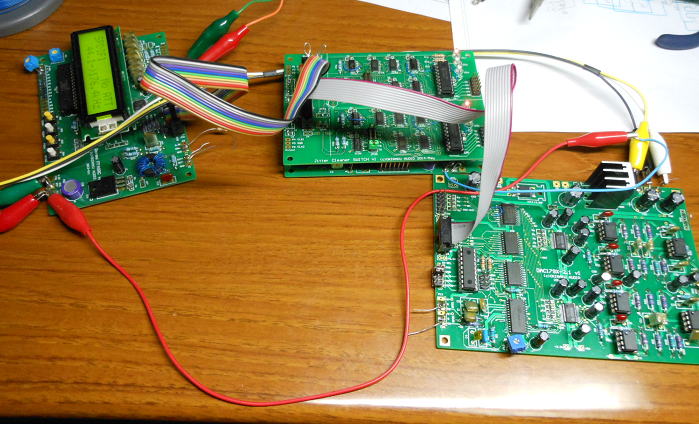

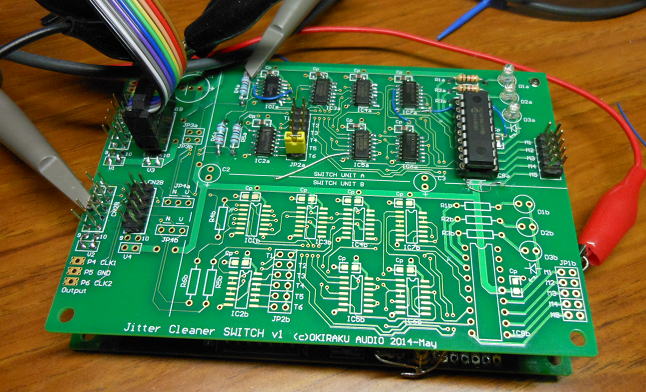

ジッタクリーナと接続した様子です。下側がジッタクリーナ基板、上が切り替え器です。

久しぶりの作業再開 2014.6.21

備忘録から

| A0 |

OUT:ALWAYS JC OUTPUT(AJC) ACTIVE LOW |

| A1 |

INT: C2 CONDITION(未接続) |

| A2 |

LED3 |

| A3 |

LED2 |

| A4 |

LED1 |

| A5 |

Vcc |

| A6 |

N.C |

| A7 |

N.C |

| B0 |

OUT:ALWAYS DIRECT OUT(ADO) ACTIVE LOW |

| B1 |

OUT:FF RST |

| B2 |

IN:C1 CONDITION |

| B3 |

M5 モード設定 |

| B3 |

M4 モード設定 |

| B5 |

M3 モード設定 |

| B6 |

M2 モード設定 |

| B7 |

M1 モード設定 |

OUT

ALWAYS

JC OUTPUT

AJC |

OUT

ALWAYS

DIRECT

OUTPUT

ADO |

IN

C1

COND |

IN

C2

COND |

OUT

FF

RST |

状態 |

出力

クロック |

|

| L |

X |

X |

X |

X |

|

JC OUT |

|

| H |

L |

X |

X |

X |

|

IN

(DIRECT) |

|

| H |

H |

H |

H |

H |

C1,C2に位相変化が発生した場合 |

IN

(DIRECT) |

|

| H |

H |

L |

H |

H |

C1、C2の少なくともどちから1つが

安定 |

JC OUT |

|

| H |

H |

H |

L |

H |

|

JC OUT |

|

| H |

H |

L |

L |

H |

|

JC OUT |

|

ほんと久しぶりです。 2015.1.4

前回作業をしてから半年ぶりの作業再開です。

なぜ、前回は基板まで作成して途中で中断してしまったかといえば、

電源を入れたときに電源の電流計がいきなり1Aくらいまで振れてしまって、慌てて切ったところはいいのですが、

そのときは原因がよくわからなかったので、とりあえずあとで、と思ったらずるずるいってしまいました。

で、正月休みに色々と考えてもう一度パターンの確認からしてみまようと頭の切り替えができたので、

再開する運びとなりました。

しかし、半年も経つとほとんど忘れてますね・・・・。もう年だしな〜(笑)。

あれ?

いぜん作った基板を探し回りましたが見つかりません。ひょっとして年末の大掃除のときにジャンクと間違えて捨てたかな?

そういえば、年末はいろいろと処分したからな〜。自分で捨ててなくても、捨てられそうな位置においておいたら、家族に捨てられたかもしれません。

まあ、文句を言おうもののなら、「そんなとこにおいといたあんたが悪い」で一蹴されそうですが(笑)。

ということで、もう1枚!

部品点数も多くはないので、もう1枚作成です。今回は1回路分のみです。ジッタクリーナのちょうどBCKの回路に相当する部分です。

事前に回路図とパターンを眺めて3箇所ほど修正です。かなりポカミスありました。

1回路分を新たに作りました。

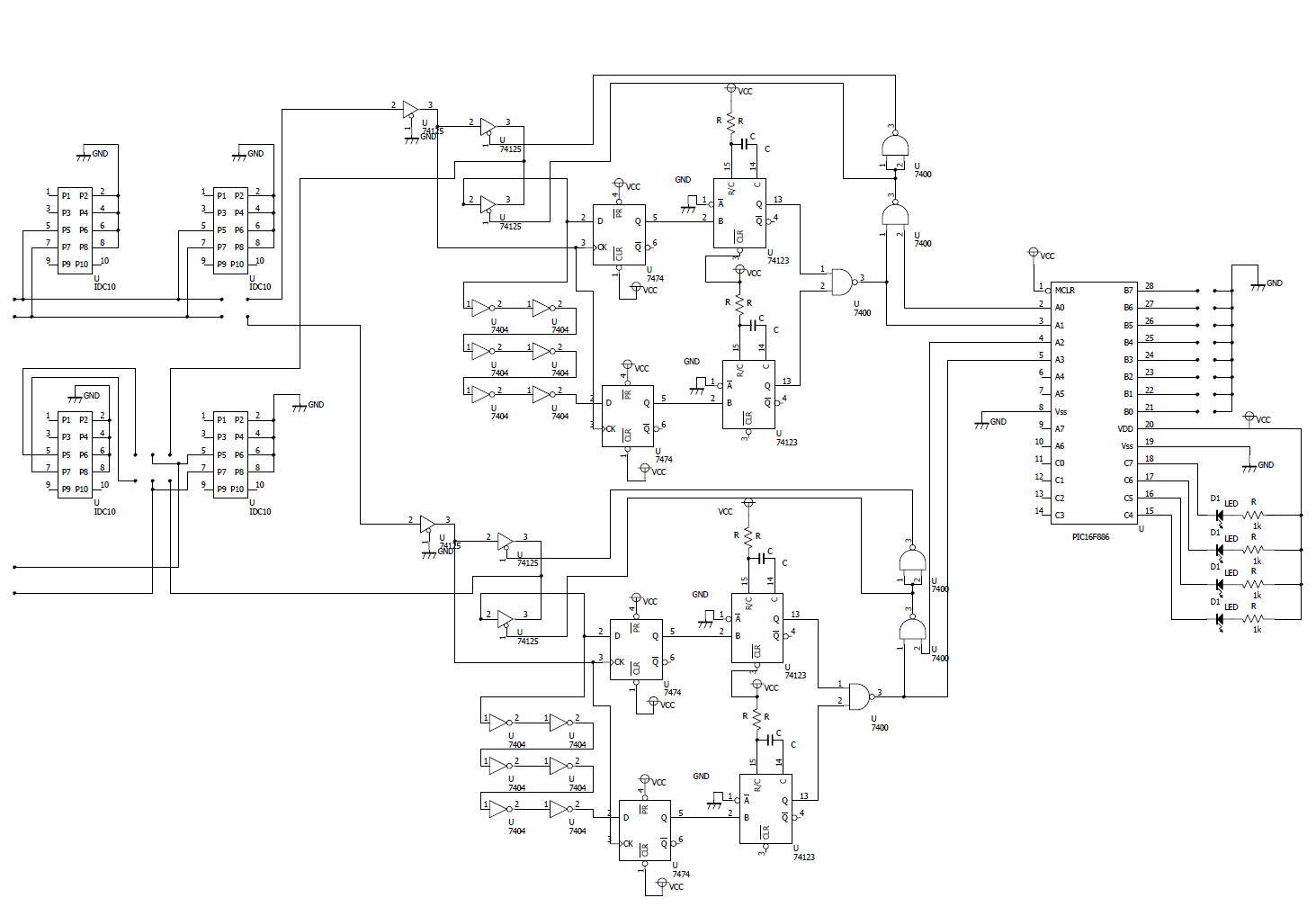

主要な回路はこんな感じです。

ソフトを作っていきましょう!

ソフトを作るまえに、ジャンパー設定を定義づけておきましょう。半分備忘録です。

| 動作モードの設定 |

| M1 |

M2 |

モード |

説明 |

| OPEN |

OPEN |

NORMAL(1) |

ジッタクリーナ出力が安定した場合はJC出力。

それ以外はダイレクト(スルー)出力。 |

| SHORT |

OPEN |

JC OUT(2) |

常にジッタクリーナを出力。 |

| OPEN |

SHORT |

THROUGH(3) |

常にスルー出力。 |

| SHORT |

SHORT |

reserve(4) |

予約 |

| JC安定後の保持時間 |

| M3 |

M4 |

時間 |

説明 |

| OPEN |

OPEN |

10sec |

ジッタクリーナの出力が見かけ上安定してから、実際にジッタクリーナの出力を得るまでのディレイ時間を設定します。 |

| SHORT |

OPEN |

6sec |

| OPEN |

SHORT |

3sec |

| SHORT |

SHORT |

1sec |

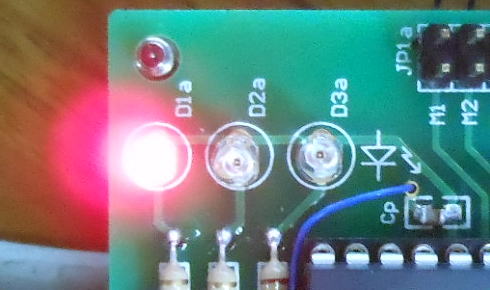

| LEDによる状態表示 |

| D1 |

ジッタククリーナを出力しているときに点灯 |

| D2 |

ジッタクリーナが安定しているが安定後の保持時間中は点灯

ジッタクリーナの安定待ちのときは点滅

|

| D3 |

ダイレクト出力時に点灯 |

動作確認!

オシロで波形を眺めている分には問題なさそうです。

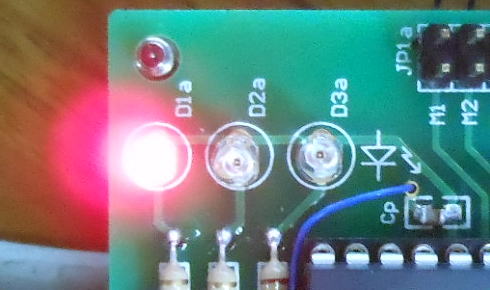

この基板には動作状態を示すために3つのLEDが付いています。

下記のようなシーケンスで進みます。

周波数切り替え

↓

LED3が点灯:ジッタクリーナをスルーした信号を送出。

↓

LED2が点滅:ジッタクリーナの動作安定状態待ち(位相ずれなどがある場合)

↓

LED2が点灯:ジッタクリーナの出力は安定しているが、さらにウエイトをかける(1〜10秒)

↓

LED1が点灯(LED2,3は消灯):ジッタクリーナ出力に切り替え

なお、ジッタクリーナ出力からの切り替えは、すこしでも遅れるとノイズがでるのでマイコンを介さずに

ハードで直接切り替わるようにしています。具体的には入力信号とジッタクリーナの出力信号の位相が

ずれたことを検知して即座に、ジッタクリーナの出力をスルーするようにしています。

ジッタクリーナ出力に切り替わった状態。

試用してみましょう!

どのくらいの効果があるのかを試すために、DACにつないで試してみましょう。

ちょうど、製作中のDAC9018K2Mの試聴にあわせて使ってみることにしました。

→ こちらになります。

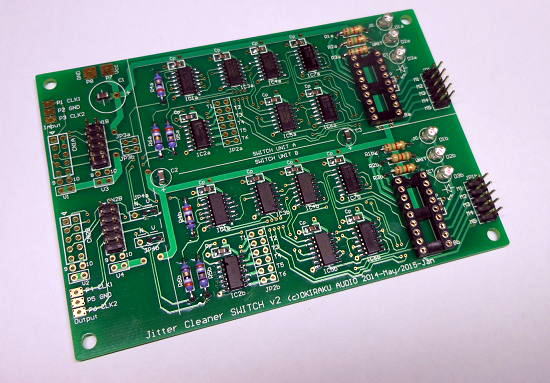

次はDUAL JITTER CLEANERと組み合わせ! 2015.1.6

DUAL JITTER CLEANER ではPCM信号のBCK、SCLKの2つのクロックの整形ができるので

切り替え基板のもう一つの回路も組み立てます。

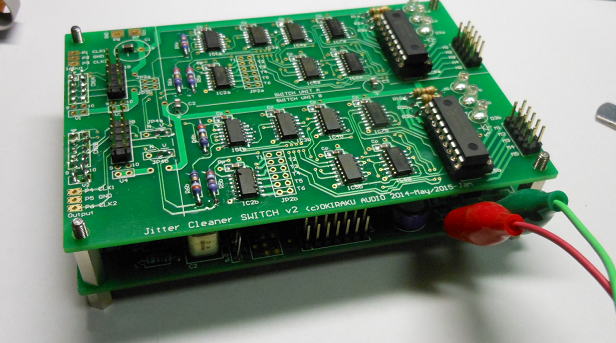

2回路分を組み立てたジッタクリーナの切り替え器

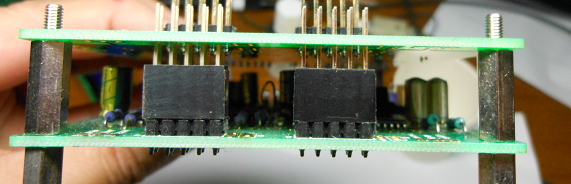

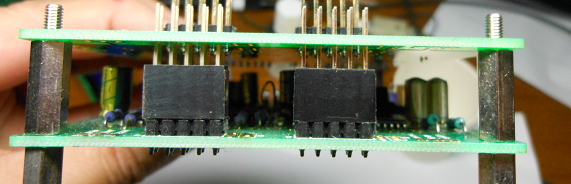

ジッタクリーナとの合体前ですが、ジッタクリーナ(下)側のオスピンと切り替え器(上)のメスソケット

の位置がピッタリあっている様子がわかります・・ん?わかりにく。

合体する前の2枚の基板

試聴してみましょう!

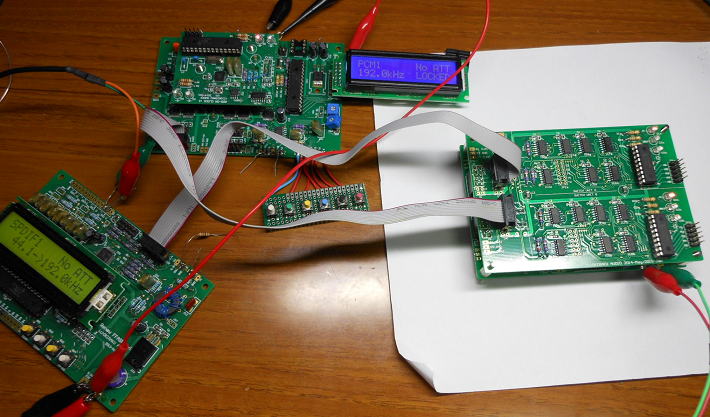

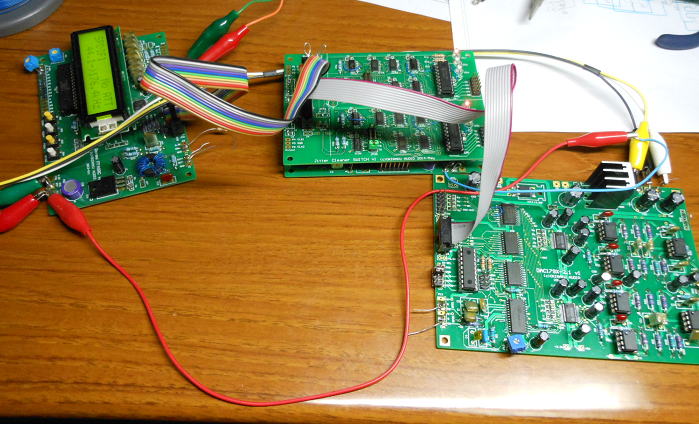

構成は

RenewFFASRC(PCM出力)→ジッタクリーナ切り替え器/DUAL JITTER CLEANER

→ DAC1794-2.1→直接ヘッドホン

です。これで、動作確認とノイズの確認を行いました。

動作確認の様子です。

まずは問題なく音がでることを確認しました。FFASRCの周波数を変更したときには、若干ポップノイズが生じます。

それ以外はノイズはないようです。念のため、ジッタクリーナを外して直接FFASRCとDACを接続してノイズの発生

状況を確認しましたが、この場合も周波数を切り替えたときには若干ポップノイズが生じますが、ジッタクリーナ(切り替え器付き)

とほとんど同じようです。このポップノイズは不可避ということでしょう。

動作確認の様子です。ジッタクリーナを外しました。ノイズは一緒ですね。

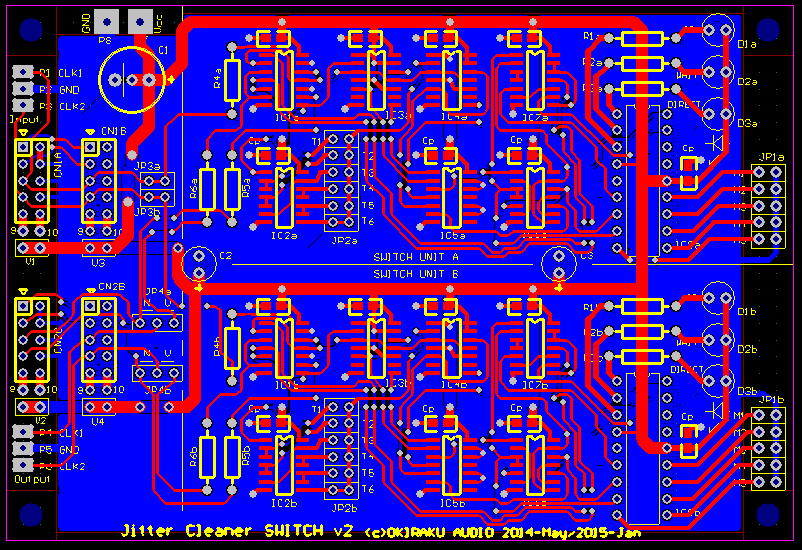

修正版をつくるかな?

今回のジッタクリーナでは修正箇所が1回路あたり4箇所(計8箇所)あるので、修正版を書いてみましょう。

修正版を描いてみました。

動作モードの備忘録 2015.1.18

この基板の目的は、ジッタクリーナの周波数が切り替わり時間(数秒)に発生するDACからの

ノイズを抑制することです。機能的にはジッタクリーナの出力周波数が安定するまでは、

DAI等から供給されるクロックを直接DACに送り出し、ジッタクリーナの出力が安定した時点で、

切り替えます。

通常の接続方法

ジッタクリーナスイッチを追加した構成

ジッタクリーナスイッチで、周波数の安定を検出するには位相のずれをみています。

出力が安定している位相のずれがありませんが、周波数は変わるときにはこの位相がずれてきます。

この位相のズレを検知して瞬時に切り替えるます。

周波数ずれの検知方法(位相のずれをみています)

動作フローは次のようになります。

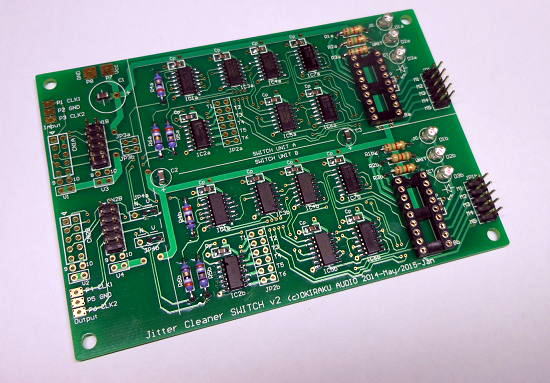

V2基板できました。 2015.1.20

一箇所シルクミスを見逃してしまいましたが、パターンの修正はできているはずです。

V2基板完成です。

一気に組み立てましょう!

部品はさほど多くないのと、表面実装部品がほとんどなので組み立ての時間はさほどかかりません。

ほとんど部品のとりつけ完了です。

ジッタクリーナとのとりつけは、基板の部品面にコネクタをとりつけますが、スペーサの長さ(15mm)に応じて

取り付ける必要があるのでリード線の長いコネクタを使用しました。スペーサの長さであわせるなら11mmがピッタシ

ですが、店頭では手にいれるのは難しいかもしれません。ヒロスギ計器から直接購入すれば問題ありませんが、

50本以上が最小注文数量になるので、すこし躊躇してしまいます。

ジッタクリーナとの取り付けのためリードの長いコネクタを使用。

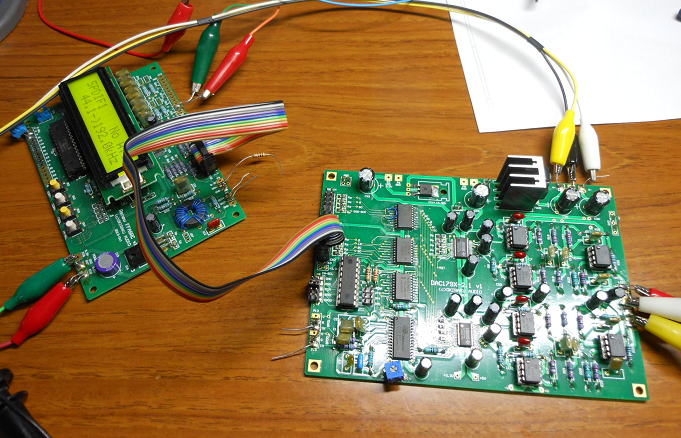

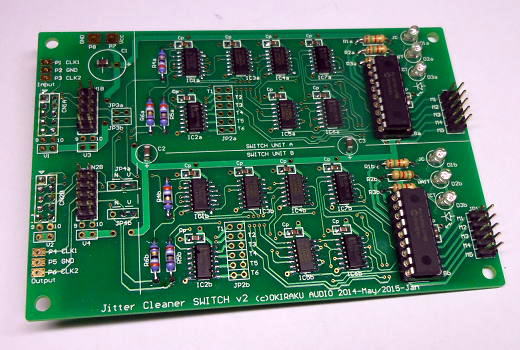

上がジッタクリーナスイッチ、下がDUAL JITTER CLEANERです。

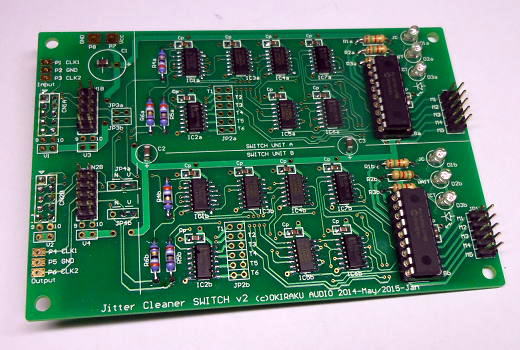

完成しました!

電解コンデンサに相当する部分は10uFの大容量セラミックコンデンサを取り付けました。

完成です。

ジッタクリーナとくみあせた状態です。

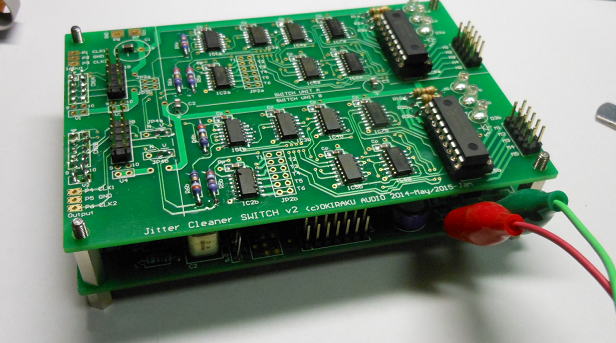

最終動作確認!

念のため動作確認です。FFASRCとDAC9018K2Mの間に挟みこんで、動作確認です。

すでに動作を確認はしていますが、パターンをの修正があるので最終的な動作確認を行いました。

動作確認です。

結局・・・・

構想から1年以上かかってしまいましたが、ようやく完成にこぎつけました。

何事もあきらめないことが大切ですね。

(つづく、かな?)