メモリーバッファーは復活するか? 2014.11.4

Raspberry Piをいじっているうちに、もういちどディジタルオーディオの基本にもどってジッタをどのように低減

すべきかを考えるようになりました。その一つの解はジッタクリーナであり、またはメモリーバッファーかな〜と

思いをめぐらすうちに、ムラムラとメモリーバッファーについてまたまた作りたくなりました。

過去の記事をみていると、最初にメモリーバッファーを作ったのはすでに7年前になるんですね。

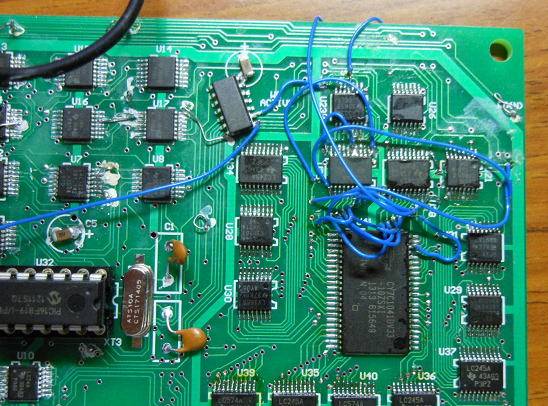

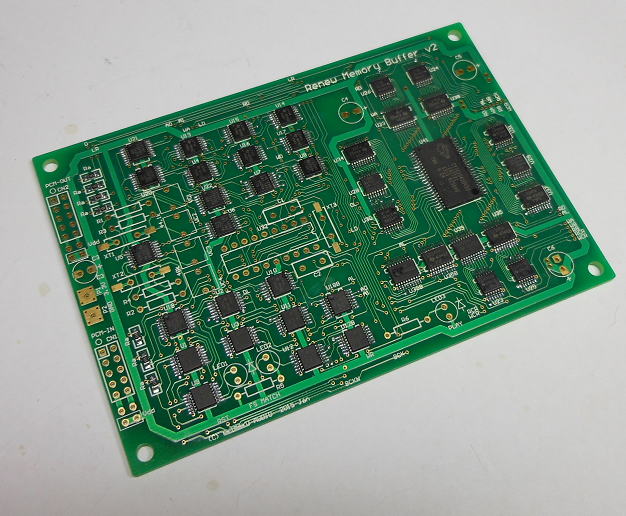

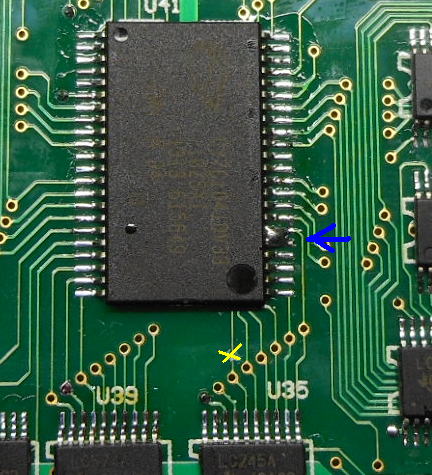

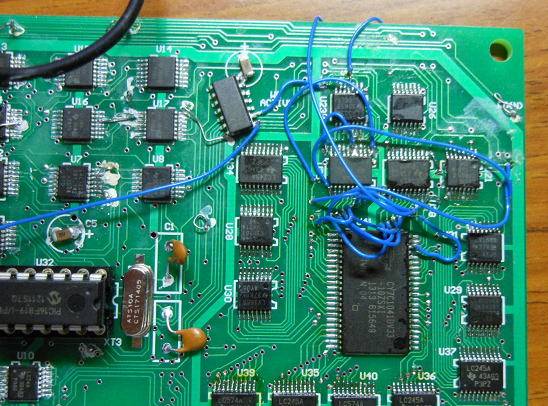

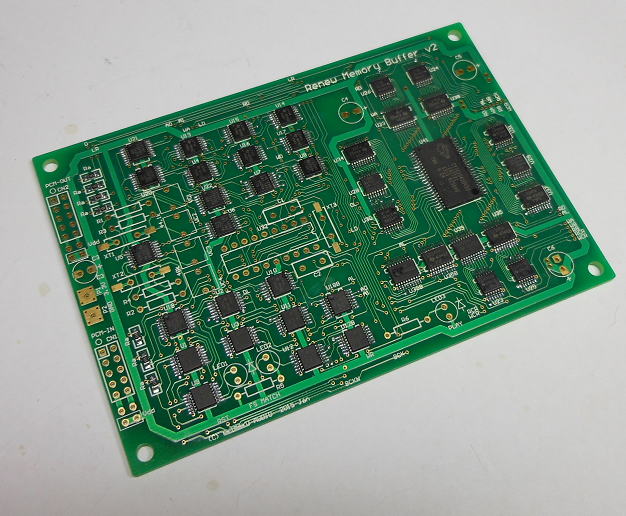

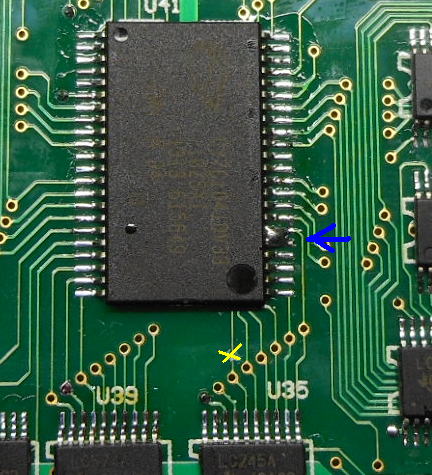

7年前に作ったメモリーバッファー。

以前に作ったメモリーバッファーは結構お気に入りでしたが、今回路図をみると結構反省点があります。

一つは、最初は44.1kHz前提で作ったことから遅いロジックIC(ノイズは少ないが・・・)を使って、

さらに非同期カウンタを多様し、論理和、論理積のゲートを多様したために、高速動作時には

グリッジに悩まされたり・・・。また、部品も多く2枚構成となってしまっていることなど、などです。

次に考えるなら、もう少しスマートな設計にしたいものです。

かといってFPGAを使う知識もないので、従来通りロジック回路で攻めるわけですが、

コンセプトとしては下記のように設定してみましょう。途中で挫折するかもしれませんが・・・。

1.PCM入力対応

この際、SPDIFはやめてPCM入力オンリーでいきましょう。さらにI2S、右詰、左詰のすべてのフォーマットに対応。

2.384kHz対応。

すくなくとも192kHzは余裕で対応して、素子スペックの点からは384kHzまで動作する回路設計にする。

3.ボードは1枚

これはシンプルに1枚で収まるように回路をシンプルに。でも機能は落とさずに。

4.3.3V電源動作

5.周波数自動追従

これはPIC1個載せればこと足るので実現容易でしょう。

考える上で、使用する素子の選定は重要です。一つはロジックICに高速タイプのものがあるかどうかを確認した上で、

採用を決める必要があります。とくにシフトレジスタやカウンタなどは、すでに絶滅危惧種となっているけらいもあるので、

入手の可能性を考慮したうえで、選定する必要があります。

そして重要なのは高速なRAMの選定です。

これは秋月で下記のSRAMが安価に手にはいります。アクセスタイム10nSなので、かなり早いです。

これを1個つかう構成がよさそうです。

|

秋月で安価に購入できるSRAMです。

だいぶロジックが固まってきました。2014.11.15

できるだけ簡素にし、かつ高速に動作させることを主眼において回路設計です。

高速で動作速度がシビアなところは同期回路にして、それ以外は非同期で設計です。

非同期回路にすると回路がシンプルにはなりますが、遅延時間には注意が必要です。

非同期回路のカウンタはメモリ書き込みのアドレス生成につかいますが、

アドレスが確定するには200nS程度はかかると見込んで、アクセスタイムに余裕のある設計をします。

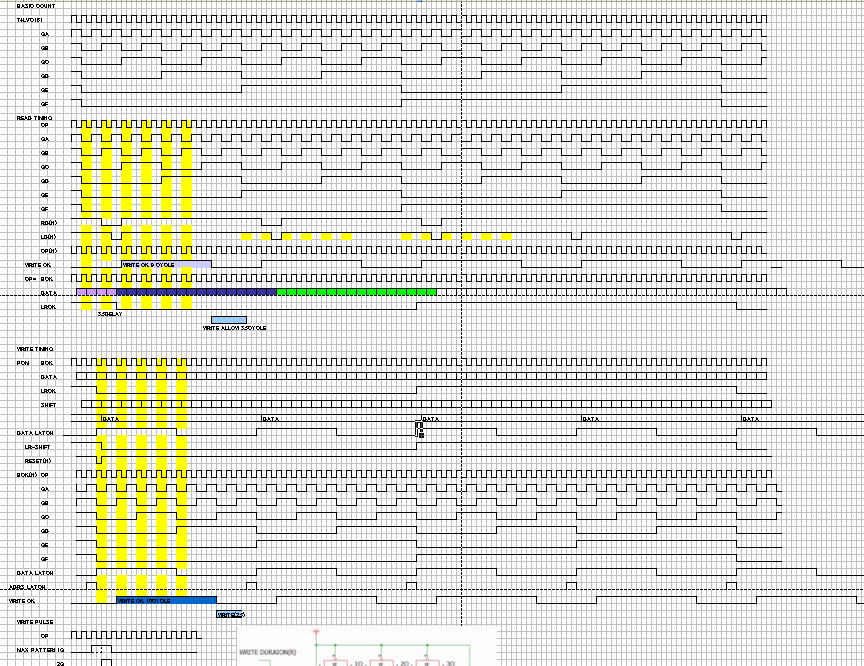

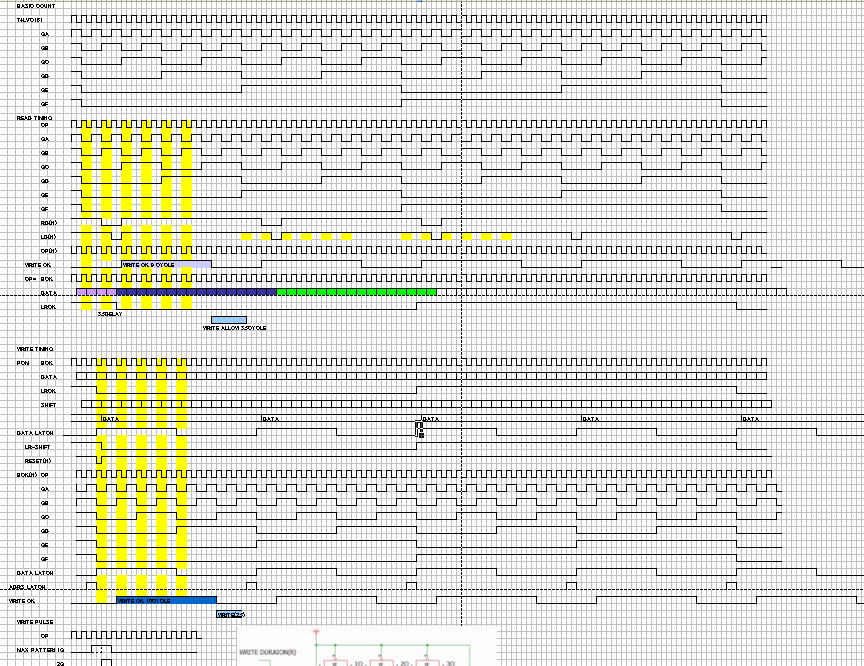

まずはタイミングチャートを描いて動作を決めます。

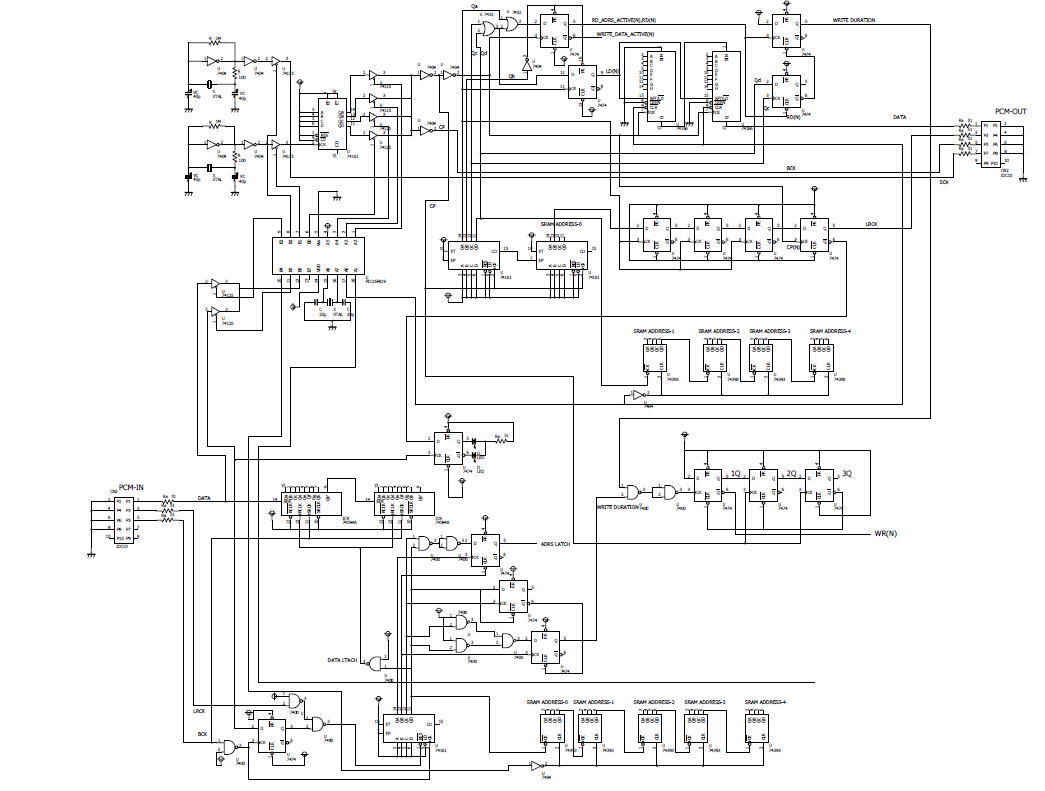

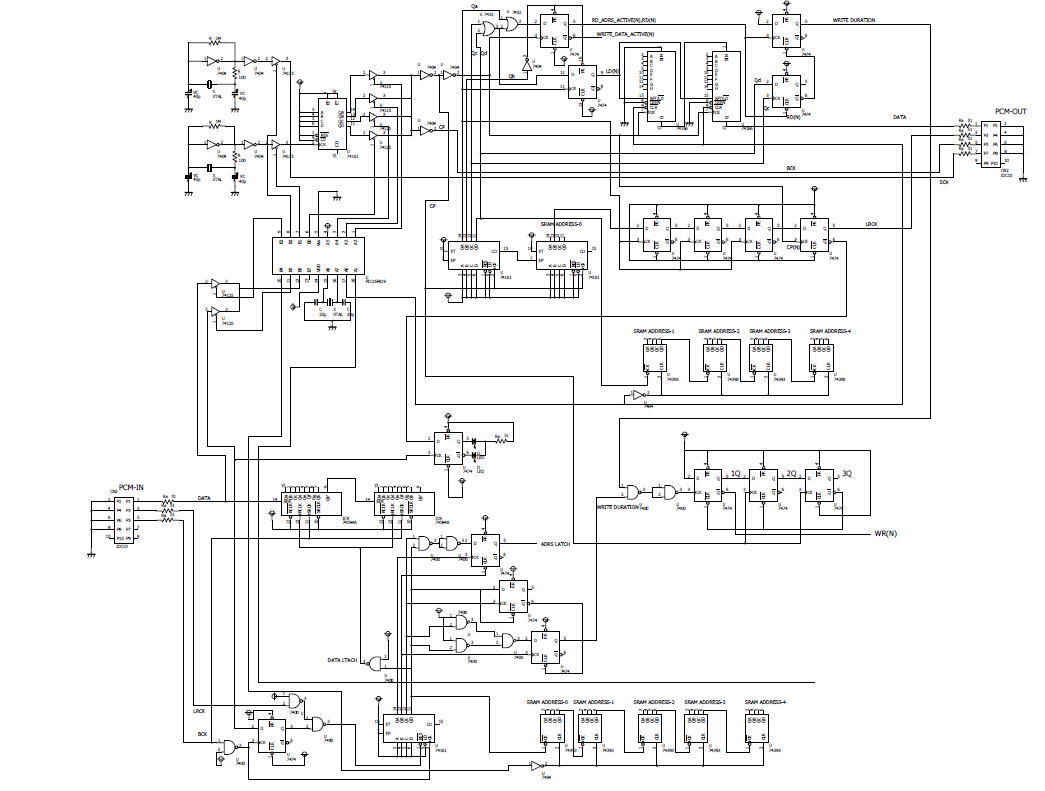

つぎはタイミングチャートを実現するロジックを考えていきます。

ICの数を数えればおよそ40個弱です。

SOICでは無理だけどTSSOPをつかえば、ドータボードなしで、なんとか基板1枚に収まるかもしれません。

収まりそう・・・

およそ必要なICは40個です。すべてTSSOPを使うことで収まりそうです。

でも、こんな密度で配線できるかな〜。

それと半田ゴテレベルもレベル4を新設しないといけません(笑)。

なんせ、TSSOP(0.65mm)を40個間違いなく半田づけするとなると、かなりの集中力が必要です。

まあ収まるでしょう。

いろいろと調査 2014.11.17

前回のメモリーバッファーで、改造が必要だな〜と思ったところが一点あります。

それは、データが一定時間ゼロ(無音)状態になったら、リングメモリーをクリヤする機能をいれていました。

こうすることにより、通常のCDでの曲間では無音になるので、そのときにメモリーをクリヤすればメモリーの

オーバフロー/アンダーフローによる音跳びはまず発生しません。

PCM信号をダイレクトに生成する場合、たとえばDAC2707などでPCM信号を生成する場合などは

まったく問題ありません。というのも無音のときはデータは完全にゼロになります。しかし、一旦FFASRCに入れると

ゼロデータが入力されても出力にどうやら±1〜2程度のデータが漏れてでることがわかりました。

したがって、FFASRCを一旦介すると、ゼロデータによるメモリーのクリヤー機能が動作しないことになります。

そこで、どの程度のデータが漏れ出るかを調べて、ある一定以下であれば無音と判断しようと考えています。

この機能の実現にはPICを使います。

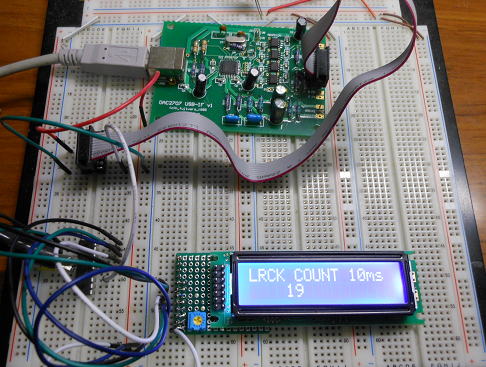

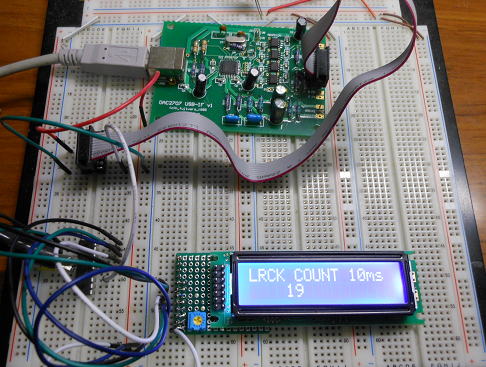

まずはダイレクト出力のソースで確認

まずはDAC2707の出力で確認です。データのカウントのためにPICで10mSのデータの変動(0,1の繰り返し)を

調べてみました。

DAC2707の出力データの確認です。

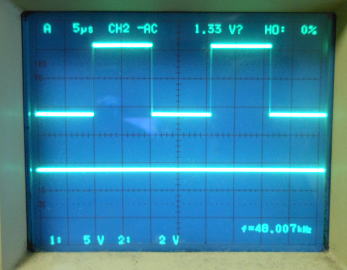

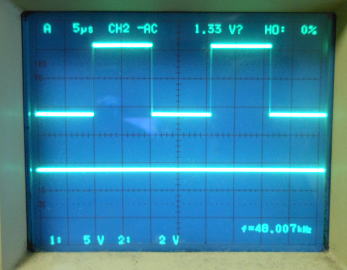

下の写真の通り、無音時(停止時)は完全にデータがゼロになることがわかるかとおもいます(48kHz出力時)。

DAC2707無音時はデータはゼロです(上:LRCK、下:DATA) DAC2707正弦波出力時(上:LRCK、下:DATA)

つぎはFFASRCを接続してみる。

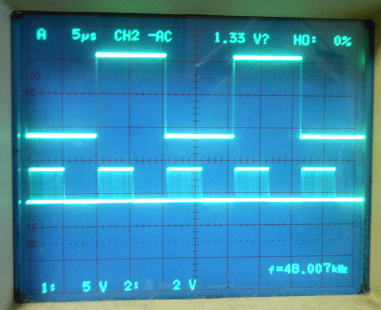

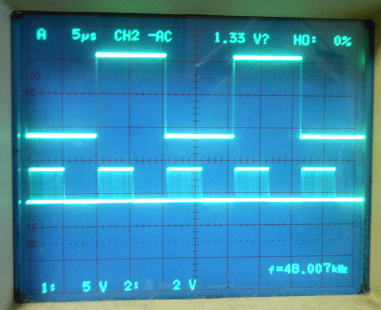

FFASRCを接続したあとのデータを観測すると、無音時にも出力データがでていることがわかります。

FFASRCの出力を確認してみましょう。

FFASRC無音時はデータは若干の出力あります(上:LRCK、下:DATA)

ではどのくらいデータの変動があるかを調べてみました。

下の写真のように、当然のことながらfsがあがるとその数値も大きくなります。

無音時では230程度(48kHz時)

無音時では930程度(192kHz時)

正弦波を出力すると、数値は一気にあがります。

正弦波では5800程度(48kHz時)

正弦波では23000程度(192kHz時)

以上から、入力周波数に応じて閾値は変更必要ですが、たとえば48kHzなら400以下、192kHzなら1500以下程度を閾値にして

データのリングバッファーをクリヤしようかな〜と考えたりします。

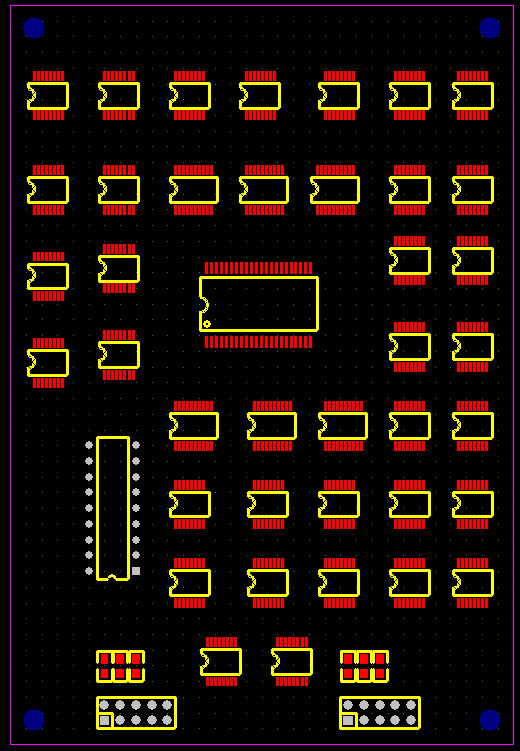

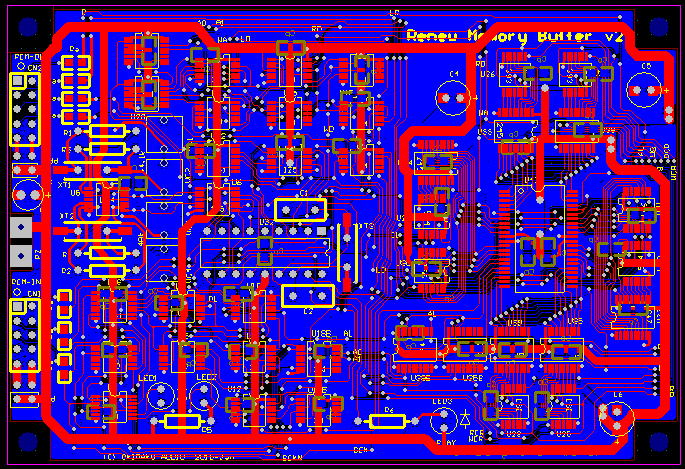

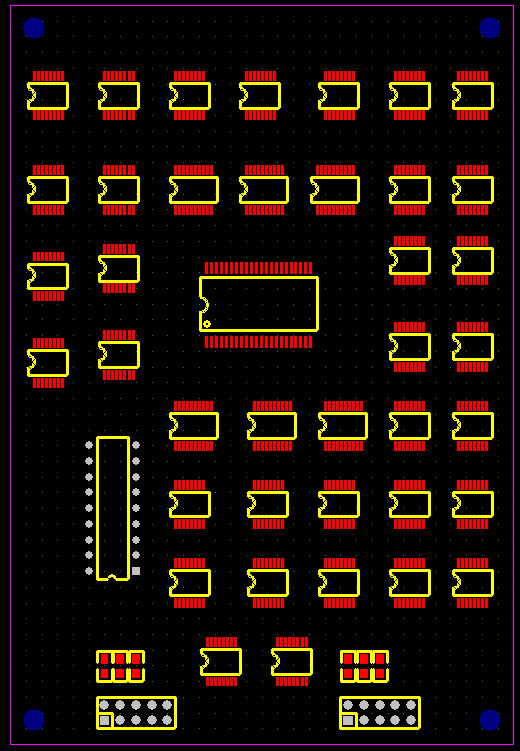

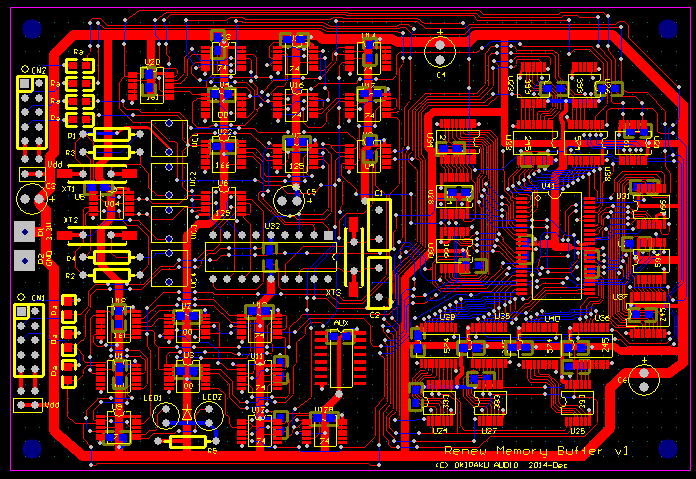

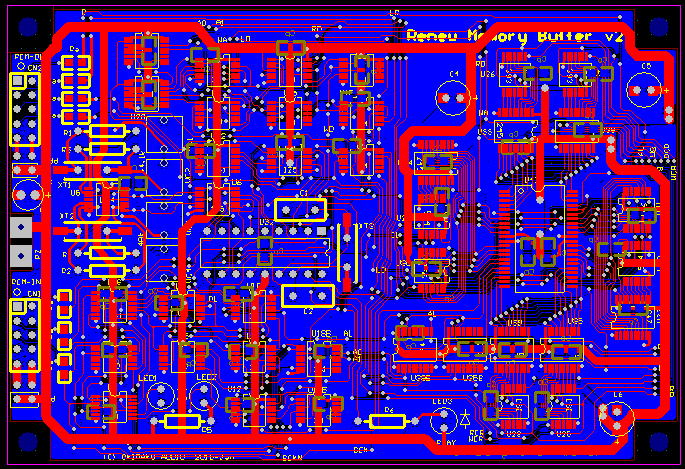

アートワークを描いてみよう 2014.11.29

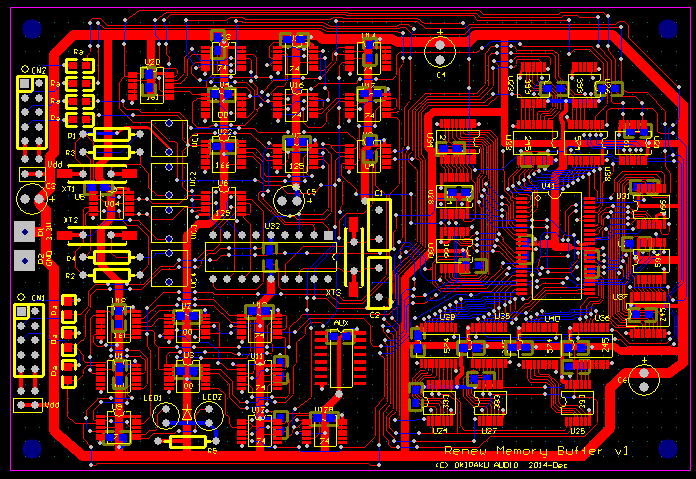

構成がだいぶ固まってきまったのでアートワークを描いてみました。

今まで以上に密度の高い配線です。

基板作成にはデザインルールがあって、35umの銅箔だと最小線幅0.15mm、線間0.15mmで、

いつも使っている銅箔厚さ70umでは最小線幅0.20mm、線間0.20mmと規定されています。

個人的には別の基準があり、少し余裕をもたせて最小線幅0.25mm、線間0.250mmで設計しています。

しかし、今回は最初から銅箔厚さ70umぎりぎりでのデザインルールでアートワークを描いています。

ひょっとして、部分的にはデザインルールを破っている場所があるかもしれません。

となると35um銅箔で作る必要がでてくるかな〜と思ったりです。

しかし、これからの配線チェックが大変です。

システム化されたCADだと、回路図と正しいかどうかは機械的に判断してくれますし、デザインルールに問題ないかもチェックできます。

私のつかっているCADもその機能はあるのですが、なんせ古いものでライブラリーの中身が古くてメンテしていないので、

その機能を生かせずにいる状態です。

そろそろ新しいCADほしいな〜。

結構密度高いです。

試作にかかりましょう! 2014.12.5

とりあえず、配線の目視確認が完了(1回だけですが)したので試作に出してみましょう。

やはり、線間の間隔でデザインルールが守られていないところがありました。70um銅箔の場合、

最少線間は0.2mmですが、一部0.175mmになっていました。これを満たすためには、色々と

修正必要なところがあるので諦めて、35um銅箔で試作することにしました。35um銅箔だと

線間は0.15mmまではOKです。しかし、35umでつくるとなると他の基板(70umが標準です)

と同じ面付けできないので、この基板だけ単独で試作です。それと、動く自信も少ない(?)

ので、オプションはなにも付けずに製作です(金メッキはありません)。

今回の試作での懸念事項は、修正が必要であったとしてもかなり難しいという点です。

なんせTSSOP(0.65mmピッチ)ですべて部品を選定してますからね。SOパッケージ(1.27mm)で

あれば、なんとでもなりますが、流石に0.65mmピッチのリードに個別にジャンパーを飛ばすのは

大変です。パターン上の切った貼ったで済めば助かりますが・・・。またオシロのプローブを

当てるのも一苦労です。

まあ、すでに試作は発注しているので完成を待ちましょう。

プリント基板CADについて

今回の試作でも、回路図から配線パターンのチェックは手作業で行っていましたが、通常は

回路図と基板パターンの整合性は機械が勝手にやってくれます。これは回路図を作った時点で

ネットリストとよばれる接続表が作成されますので、これが一致しているかをパターン作成CADが

判別してくれるわけです。私のつかっているCADもこれらの機能は勿論あるのですが、なんせ古い

(WIN3.1時代のもの)ので、現在つかっているXPでは、画面周りがすこしおかしくなっていて、

使いにくいところがあるので、いまはほとんどつかっていません。そもそも回路図CADが

使いにくかったこともあり、ほとんど手描きだったこともあります。

でも、最近では回路図CADに水魚堂のBSCHをつかうようになって、これにもだいぶなれてきました。

そして、これまた最近ですがBSCHの吐き出すネットリストを今つかっているパターンCAD用のネットリストに

変換するソフトも周辺ソフトとしてあるようなので、これらを今後はつかって行きましょう。

そのためには、パターンCADの部品ライブラリ等を一部修正する必要もありますが、ぼちぼちを始めましょう。

新しいCADとしてKiCADなどのフリーのソフトも紹介していただきました。機能とかをみていると

無償とは思えない充実ぶりですが、さすがに古いCADとはいえ10年来もつかっている、かなり手に馴染んで

いることもあり、新しいCADを触ってみてもなにかぎこちなさがでてきます。それと、どうも部品のデザインが

若干異なる点も、すこし違和感を生じているところかもしれません。

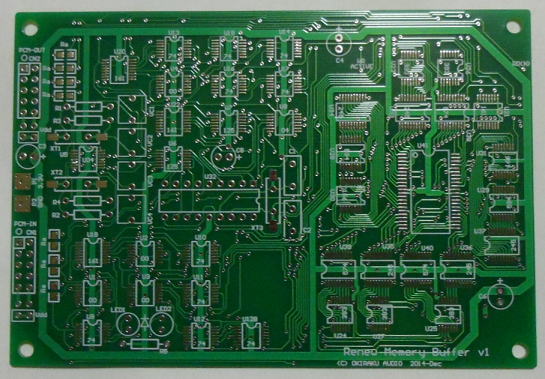

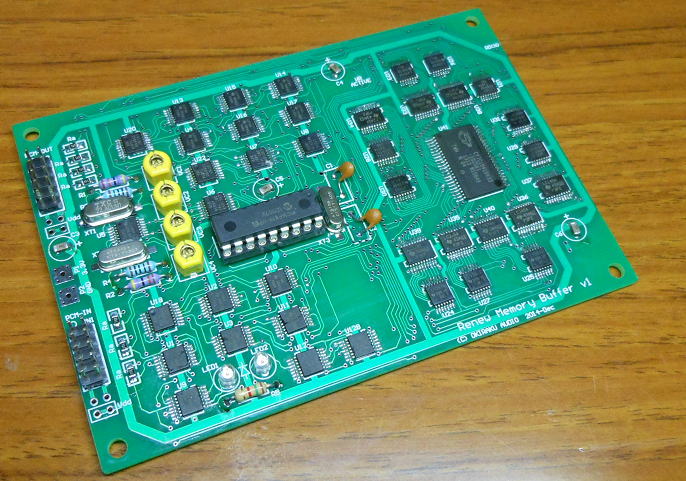

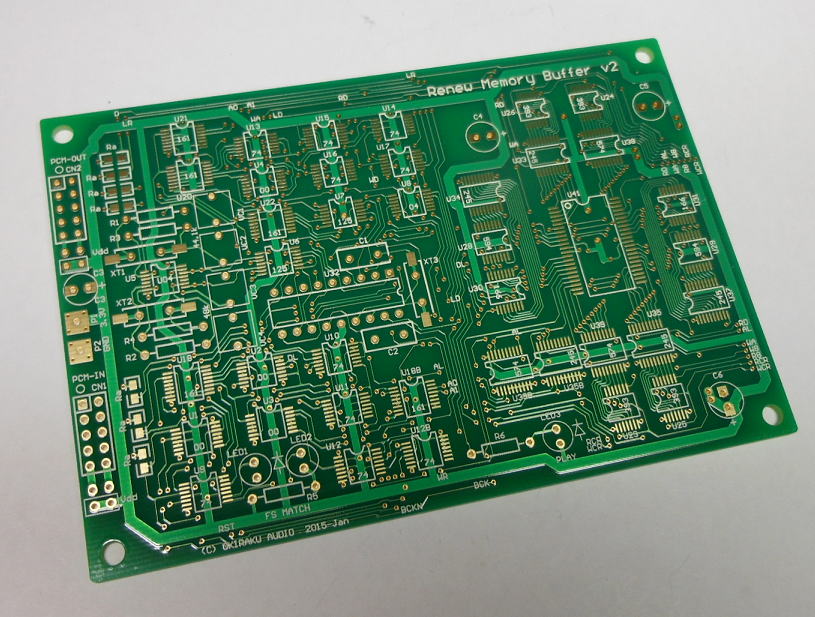

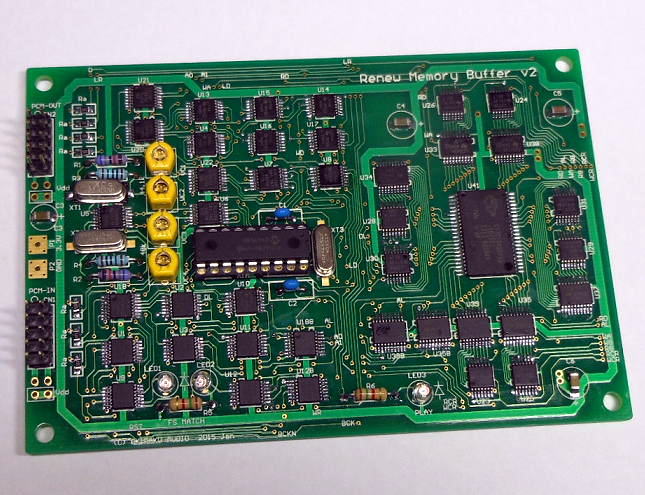

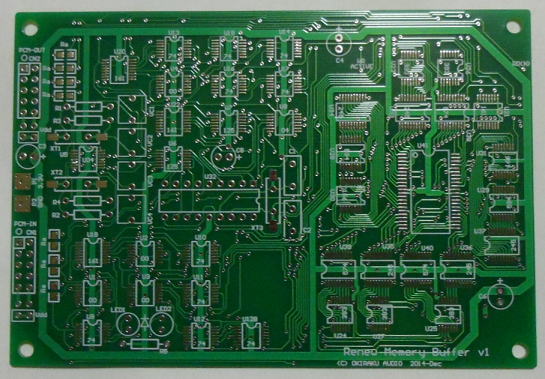

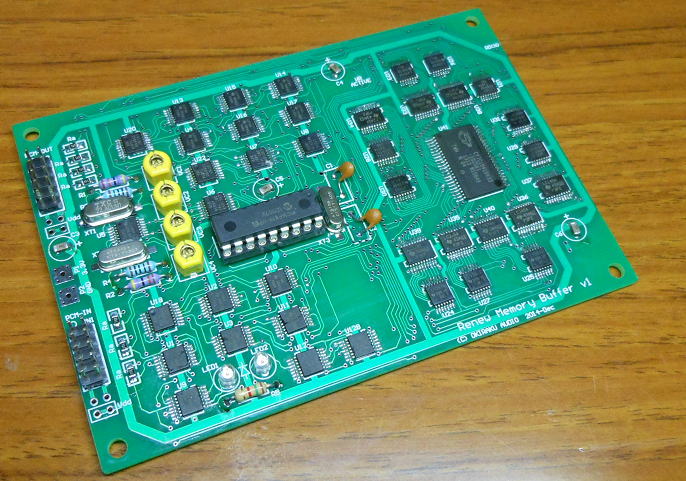

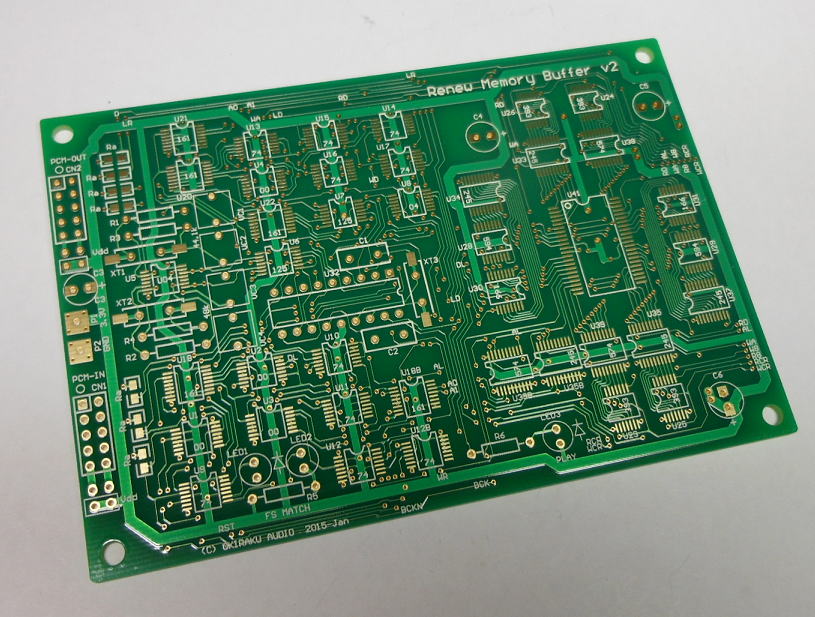

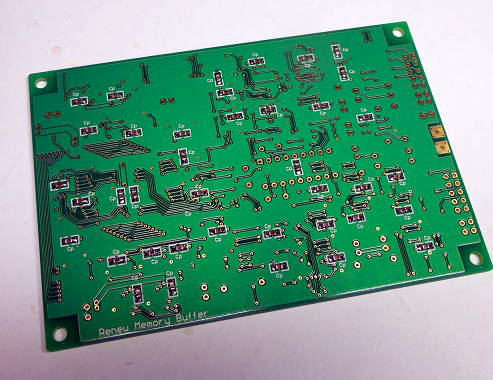

試作基板完成しました! 2014.12.9

試作基板完成しました!

いや〜、画面上でみていても細かい配線だな〜と思っていましたが、実物をみるとやはり細かいです。

なんせ、以前のMBみたいに大き目の基板2枚に分けていたものを小さめの基板1枚に収めましたからね。

使用チップも0.65mmピッチのTSSOPばっかりだし。

まあ、RasphberryなどのCPU基板と比べれば配線も太いし、線間も広いのですが、それでもオーディオ用とは思えないです。

もっともPCなどのデザインルールは線太さ0.1〜0.125mmでしょうから細いわけです。こんなの、少しでも異物やほこりがはいれば

容易にパターン切れを起こしてしまいます。クリーンルームあるいはそれに準拠した部屋で作っているのでしょうね。

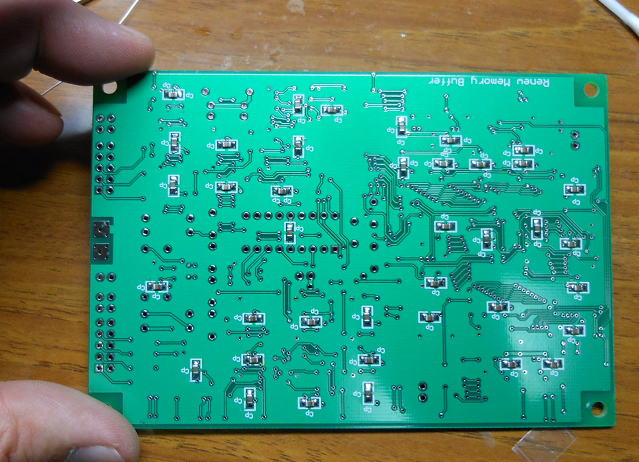

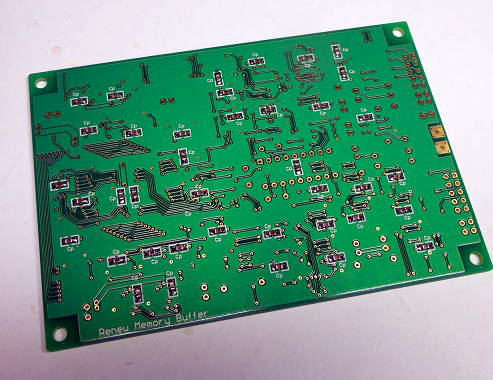

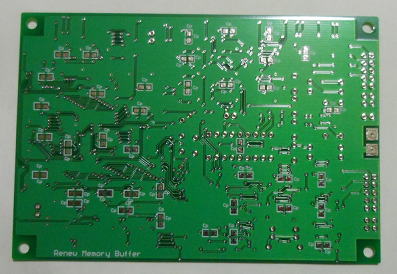

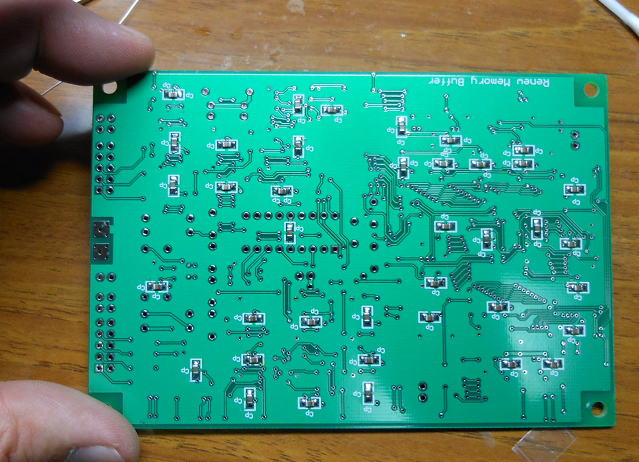

部品面のパターンです。

半田面のパターンです。

さて、部品を実装していきましょう。部品の大部分は表面実装部品です。そのうち約40個のTSSOPの半田付けがまっています。

そういえば以前に32パラのFN1242Aを作りましたが、このときもSSOPを32個半田付けしたのですが、2個ほど半田不良を

引き起こしています。今回は大丈夫かな? 久しぶりに実体顕微鏡の出番があるかもしれないです。

そういえば、最近パソコンにつなげるマイクロスコープも安くなりました。これらをつかうと便利かもしれません。

一度、秋月で購入しましたが、フレームレートが遅い(画像の追従性が低い)こともあり、1度つかった限りでした。

やっぱり、リアルタイムに画面が確認できるほうが嬉しいです。

さて、半田付けはまずはTSSOPからです。この基板での部品番号は品種別に割り振っているので、基板のあちこちに番号がとんでいます。

基板のIC番号はU××とありますが、まちがわないようにパターンの中にICの型番も入れています。ちょうど74LVC125なら125と書いています。

これがなければ、部品番号だけだと間違う可能性がでてくるでしょうね。

まずはTSSOP部品を取り付けました。

半田付けする量は多いですが、表面実装部品の半田づけはゴミ(リード線等)がほとんど発生しないので、

以外と作業は楽です。ゴミといえばICをパッケージしているプラスチックリールくらいです。考えればエコですね。

さて、ICの取り付けが完了しました。次は裏面にうつってチップコンデンサのとりつけです。

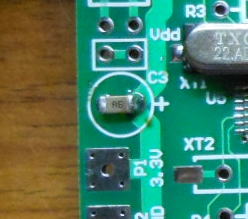

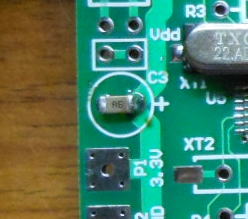

裏面のチップコンデンサのとりつけです。

表面の電解コンデンサはチップコンデンサに入れ替えています。

背が低いほうがなにかといいですから。

これがおわれば残りの半田づけをしましょう。

完成しました!

さて、電源を入れるまえには、再度の半田チェックをしておきましょう!

しかし、電源入れるの怖いな〜。

動作確認・・・バグ続出 2015.1.9

基板完成しました。案の定バグ続出です。

まったく動かないです(笑)。想定範囲ですが・・・・

一度見直したつもりでしたが、配線ミスもあれば致命的な論理ミスもありました。

まあ、それらの修正は配線数的にはすくないのですが、一箇所74LVC574と74LVC245を間違えた

ところがありました。おなじ20PのTSSOPなのでうっかり配置間違えです。

この修正は結構な配線数が必要でした。それよりなにより、修正自体が大変です。

なんせ、TSSOPですからピン間は0.65mm。それらからジャンパーを飛ばすのも大変です。

さらに試作ということもあり35umの銅箔基板でつくったのでカッティング自体は

簡単でいいのですが、ランドが小さいこともあって強度が低く、ちょっとひっぱたら

ランドごと浮き上がったりと、まあ苦労しました。

修正箇所がタンマリあります。

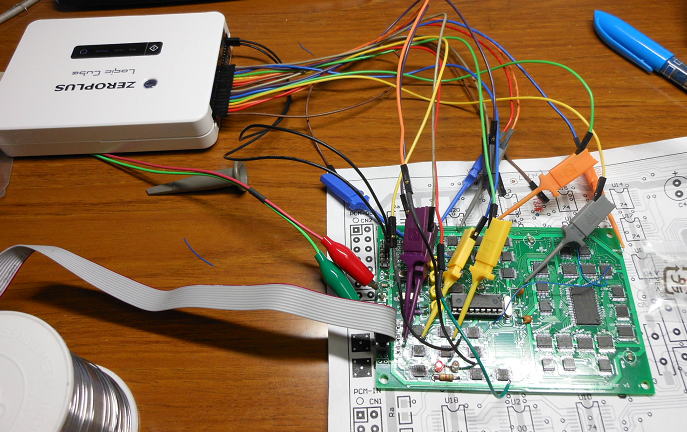

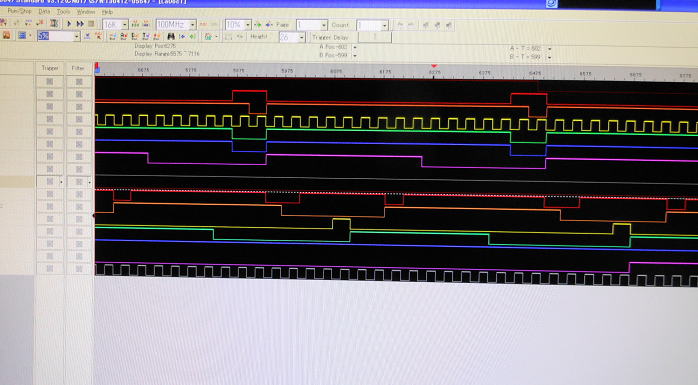

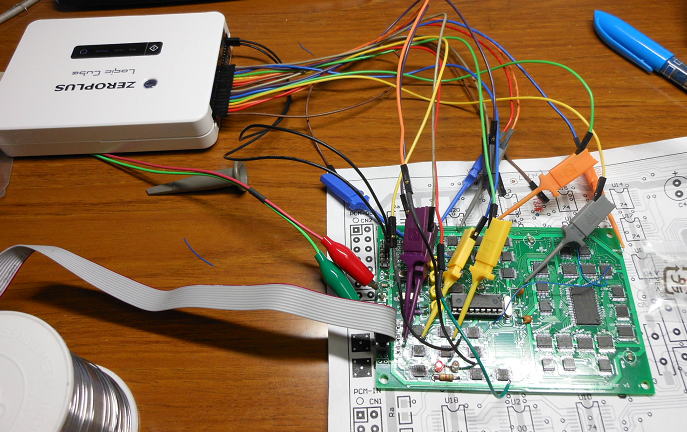

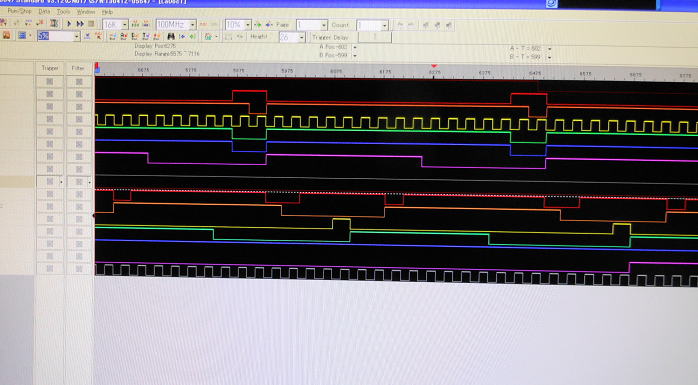

それにしても、論理テストを2chオシロだけでするのは大変そうだったので、

デバッグ途中でロジアナも購入しました。ロジアナといっても秋月で売っている

安いものです。16chで100MHzサンプル1Mメモリの一番廉価なものです。でも、

これがあるとないとでは作業性が違います。

最初はオシロだけでデバックですが、限界があります。

ロジアナをつかって一番複雑なメモリ制御の排他制御の部分については問題

ないことを確認しました。でも、どうして分からないバグがあり、なかなか発見

できませんでした。

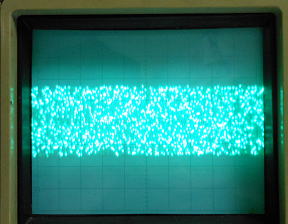

どういうバグかといえば波形はでるのですが、微妙に崩れます。その崩れ方が

時々刻々変わるというものです。とくに、書き込みと読み込みのFSの差が大きくなる

と波形が崩れる間隔が短くなることもあり、メモリ制御の排他制御のロジックそのものに

問題があるかとおもいましたが、なかなか考えずらいところもあり、色々と考えた

あげく、ようやく発見です。

ロジアナも導入しました。やはり文明の利器は便利です。

論理回路の問題の発掘には便利です。

でもバグの原因の発掘難航です。

メモリーバッファーはリングバッファーになっており、計算上は16K単位(1単位は

64Bit/8Byte)のリングになっているはずなのですが、どうやらそのリングが非常に短くて、

実際には4単位程度になっていると考えればなっとくです。すなわちメモリ制御の部分

には違いないのですが、アドレスカウンタのところに問題がありそうです。というわけで

原因が推測できれば、あとはチェックするのみ。

見つけた!

ようやくバグを見つけました。なんたるポカミスでしょうか?アドレスカウンタのICの部分の

半田不良でした。なんでこんなんものを見つけるのに時間がかかったのか、不思議ですが、

まあこれでバグはなくなり論理回路は完成です。

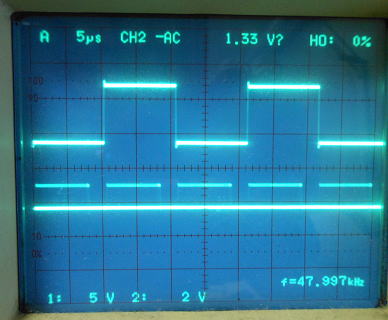

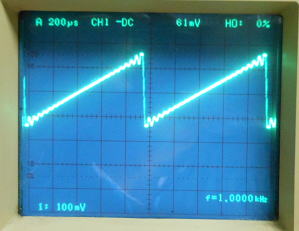

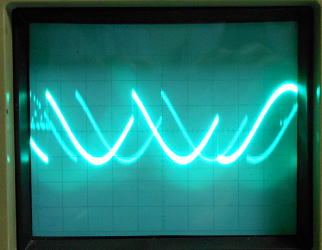

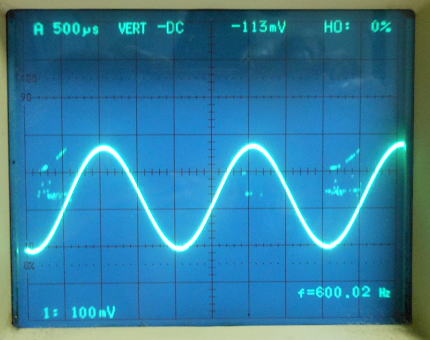

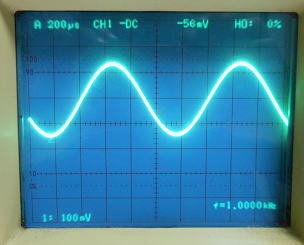

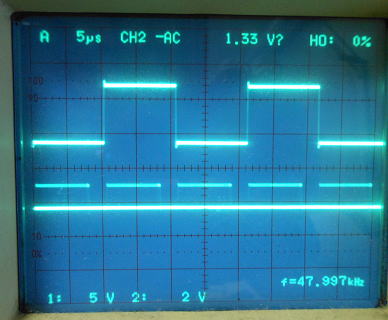

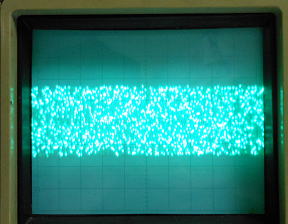

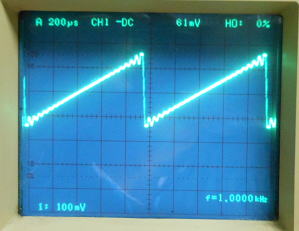

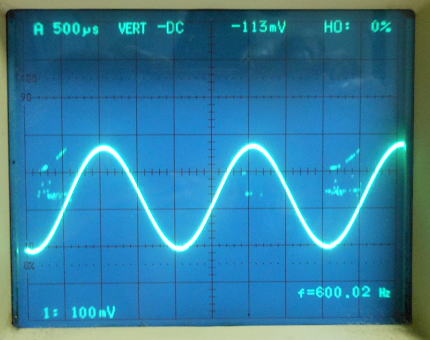

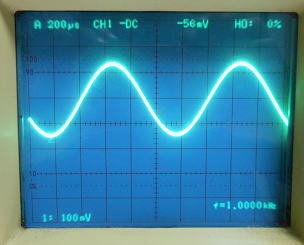

ようやく動きました!

192KHzで動作させています。

同期回路を基本としているので192kHzでも安定して動きます。

ただし、修正箇所が多すぎてこのまま、パターンを修正するだけでは済まない(ICの追加も必要)

ということもあり、再設計をしなおす必要ありでしょう。

まずは試聴 2015.1.10

PICのソフトを作成して試聴です。PICの役割は周波数の自動判別とデータのMUTE検知です。

MUTE検知をすればバッファーメモリーのアドレスカウンタをクリアします。この部分をロジックで組むと3〜4個の

ICが必要なのですが、PICを載せることもありこの機能を持たせました。

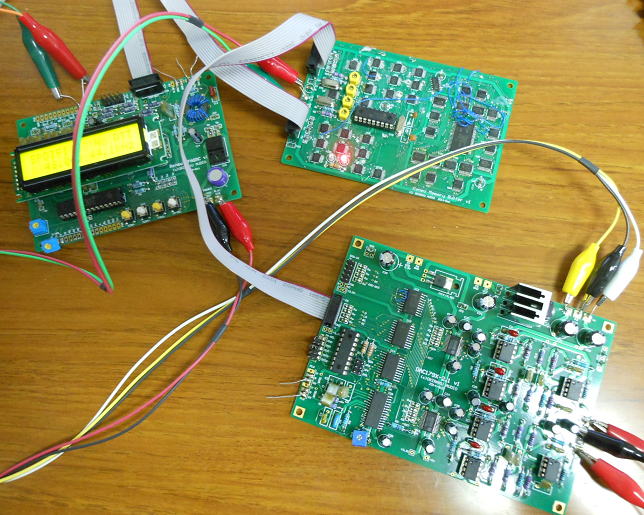

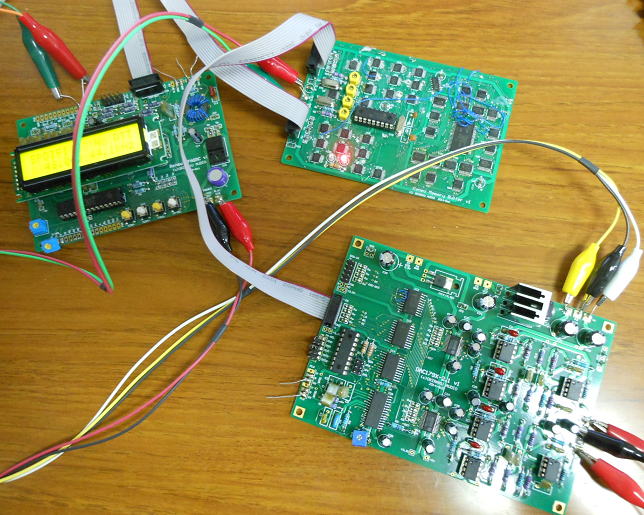

試聴の構成は

Renew FFASRC → メモリーバッファー → DAC179X-2.1

です。

ソースは木住野佳子さんのFACEを選びました。試聴時の最初の印象は音の粒立ちがあがったような、

まあ主観全開です(笑)。それより音のスタートがワンテンポ遅れるのが面白いところです(44.1kHz再生時

で0.7秒程度遅れます)。

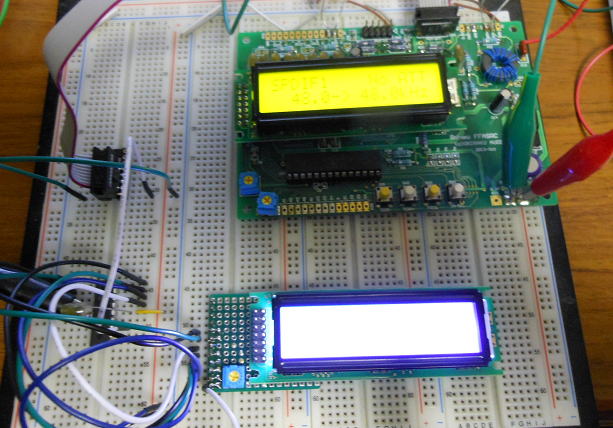

試聴です。

全面改訂!

部品配置を見直して全面的に書き直しました。さらに表示機能として再生状態を示すLEDも追加しました。

パターンは見直すたびに間違いを発見(笑)してしまいますが、まあこれで作ってみましょう。

V2基板を描いてみました。

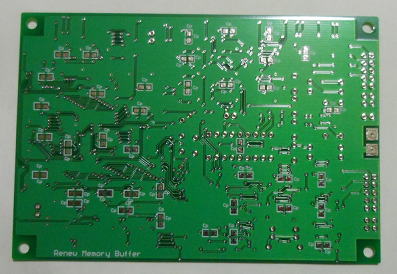

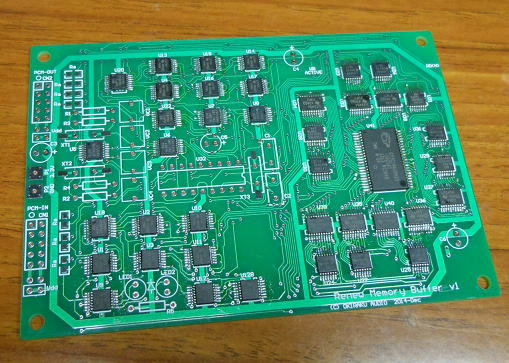

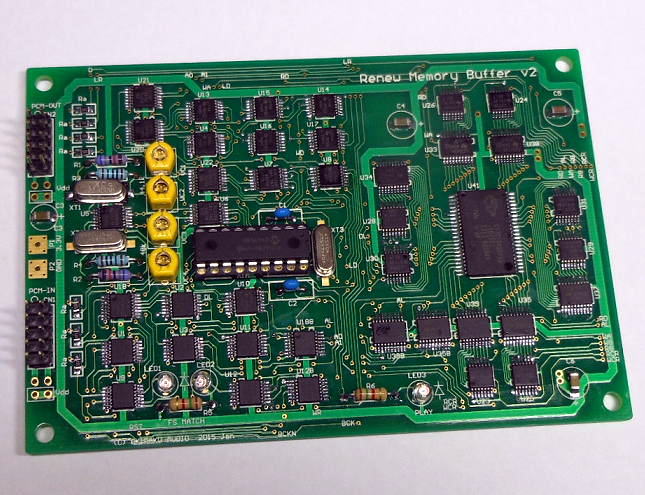

v2基板完成しました。 2015.1.20

さて、ド平日にもかかわらず基板が届きました。この基板も試作品に終わるのか、はたまた頒布できるか・・・。

頒布に耐えられるように金フラッシュ、70um銅箔でつくっちゃいましたが、さてさてどうなることやらです。

でも、基板をみていると作りたくなるな〜。

いまから作ると、とてつもなく遅くなりそうな予感がするのだけど〜〜、えい!作っちゃえ!。

V2基板が出来上がりました。

表示はV2になっていますね。

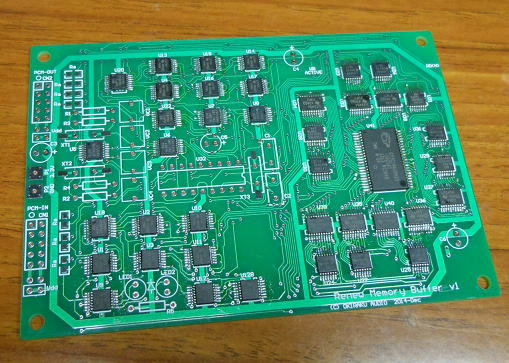

表面実装部品がとりつきました。

ここまでくれば、富士山の9.5合目くらいです。TSSOPのICをたっぷりの半田でブリッジを気にせずとりつけて、

あとは一気に半田吸い取り器でブリッジを取り除いていく方法をつかっています。もちろん、その後の目視検査は

入念にやります。ここで手を抜くとあとあと間違いを見つけるのが難しくなります。

表面実装部品がとりつきました。

裏面にはチップコンデンサをとりつけます。ICのパスコンになっています。

完成!

あとは通常部品をとりつけて完成です。

電解コンデンサは背が高いので大容量セラミック(100uF/6.3V)をとりつけました。

秋月で10個200円程度で購入できます。

お出かけ用の写真です。

ワクワクドキドキ動作確認!!!!アチャー

電源投入はいつでもワクワクドキドキ。

問題なく動くとヤッター、動かないとシュン・・・・ですが、今回もうごけばラッキー程度に思っている

ので心構えは大丈夫です(ホント?)。

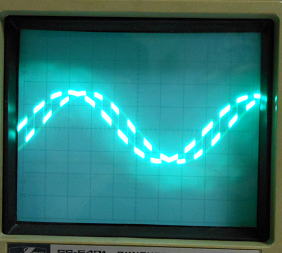

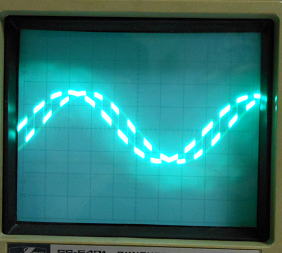

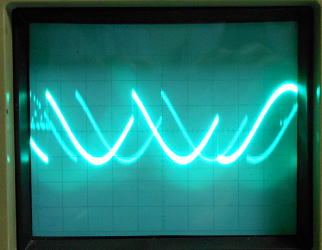

で、電源ON! あれ、正弦波がおかしく出力されてしまいます。

でも、最初の試作時はまったくうごかなかったことから考えると、波形が分割されているとはいえ、

それなりの形になっているので、大きな前進です(と言い聞かせないと落ち込むので・・・)。

まあ、最初はこんなもんです(笑)。

でも、オシロの画面を眺めるとタイミングの早い部分ではなくて、比較的時間のゆったりとして部分のミスのようなので、

おそらくアドレスカウンタに関係することだろう、というのが容易に推測されます。

で、あらためてパターンをみてみると速攻で間違い発見しました。

というのも、こんなところは間違えないだろうと思って、ほとんどノーチェックだったところだからでした。

そういったところにミスって生じるんだよね〜。

かえって簡単なところでミスってしまう典型的な事例です。

修正は簡単。

幸いにも周辺がTSSOPとはいえ0.8mmピッチのSRAM周辺で助かりました。

修正箇所は2箇所です。

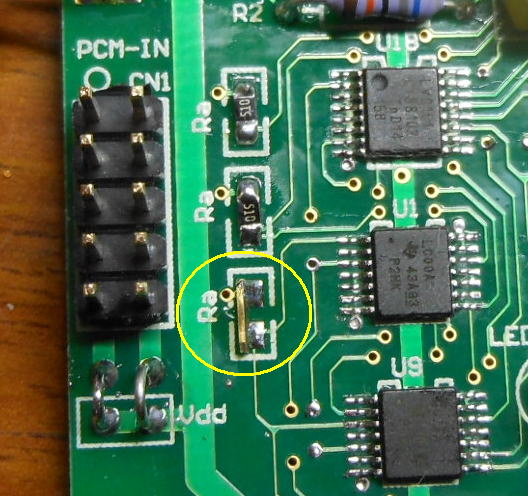

下図にありますが、

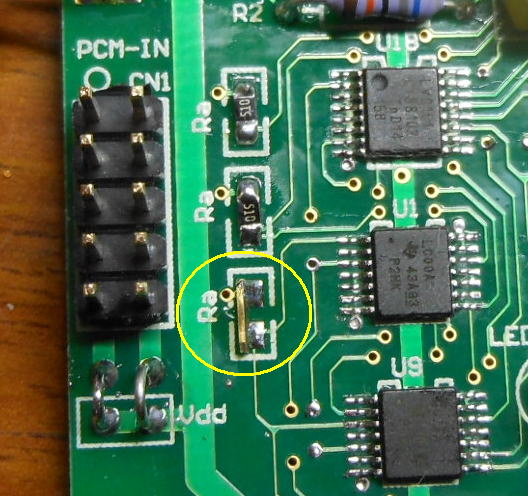

1つは黄色の×部分の切断です。これは簡単です。間違って隣を切らないように注意してカットです。

もう1つはピン間のブリッジです。SRAMは44pinですが、PIN27-28を半田でブリッジです。というのは

Pin28はN.C(無接続)なので、その隣に接続したかったので。ジャンパー線を飛ばすこともできますが、

簡単に半田ジャンパーで直るのでそうしました。

2箇所を修正。1つは切断、もう一つは半田ジャンパー(ブリッジ)です。

動いた・・・?

波形は正常にでるようになりましたが、プチプチとノイズがでます。前の試作では出なかったので

なぜかな?で、ロジック部分を半田をしなおすと、ほとんど出なくなりましたが、それでもたまにでるようです。

すこしノイズがでるようです。

おそらく接続するケーブルが長かったのと、ダンピング抵抗がソースであるFFASRCにも入っているし、この基板にも入っているので、

すこし抵抗値が高すぎたのかもしれません。ということでBCK部分のダンピング抵抗を除去してジャンパーに切り替えました。

なんせ、部品数も少なくするためにバッファーはあまり入れていないので、端子はロジック5個程度の入力負荷があります。

まあ。この程度なら問題ないのですが、容量性の負荷になると波形のリンギングやなまりに注意する必要があります。

BCK部分のダンピング抵抗をとりのぞきました。適当な切れ端でジャンパーです。

無事動きだしました。

ノイズレス状態になり無事動きだしました。

ようやくです。

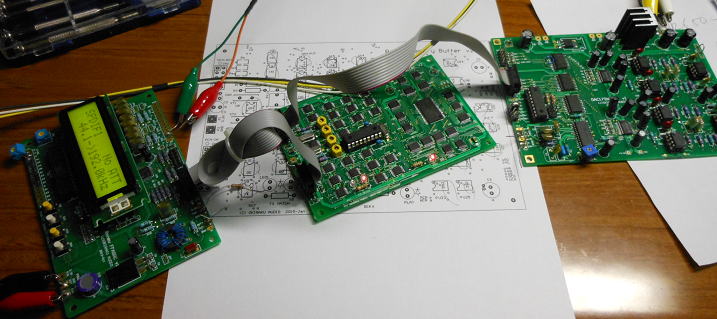

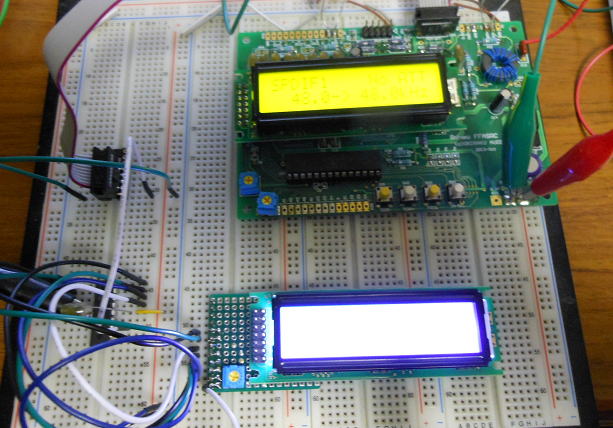

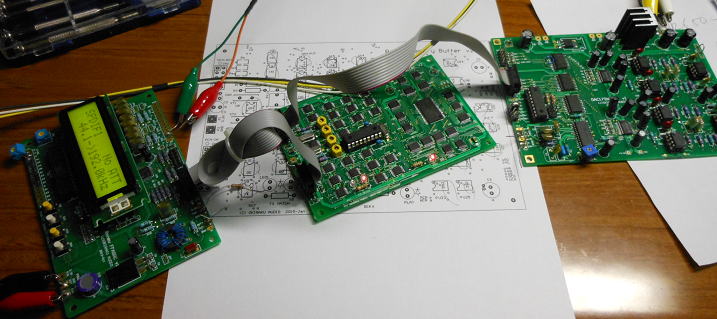

動作確認中の本基板です。

修正箇所も簡単なのですが、さらに修正版をつくろうか、どうしようか・・・・悩みどころです。

いづれにしても、無事動いてほっとしました。

この密度で基板を設計したのは、たぶん初めてです。

それにTSSOPを40個も半田付けすると疲れちゃいます!

試聴は楽しみ!

出張前の少しの時間を利用して試聴です。

Renew FFASRC → Renew Memory Buffer → DAC179X-2.1(PCM1795)

の構成です。

マイコン搭載の効果があり、周波数が切り替わっても迅速に追従していきます。

192kHzに設定すると、流石にメモリーによる遅れはあまり気にならなくなります。

180mS程度のずれですからね。

速攻で組んで試聴してみました。

バッファー容量考 2015.1.24

メモリーバッファーの動作としては、メモリーの半分まで読み込んだあとに再生を始めますが、読み込みデータの無音を

検知すると直ちに再生をやめることになります。

たとえば44.kHz再生時を考えると、このメモリーバッファーは4MBitの容量がありますから、64k単位(1単位64ビット)の

音楽を読み込むことができます。時間にすれば16k/44.1=約1.47secになります。すなわち、音楽再生時は0.735秒間

先読みして、その後に再生することになります。しかし、元の音楽データが途切れると再生をやめることになるので、

音楽の最後の0.735secが再生されないことになります。まあ、このくらいの時間なら問題ないとおもいますが、

ひょっとして楽曲のぎりぎりまで音が鳴っている可能性がないともいえません。そこで、対策としてたとえば元音楽が

無くなっても、0.735secだけは時間を延長して再生することが考えれます。しかし、これは大丈夫なのか? 答えはNOです。

メモリーに残留しているデータが不意に再生される可能性が高くなります。すなわち、音楽が消えたはずなのに、

最後に「ガガガ・・・」と音がでる場合もありえます。したがって、元音楽が切れれば即座に再生も停止する必要があります。

そもそも最初に0.735secも先読みをする必要があるのかどうか?

ここが一番の疑問です。

以前のメモリーバッファーでは書き込み周波数と読み出し周波数の差はトリマーコンデンサの調整しだいで0.1Hz以下に

するこができます。すくなくとも1Hz以下にすることは余裕です。これは書き込み時の周波数が44.1kHzとすれば

読み出し時の周波数が44.101kHzということです。たとえば1Hzの周波数差があったとして、メモリーの半分まで読み

こんで再生するとすると、何秒後にメモリーがオーバーフローするかというと64k/2/1Hz=32000秒です。すなわち

約500分です。CD1枚がまるまる曲間がないとしても高々80分ですから、この数値は余裕がありすぎです。

長くてもCD一枚分に対応できるようにすることを考えると、先読み時間は高々0.11秒程度でよいことになります。

ここで、再生周波数によらず先読み時間を一定にしたほうが、操作感覚上いいかもしれません。周波数が低くなると

再生までの時間が長くなるのは違和感がでるかもしれません。

下に、周波数別の再生までの遅れ時間を列挙してみました。

| fs |

再生開始までの時間

(sec) |

| 44.1 |

0.743 |

| 48 |

0.683 |

| 88.2 |

0.372 |

| 96 |

0.341 |

| 176.4 |

0.186 |

| 192 |

0.171 |

| 352.8 |

0.093 |

| 384 |

0.085 |

常用の最大周波数を192kHzとして再生までの時間を150ms程度に設定するのがよさそうです。

もっとも352,384kHzではメモリー容量が足りないので、これらの周波数についてはメモリーの半分読み込んだ時点で

再生が必要です。

ということで、再生開始時間を150mSを基本として、メモリーの使用量を整理してみました。

|

メモリーに半分まで

読み込んだ場合の

再生開始までの時間 |

再生開始時間 |

メモリーのバッファー率 |

| 44.1 |

0.743 |

0.15 |

20% |

| 48 |

0.683 |

0.15 |

22% |

| 88.2 |

0.372 |

0.15 |

40% |

| 96 |

0.341 |

0.15 |

44% |

| 176.4 |

0.186 |

0.15 |

81% |

| 192 |

0.171 |

0.15 |

88% |

| 352.8 |

0.093 |

0.093 |

100% |

| 384 |

0.085 |

0.085 |

100% |

192kHzまでは150mSで固定です。ただ、192kHzではメモリーの88%までバッファーを使用しますから

4MBitのメモリーもあながち無駄ではないことになります。反対に44.1kHzなどの低い周波数では

すこしメモリーとしてはオーバースペックということになります。

さてさて、どうしようか考えどころです。

というのも、再生機種が複数あった場合には、片方に周波数を合わせたとしても、他方が大幅に異なる可能性もあります。

水晶の周波数精度は一般に50ppmなので、2台再生機器がある場合は最大で100ppmの周波数差が考えられます。

100ppmの周波数があると、44.1kHz時は64k単位のメモリーは約7000秒の余裕がありますのほとんど問題にならないでしょう。

ただし、150mSの先読みでは不十分で、約1400秒(20分ちょっと)で、音の途切れが発生することに繋がります。

192kHz再生時だと、さらに顕著で5分ちょっとで音途切れが生じます。

やはり、余裕をみるとすべての周波数で、メモリーの半分をきちんと読み込んでから、再生したほうがいいようです。

製作の補助情報

今回のRenew Memory BufferはTSSOPが主体で40個以上のICを間違いなく半田付けが必要で

難易度は過去最高とおもいます。1つ1つを確実につけていけばいいのですが、途中で集中力が

続かなくなってしまいます。

電源を入れて動かないとなると、どこが悪いかなかなかオシロがないと見当がつかないのも事実ですが、

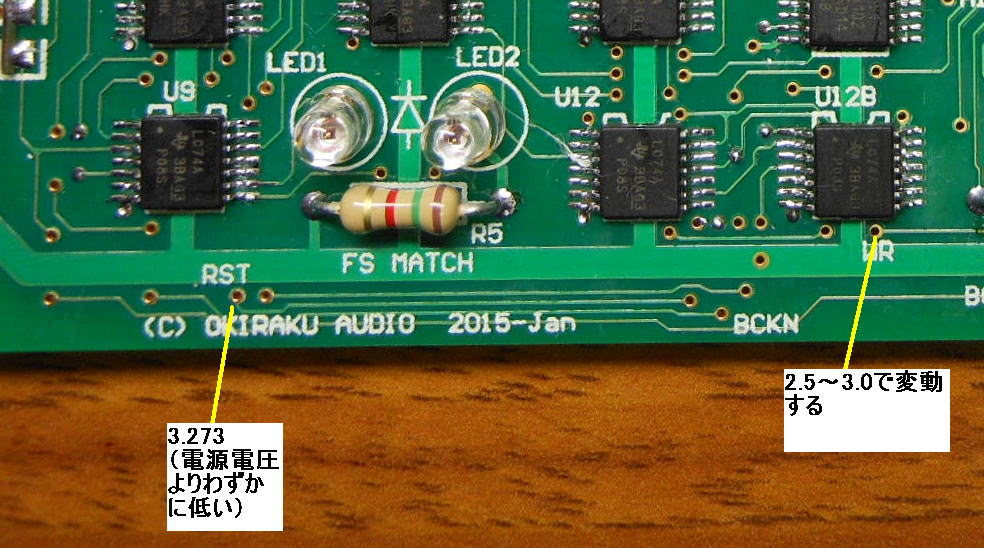

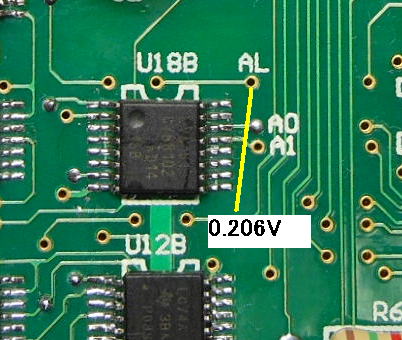

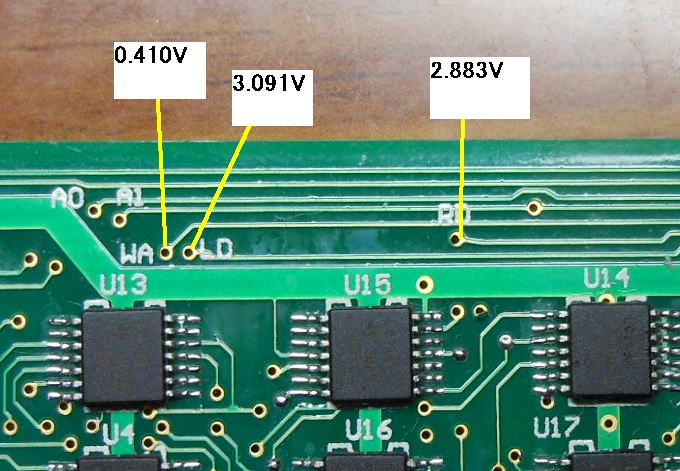

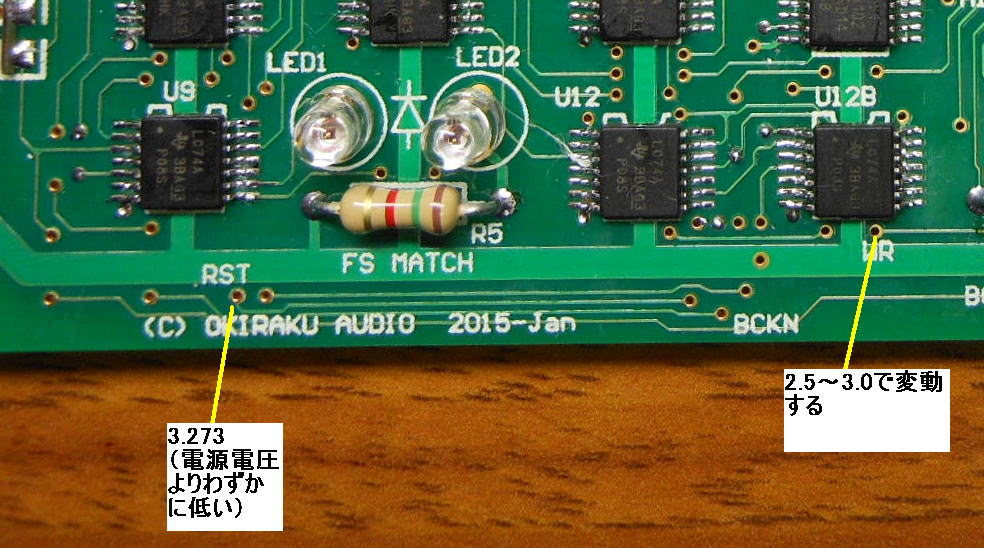

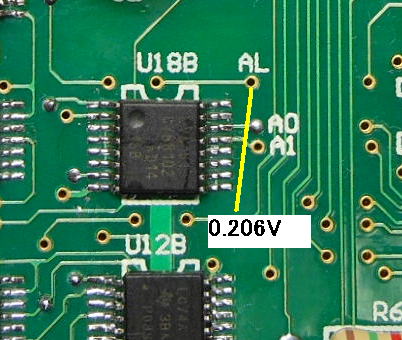

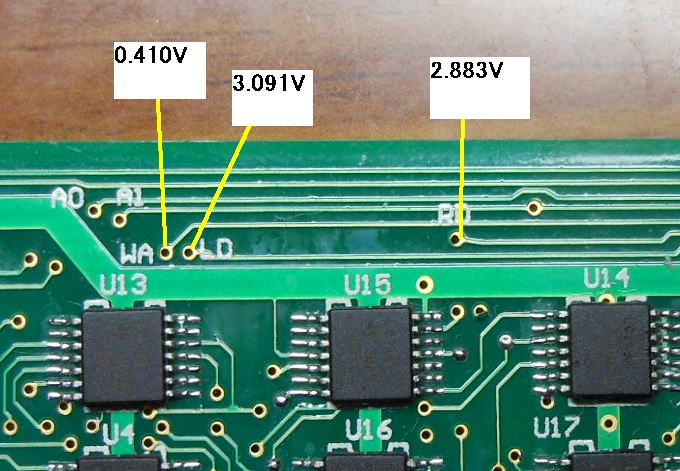

ある程度テスターだけでもデバッグできるように代表的なタイミングのところの電圧を測定しておきまし。

基本はパルス波形部分ですが、デューティ比が違うので電圧をみれば波形が正しいかどうかの見当は

つけられると思っています。

1/8スタート版です。 2015.4.28

メモリーバッファーを通すと再生までに時間ラグがあります。

44.1kHzだと0.7秒程度遅れます。音楽のみだけならいいのですが、DVDなど映像とあわせると、その時間ラグは無視できません。

ということで、開始時間を1/8まで短縮しバージョンをアップします。

PIC16F87に書き込んで使用してみてください。

バイナリーファイル(1/8スタート)

(さてさて、つづくかな?)