QUAD FN1242A偼幚尰偡傞偐丠丂2013.10.4

1捠偺偙傫側儊乕儖傪偄偨偩偒傑偟偨丅

| 嶐擭偐傜僄儗傾僩偝傫偺乽俹俀俢婎斅乿偑偱傑傢偭偰偐傜丄俢俽俢僆儞儕乕偺俢俙俠偑岼偱偼丄 側偵偐偲榖戣偵側偭偰偍傝傑偡丅 崱偼巹帺恎丄P2D婎斅仺FN1242A婎斅乮僔儞僌儖乯仺儖儞僟乕儖偱挳偄偰偄傑偡偑丄 偙傟偑FN1242A偺怴偨側敪尒偲尵偄傑偟傚偆偐丄側偐側偐椙偄偱偡丅 偦偙偱丄FN1242A僨儏傾儖亊俀偺俢俽俢愱梡婎斅傪惢嶌偟偰捀偗傟偽偲栂憐偟偰偍傝傑偡丅 乮拞棯乯 |

FN1242A偼側偐側偐偄偄壒傪偩偡偺偱丄傑偩傑偩恖婥偁傞傛偆偱偡偹丅

傑偩FN1242A偼儌僲儔儖偱巊偭偨偙偲偼側偄偺偱丄偪傚偭偲専摙偟傑偟傚偆丅

偲偄偆偐丄偪傚偭偲FN1242A傪儌僲偱偮偐偆偺偼寢峔棤僥僋偑昁梫偩偭偨傝偟傑偡丅

偲偄偆偺傕儌僲儔儖儌乕僪偱巊梡偡傞偨傔偺愢柧偼儅僯儏傾儖偺僶乕僕儑儞偵傛偭偰偼婰嵹偑側偐偭偨傝偡傞偺偱丄

側偤偐撲偵曪傑傟偰偄傑偡乮徫乯丅

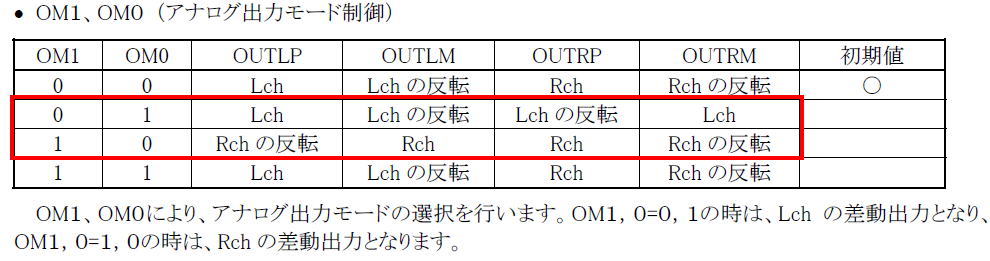

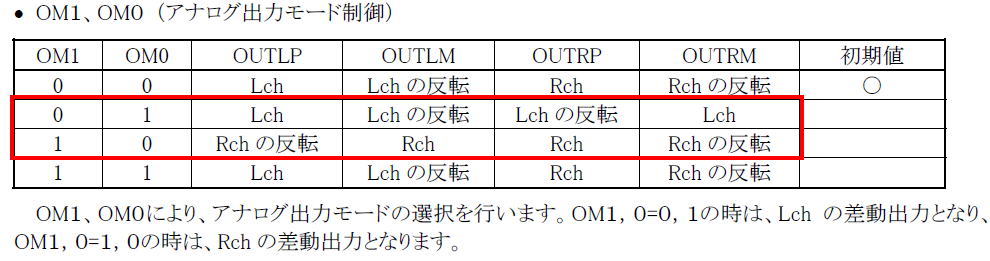

偲偄偆偐丄PCM偱傕儌僲儔儖儌乕僪偱偮偐偆偵偼丄OM0,OM1價僢僩偺曄峏偑昁梫偱偡偑丄偙傟偵偼僜僼僩惂屼偑昁梫偱偡丅

儌僲儔儖儌乕僪偵偡傞偨傔偺愝掕

|

DSD儌乕僪偩偗偵偡傞偵偼栜懱側偄偺偱丄DSD側傜傃偵PCM偱傕巊偊傞傛偆偵峫偊偨偄偲偍傕偄傑偡丅

儅僯儏傾儖偵偼DSD傪儌僲儔儖嵎摦偱偮偐偆応崌偺夞楬椺偑偁傝傑偡偑丄

偙傟偱偼PCM偺応崌偵嵍塃偺埵憡偑曄傢偭偰偟傑偄傑偡丅

儊乕僇偺僨乕僞僔乕僩偺DSD嵎摦弌椡偺愙懕曽朄丅

DSD偱傕PCM偱傕摨偠弌椡埵憡偵側傞傛偆偵偡傞偨傔偵傕丄庒姳偺曄峏偑昁梫偱偡丅

偍偦傜偔壓婰偺傛偆側攝慄偱OK偱偟傚偆丅

偙偺傛偆側愙懕偵偡傟偽DSD偱傕PCM偱傕OK側偼偢偱偡丅

婎斅偵偺傞偐側丠

偞偭偲昁梫側晹昳傪攝抲偟偰傒傑偟偨丅偝偡偑偵係偮偺FN1242A傪嵹偣傞偲偒偮偄偐傕偱偡丅

傕偭偲傕DSD愱梡偲偐偵僔儞僾儖壔偡傟偽偄偄偺偱偡偑丄傗偼傝PCM傕擖椡壜偵偟偨偄偱偡丅

偦偺愗傝懼偊梡偺IC偑彮偟晹昳悢傪懡偔偟偰偟傑偄傑偡偑丄傑偁巇曽側偄偱偟傚偆丅

偩偄偨偄攝慄偑姰椆偟傑偟偨丅

偙傫側偛堄尒傕丂2013.10.6

偙傫側儕僋僄僗僩傪偄偨偩偒傑偟偨丅

|

DSD愱梡偲偡傞側傜丄偲偔偵PIC傕昁梫偁傝傑偣傫偟PCM梡偺兽ОIC傕晄梫偱偡丅

偍偦傜偔DSD傪摦嶌偝偣傞IC埲奜偺慺巕偑側傫傜偐偺塭嬁傪媦傏偡偺偱偼丄偲偺偛堄尒偩傠偆偲偍傕偄傑偡丅

偲偄偆偙偲偱丄偪傚偲偩偗僷僞乕儞傪曄峏偟偰DSD愱梡偵偡傞応崌偵偼丄晄梫側IC傪偡傋偰攔彍偱偒傞傛偆側

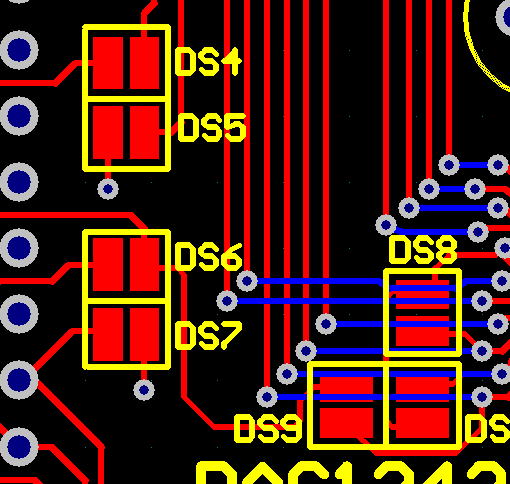

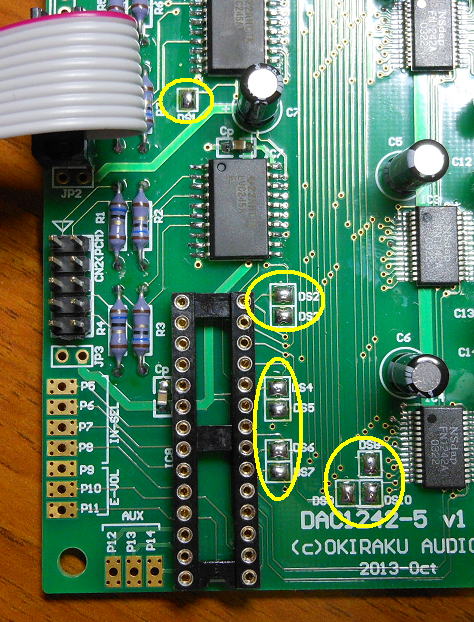

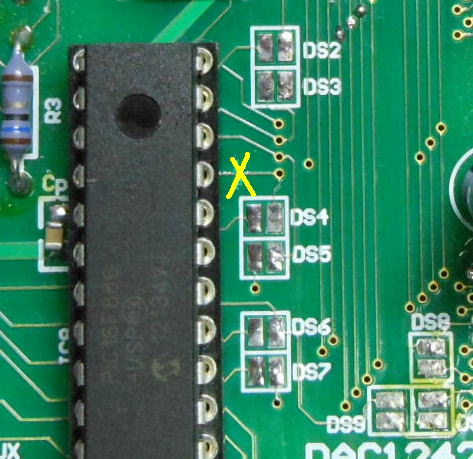

僷僞乕儞傪捛壛偟傑偟偨丅堘偄傢偐傞偐側丠

偡偙偟僷僞乕儞曄峏偱偡丅

婎斅忋偵愝偗偨DS侾乣DS10傪敿揷僕儍儞僷乕偡傟偽丄PIC傗兽ОIC偺幚憰傪晄梫偵偟偰傒傑偟偨丅

偙傟傜偺僕儍儞僷乕抂巕偼丄偁傞堄枴偱婎斅偺僨僶僢僌偵栶棫偮偐傕偟傟傑偣傫丅

敿揷僕儍儞僷乕梡偺僷僞乕儞傪捛壛偟傑偟偨丅

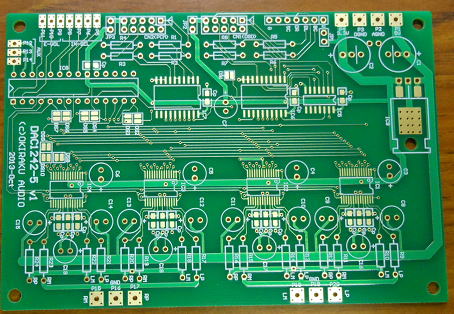

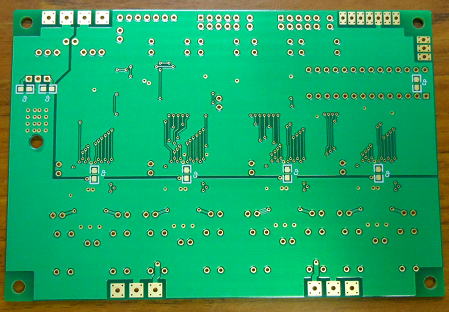

帋嶌婎斅偑偱偒傑偟偨丅丂2013.10.16

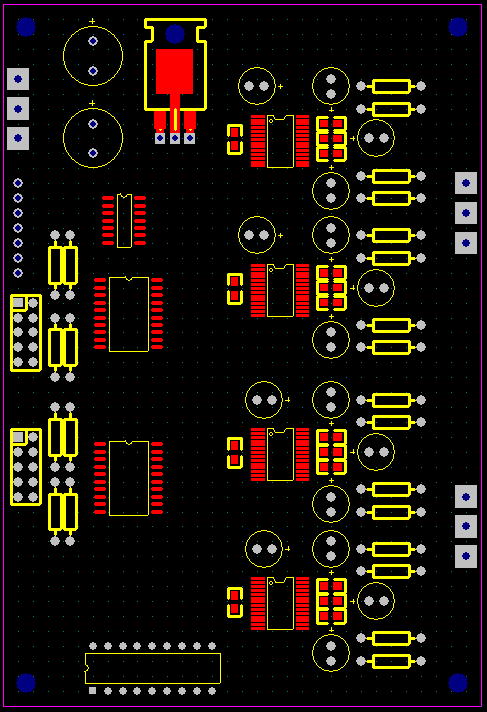

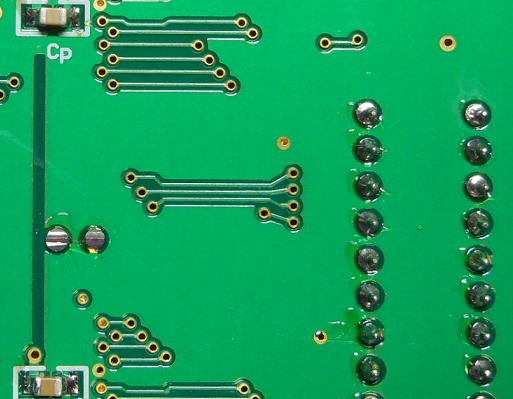

晹昳柺偱偡丅

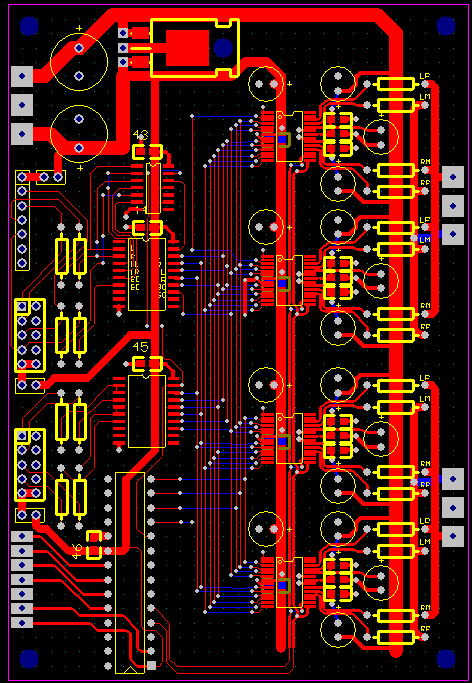

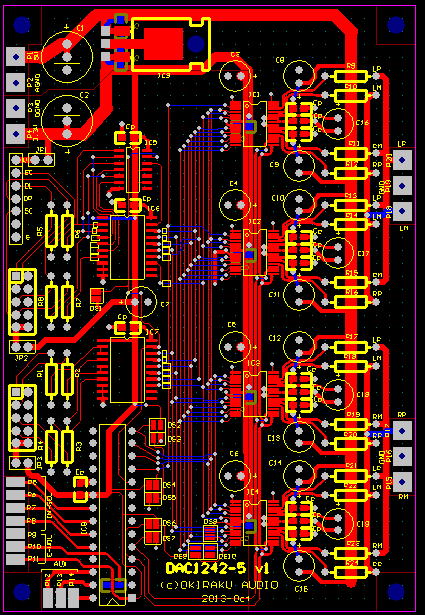

敿揷柺偱偡丅

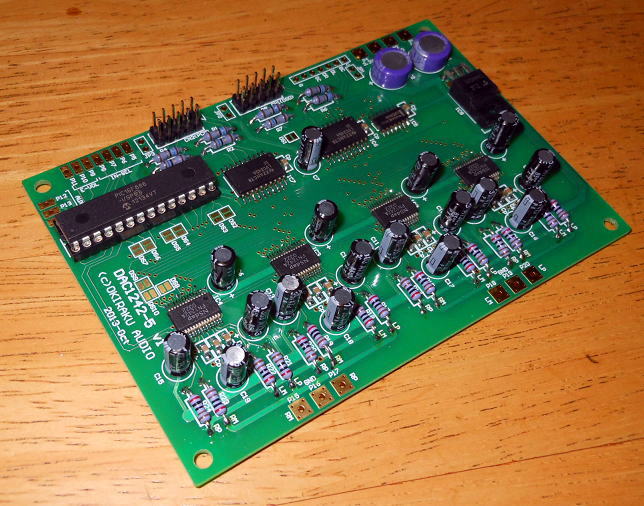

傑偢偼晹昳傪幚憰両

偍弌偐偗梡偺幨恀偐側丅

僐乕僪僱乕儉偼俢俙俠侾俀係俀亅俆偱偡丅枛旜偺亅俆偼埲慜偵俹俠俵1794傪係偮巊偭偨俢俙俠偺僐乕僪僱乕儉偑

俢俙俠侾俈俋係亅俆側偺偱丄俢俙俠慺巕係屄巊偄偺婎斅偺枛旜偼亅俆偲偡傞偙偲偵偟傑偟偨丅

摦嶌妋擣両丂2013.10.20

傑偢偼DSD愱梡儌乕僪

惂屼僜僼僩傪慻傕偆偲偟偰丄PIC偺俬俷僺儞偺掕媊傪偟偰偄偨傜丄廳戝側栤戣偑偁傞偙偲偵婥偯偒傑偟偨丅

徻嵶偼屻弎偡傞偲偟偰丄傑偢偼俢俽俢愱梡儌乕僪偱摦嶌偝偣傑偟傚偆両

俢俽俢愱梡儌乕僪偱偼俹俬俠偼昁梫偁傝傑偣傫丅婎斅忋偺俢俽侾偐傜俢俽侾侽傪偡傋偰敿揷僕儍儞僷乕偵偟傑偡丅

俢俽俢儌乕僪偺愝掕丅DS1-10傪敿揷僕儍儞僷乕丅俹俬俠偼晄梫丅

俢俽俢僜乕僗傪梡堄偟傑偟傚偆丅

俢俽俢僜乕僗偵偼僄儗傾僩偝傫偺倀俽俛亅俢俙俠偑偁傞偺偱偡偑弌椡偺埵憡偺妋擣摍傪偡傞偵偼惓尫攇側偳偺

掕忢怣崋偑偁傞偲曋棙偱偡丅偦偆偄偭偨俢俽俢偺僨乕僞僼傽僀儖傪嶌惉偟偰傕偄偄偺偱偡偑丄庤尦偵埲慜偵

俢俽俢僜乕僗偲偟偰夵憿偟偨俙俢曄姺婎斅偑偁傞偺偱偦傟傪偮偐偆偙偲偵偟傑偟偨丅

丂婎斅傪扵偟偰偩偟偨偺偼偄偄偺偱偡偑丄偙偺婎斅偐傜偼僔僗僥儉僋儘僢僋偲側傞弌椡偑偱偰偄傑偣傫丅

偲偄偆偙偲偱俛俠俲怣崋傪係攞偟偨怣崋傪偮偔傞偨傔偵俬俠俽570傪捛壛偱搵嵹偡傞偙偲偵偟傑偟偨丅

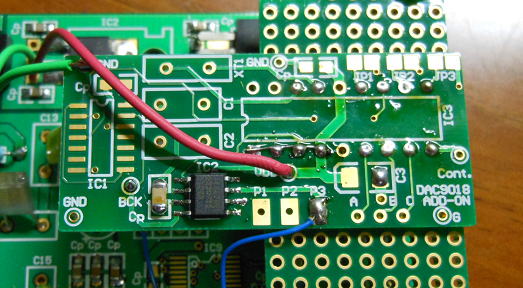

俢俽俢僜乕僗梡偵夵憿偟偨俢曄姺婎斅乮僔僗僥儉僋儘僢僋捛壛斉乯丅

俬俠俽570偼SO-8僷僢働乕僕(1.27mm僺僢僠乯側偺偱丄曄姺婎斅偑昁梫偵側傝傑偡偑庤尦偵DAC9018S偺僋儘僢僋掽攞婎斅偑

偁偭偨偺偱丄偙傟傪棳梡偡傞偙偲偵偟傑偟偨丅偦偆偡傟偽攝慄悢傕尭傞偺偱惢嶌偑妝偵側傝傑偡丅

DAC9018S僋儘僢僋掽攞婎斅傪妶梡偟偰俛俠俲偺係攞怣崋乮俽俠俲乯傪嶌惉偟傑偟偨丅

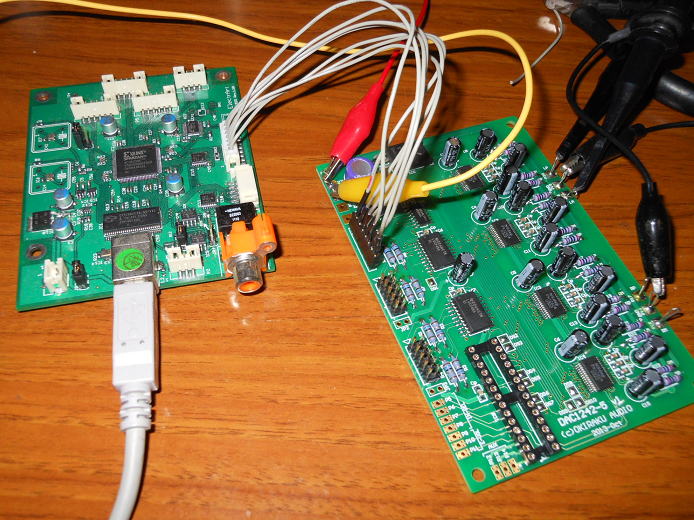

愙懕偟偰傒傛偆両

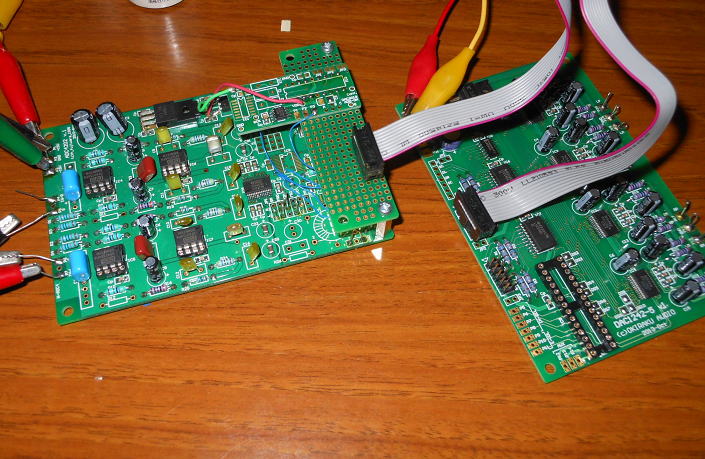

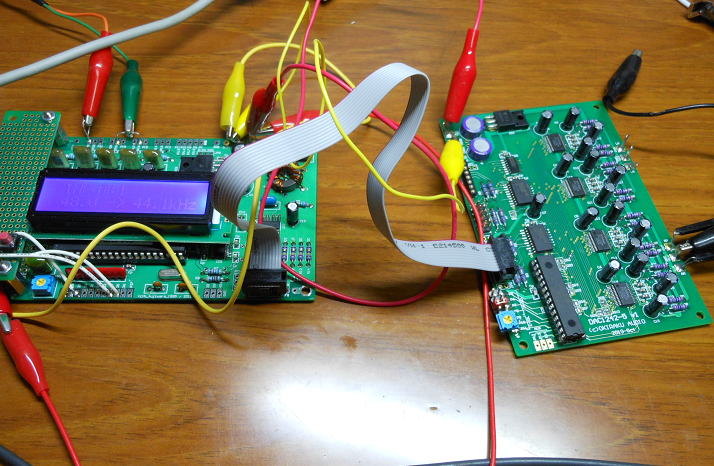

偙偆偟偰俢俽俢僜乕僗偑弌棃忋偑傝傑偟偨丅偱偼丄俢俙俠1242-5偲愙懕偟偰傒傑偟傚偆丅

俢俽俢僜乕僗偲俢俙俠侾俀係俀亅俆偲傪愙懕偟偰摦嶌妋擣偱偡丅

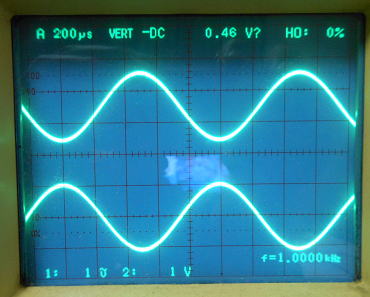

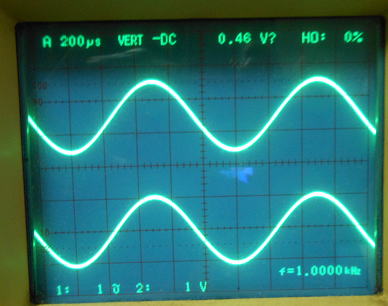

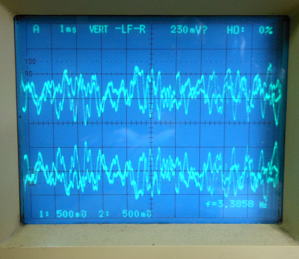

弌椡偺妋擣偼怣崋偑惓忢偵弌偰偄傞偐偳偆偐偲丄埵憡偺僠僃僢僋偱偡丅

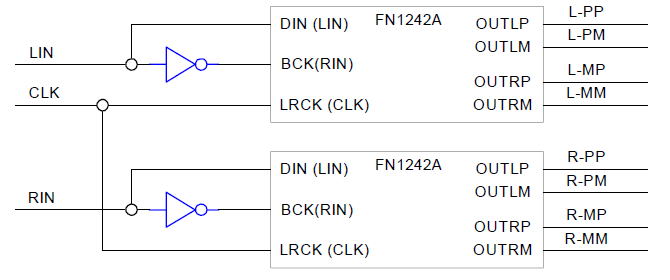

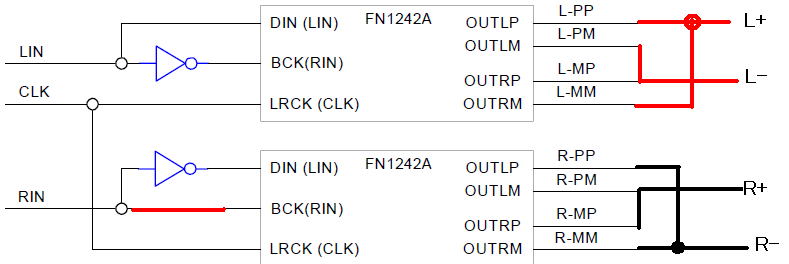

俼丆俴偦傟偧傟偺弌椡偼

俼偺弌椡偼俼俹乮惓丗旕斀揮乯丄俼俵乮晧丗斀揮乯偱偡丅摨條偵俴偺弌椡偼俴俹乮惓丗旕斀揮乯丄俴俵乮晧丗斀揮乯偱偡丅

傑偢偼丄偦傟偧傟偺僠儍儞僱儖偺弌椡偺埵憡偑斀揮偟偰偄傞偐偳偆偐偺妋擣偱偡丅

偙傟偼俥俶1242俙偑摦偄偰偄傟偽栤戣偼側偄偼偢偱偡丅

傑偢偼摦嶌偟偰偄傞偙偲傪妋擣偟傑偟偨丅

丂

丂

俼俹偲俼俵偺弌椡丅屳偄偵埵憡偼斀揮偟偰偄傑偡丅

師偼俴丆俼偺弌椡埵憡偑堦抳偟偰偄傞偐偳偆偐偺妋擣偱偡丅偙傟傕栤戣側偄傛偆偱偡偹丅

俼俹偲俴俹偺弌椡丅俀偮偺埵憡偼堦抳偟偰偄傑偡丅

倀俽俛亅俢俙俠偲愙懕偟偰傒傑偟傚偆両

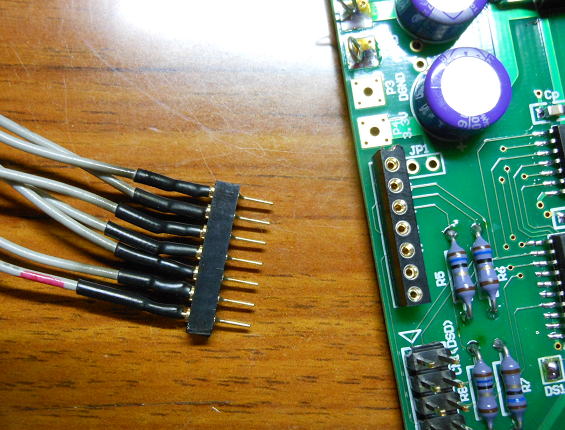

僄儗傾僩偝傫偺倀俽俛亅俙倀俢俬俷偲愙懕偟偰傒傑偟偨丅愙懕偼俈僺儞偺僐僱僋僞偱峴偄傑偡偑丄

庤帩偪偺楢寢僺儞偲俬俠僜働僢僩傪梡偄偰愙崌晹傪慻傒棫偰傑偟偨丅

偙傫側姶偠偱僐僱僋僞晹傪慻傒棫偰傑偟偨丅

僐僱僋僞傪愙懕偡傟偽摦嶌妋擣偺娐嫬偼惍偄傑偡丅

倀俽俛亅俙倀俢俬俷偲俢俙俠1242-5偲偺愙懕丅

摦嶌偵偼幚嵺偺壒妝僜乕僗傪巊偭偰偄傑偡偑丄栤戣側偔摦偒傑偡偹丅

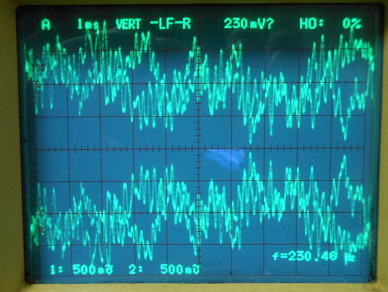

弌椡攇宍丅嵎摦弌椡側偺偱埵憡偑斀揮偟偰偄傑偡丅

廳戝側栤戣偲偼丒丒丒丂2013.10.2侾

PCM擖椡帪偼FN1242A傪PIC偱僔儕傾儖惂屼偟傑偡偑丄偡傋偰偺愝掕偑僔儕傾儖惂屼偱偒傞偲巚偄崬傫偱偄偨僼僔偑偁傝傑偡丅

偡側傢偪擖椡僼僅乕儅僢僩乮塃媗丄嵍媗丄I2S乯偺愝掕傕僔儕傾儖惂屼偱偒傞傕偺偲巚偭偰偄傑偟偨丅

懠偺DAC偵偮偄偰偼僔儕傾儖惂屼帪偼傎傏偡傋偰偺愝掕傪峴偆偙偲偑偱偒傑偡丅

仸偦傟偲傕丄扨偵PIC偲FN1242A偺FMT0乣3偺抂巕傊偺愙懕傪朰傟偨偺偐傕丒丒丒

偁偨傜傔偰丄僔儕傾儖惂屼偱曄峏偱偒傞僐儅儞僪偵偼FMT偺崁栚偑偁傝傑偣傫丅傫乣晄巚媍側DAC偩丅

僔儕傾儖惂屼偱偒傞崁栚偵FMT0乣俁偺崁栚偑偁傝傑偣傫丅 |

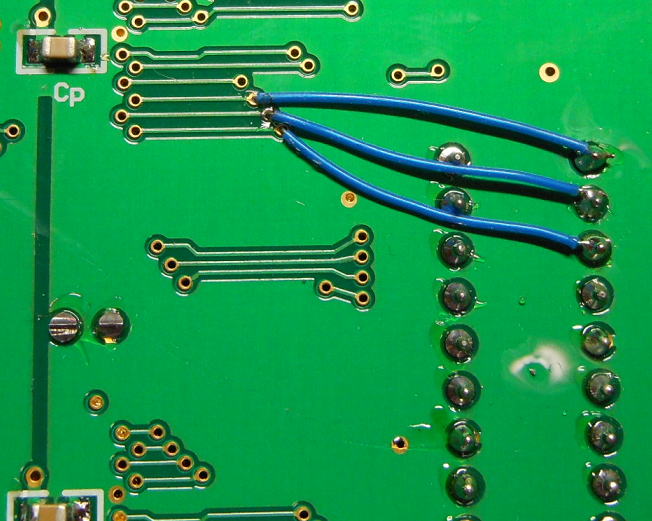

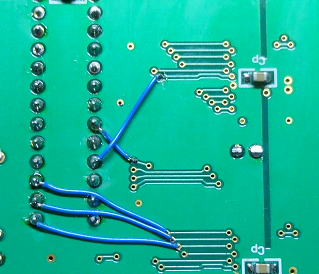

偍傕傓傠偵僕儍儞僷乕傪

FMT0乣俁偺惂屼傪PIC偱偱偒傞傛偆偵丄PIC偺嬻偒抂巕偐傜僕儍儞僷乕傪旘偽偟傑偟偨丅偪傚偆偳丄俁杮暘偺僕儍儞僷乕傪捛壛偱偡丅

嬤偔偵丄揔摉側儔儞僪偑偁偭偨偺偱偦偙傪棙梡偟偰丄僕儍儞僷乕慄傪旘偽偟傑偟偨丅

丂

丂

僕儍儞僷乕慄傪旘偽偡慜丅丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂僕儍儞僷乕慄傪旘偽偟偨忬懺丅

偝偰丄偙傟偱偡傋偰偺惂屼偑PIC偐傜偱偒傞偼偢偱偡丅

偲偄偆偙偲偱丄DSD愱梡儌乕僪偺偲偒偵抁棈偝偣偰偄偨DS侾乣侾侽偺敿揷僕儍儞僷乕晹傪偡傋偰媧偄庢傝傑偡丅

DS1乣侾侽偼偡傋偰敿揷傪媧偄庢傝傑偡丅

DSD偺摦嶌妋擣

傑偢偼僜僼僩偵DSD摦嶌傪彂偒崬傫偱丄摦嶌妋擣偱偡丅

惂屼曽朄偲偟偰偼丄FN1242A傪儕僙僢僩偟偨忬懺偱丄FN1242A偺抂巕傪DSD婲摦偵偡傞傛偆偵PIC傪愝掕偟偨偺偪丄

儕僙僢僩傪夝彍偟傑偡丅

栤戣側偔DSD偱摦嶌偟傑偟偨丅

師偼PCM偱偺摦嶌妋擣 2013.10.22

PCM怣崋偺僜乕僗偲偟偰偼丄偱偒傟偽RenewFFASRC傪巊偄偨偄偲偙傠偱偡偑丄傑偩僜僼僩偑姰惉偟偰偄側偄偺偱

偙偙偼FFASRC傪巊偄傑偟偨丅DAC1242-5偺庴怣僼僅乕儅僢僩傪RJ(塃媗乯丄LJ乮嵍媗乯丄I2S摍傪曄峏偟偰

栤戣側偔庴怣偱偒傞偙偲傪妋擣偟傑偟偨丅

PCM怣崋偺擖椡偱偺摦嶌妋擣拞偱偡丅僜乕僗偼FFASRC傪巊偭偰偄傑偡丅

偮偄偱偵揹巕儃儕儏乕儉婡擻傕丒丒丒丒偁傟丠丂

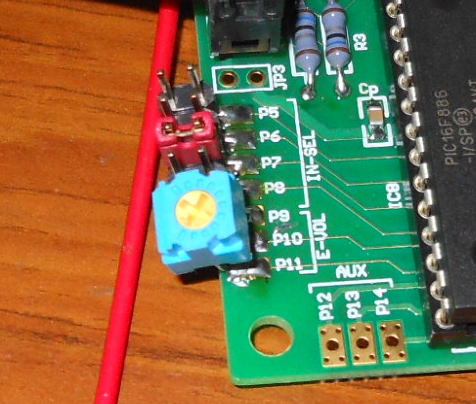

揹巕儃儕儏乕儉婡擻傕庢傝晅偗傜傟傞傛偆偵VR傕偲傝偮偗偰傒傑偟偨丅

VR傪庢傝晅偗傑偟偨両

VR偺揹埑弌椡傪AD曄姺偟偰偦偺傑傑FN1242A偺儗僕僗僞偵彂偒崬傓僾儘僌儔儉傪嶌惉偟偰摦嶌妋擣傪峴偄傑偟偨偑丄

偁傟傟丠懠偺DAC慺巕偲偼堘偄丄VR偺埵抲偵懳偟偰儕僯傾偵怳暆偑曄傢傝傑偡丅側傫偐丄曄偱偡丅

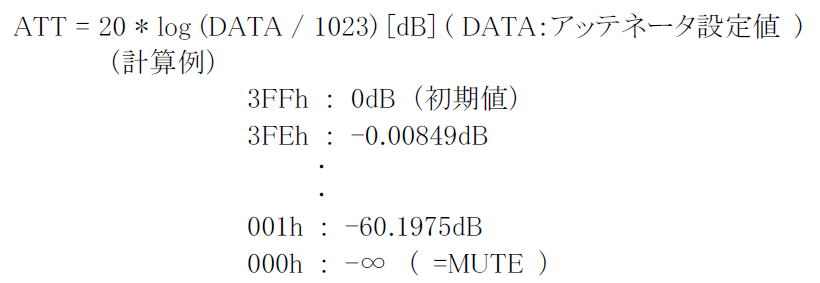

儅僯儏傾儖傪嵞妋擣偡傞偲丄尭悐棪偼師偺傛偆偵側偭偰偄傞傛偆偱偡丅

|

偙傟偭偰丄DATA乮VR偺揹埑抣乯偵懳偟偰儕僯傾偵曄壔偡傞幃偱偡偹乮徫乯丅

A僇乕僽乮懳悢乯偺VR傪巊偊偽揹巕儃儕儏乕儉偲偟偰巊偊偦偆偱偡丅偱傕杮棃偼揹巕儃儕儏乕儉偲偟偰偺梡搑偲偄偆傛傝偼丄

懠偺婡婍偲偺弌椡儗儀儖嵎傪崌傢偣傞偨傔偺儃儕儏乕儉婡擻偲偟偰峫偊偨傎偆偑傛偝偦偆偱偡丅

丂側偍揹巕儃儕儏乕儉偑婡擻偡傞偺偼PCM擖椡偺傒偱丄DSD擖椡偱偼婡擻偟側偄傛偆偱偡丅

僜僼僩偺峔惉偼

偙傫側姶偠偱偱擖椡偺僼僅乕儅僢僩傪慖戰偱偒傞傛偆偵偟傑偟傚偆丅

僨僼僅儖僩偼DSD偱偡丅

擖椡僼僅乕儅僢僩偺愝掕乮H:奐曻丄L:GND)

| 擖椡FORMAT | 丂DSD丂 | 丂I2C (16-24) |

LJ (16-24) |

丂RJ丂 (16) |

丂RJ丂 (24) |

| 抂巕丂P5 | H | L | H | H | H |

| 抂巕丂P6 | H | H | L | H | H |

| 抂巕丂P7 | H | H | H | L | H |

| 抂巕丂P8 | H | H | H | H | L |

仸丂I2C丗IIS丂format丂LJ:Left Justified(慜媗傔乯 RJ:Right Justified乮屻媗傔乯

揹巕儃儕儏乕儉愙懕乮PCM擖椡偺傒乯

| 婡擻丂 | |

| 抂巕丂P9 | GND |

| 抂巕丂P10 | VR(2)擖椡 |

| 抂巕丂P11 | Vdd(3.3V) |

偦偺懠偺抂巕偼MUTE儕儗乕傪嬱摦偡傞偨傔偵丄偦傟偧傟帪娫嵎傪摼偰L仺H儗儀儖偵側傞傛偆偵偟傑偟偨丅

MUTE丂RELAY惂屼

| 婡擻 | |

| 抂巕丂P12 | 梊栺 |

| 抂巕丂P13 | 栺1.5昩屻偵L仺H偵曄壔 |

| 抂巕丂P14 | 栺3昩屻偵L仺H偵曄壔 |

偙傟偱僜僼僩姰惉偐側丠

帋挳偼RenewFFASRC偲偁傢偣偰偍偙側偄傑偟傚偆両

僜僼僩偺堦晹夵憿斉傪嶌偭偰傒傑偟偨丅丂2014.14.24

DAC1242-5偱偼FN1242A傪儌僲儔儖儌乕僪偱摦嶌偝偣傞偨傔偵丄僜僼僩惂屼傪峴偭偰偄傑偡偑丄FN1242A偼彮偟暼偑偁傝丄

廫暘偵崅偄僔僗僥儉僋儘僢僋偑擖偭偰偄側偄偲僜僼僩儌乕僪偑摦嶌偟側偄忬嫷偑偁傞傛偆偱偡丅

偦偺偨傔丄偨偲偊偽DAI偑棫偪忋偑傞慜偵DAC1242-5偑棫偪忋偑傞(揹尮搳擖屻0.5昩屻乯偲丄

PCM擖椡帪偵怣崋偑偒偰偄側偄忬懺偱摦嶌傪奐巒偡傞偨傔丄惓忢偵棫偪忋偑傜側偄壜擻惈偑偁傝傑偡丅

丂偙傟傪夞旔偡傞偨傔偵偼

丂丂嘇DAC1242-5偺棫偪忋偑傝帪娫傪廫暘偵抶偔偡傞乮椺偊偽俆昩偔傜偄偺梋桾帪娫傪傕偨偣傞乯丅

丂丂嘆庒姳僷僞乕儞傪曄峏偟偰丄BCK怣崋傪僙儞僗偟偰丄擖椡偑妋掕偟偰偄傞偙偲傪妋擣偟偨偆偊偱僜僼僩惂屼傪峴偆

偺俀僷僞乕儞偑峫偊傜傟傑偡丅

嘇偵偮偄偰偼幚尰偼娙扨偱偡丅僾儘僌儔儉偺掕悢傪曄峏偡傞偩偗偱偡丅

嘆偵偮偄偰偼丄壓婰偺傛偆偵廋惓偑昁梫偱偡丅

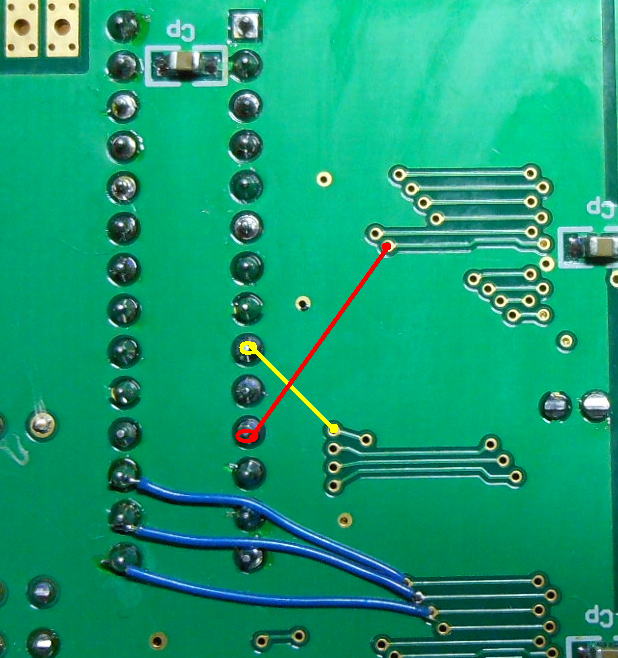

嘇BCK怣崋傪僙儞僗偡傞夵憿傪峴偆応崌偺庤弴

乮侾)庤弴侾

丂PIC乮IC8)偺Pin11偵擖傞儔僀儞傪僇僢僩偡傞丅壓恾偺墿怓偺亊報偺偲偙傠傪愗抐丅

墿怓慄傪僇僢僩

乮侾)庤弴俀

丂壓恾偺俀売強乮墿怓慄丄愒怓慄乯傪愙懕偡傞丅側偍丄壓恾偱偼V1婎斅偱偡偺偱惵怓偺僕儍儞僷慄偑俁杮偁傝傑偡偑丄

偙傟偼柍帇偟偰偔偩偝偄乮V2婎斅偱偼偁傝傑偣傫乯丅

丂丂丂

丂丂丂 丂

丂

墿怓慄丄愒怓慄傪愙懕偡傞丅丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂曄峏椺

乮俁乯庤弴俁丂

丂PIC偺僜僼僩傪擖傟懼偊傞丅

埲忋偑廋惓偺奣梫偵側傝傑偡丅偙傟傜偺夵憿偼晄梫側応崌偑傎偲傫偳偐傕偟傟傑偣傫偑丄婎斅偺慻傒崌傢偣偵傛傝

忋婰偺夵憿偑昁梫偵側傞偐傕偟傟傑偣傫丅

丂偦偺偨傔偙偺夵憿偵懳墳偟偨PIC傪儕儕乕僗偟傑偡丅壓婰偺梫椞偲偝偣偰偄偨偩偒傑偡偺偱丄偛婓朷偺曽偼偛楢棈偔偩偝偄丅

乮侾乯PIC傪憲晅偟偰彂偒姺偊屻偵曉憲丅

丂曉憲梡偺晻摏傪摨晻偺忋丄憲晅偔偩偝偄丅憲晅愭偼儊乕儖偵偰偛楢棈偟傑偡偺偱丄傑偢乽DAC婎斅乿傪審柤偵偟偰儊乕儖偔偩偝偄丅

丂側偍憲晅帪偵偼壓婰偺偳偪傜偺Ver傪彂偒姺偊傞偐傪柧帵偔偩偝偄丅

丂丂嘇Ver3丗丂揹尮ON帪偺棫偪忋偑傝偺僨傿儗僀僞僀儉傪俆昩偵愝掕偡傞丅

丂丂嘆ver俀丗丂BCK傪僙儞僗偟偰摦嶌偝偣傞丅

(2)幚旓偱偺敪憲

丂彂偒崬傒偟偨PIC傪憲晅偟傑偡丅旓梡偼400墌偵側傝傑偡偑丄憲椏偑壛嶼偝傟傑偡丅

丂偳偪傜偺ver偵偡傞偐傪偛巜掕偔偩偝偄丅

丂丂嘇Ver3丗丂揹尮ON帪偺棫偪忋偑傝偺僨傿儗僀僞僀儉傪俆昩偵愝掕偡傞丅

丂丂嘆ver俀丗丂BCK傪僙儞僗偟偰摦嶌偝偣傞丅

(3)PIC儔僀僞傪偍帩偪側傜彂偒崬傓丅

丂壓婰偵僼傽僀儖傪擖傟偰偍偒傑偡丅側偍僆儕僕僫儖偺僶乕僕儑儞偼UP偟傑偣傫偺偱丄

丂彂偒姺偊帪偼廫暘偵拲堄偔偩偝偄乮怴偟偄PIC傪梡堄偟偰偔偩偝偄乯丅

丂

丂丂嘇Ver3丗丂揹尮ON帪偺棫偪忋偑傝偺僨傿儗僀僞僀儉傪俆昩偵愝掕偡傞丅

丂丂丂丂丂丂丂仺V3HEX僐乕僪丅

丂丂嘆ver俀丗丂BCK傪僙儞僗偟偰摦嶌偝偣傞丅

丂丂丂丂丂丂丂仺V2HEX僐乕僪丅

丂