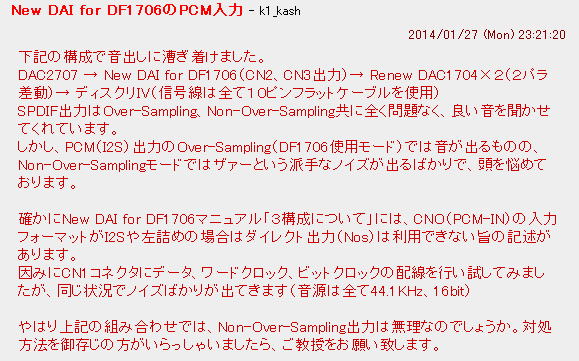

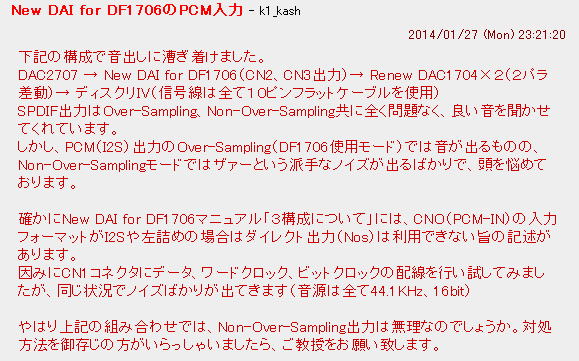

こんな投稿をいただきました。

たしかにPCM1704を動かすにはDAIからの出力は右詰24Bitフォーマットが必要ですが、

多くのDAIではI2Sフォーマットが多いのも事実です。それらを見かけ上で右詰フォーマットに

変更すれば、多くのソースでPCM1704をディジタルフィルターなしで、直接つなぐことができます。

フォーマットは?

PCMフォーマットの変換について 2014.1.29

こんな投稿をいただきました。

たしかにPCM1704を動かすにはDAIからの出力は右詰24Bitフォーマットが必要ですが、

多くのDAIではI2Sフォーマットが多いのも事実です。それらを見かけ上で右詰フォーマットに

変更すれば、多くのソースでPCM1704をディジタルフィルターなしで、直接つなぐことができます。

フォーマットは?

しかし、なんでPCM出力に複数のフォーマットがあるんでしょうね?メーカのエゴかな?

個人的には右詰より左詰の方が合理的なので、左詰フォーマットに統一したらと思うのですが、

DAC素子の立場に立てば右詰フォーマットが合理的なのもうなづけます。ただし、右詰にすると

ビット数を明示しなくてはいけない問題があるんですよね。その点、左詰ならビット数の影響は

あまりありません。下位のビットは無視するだけですから。

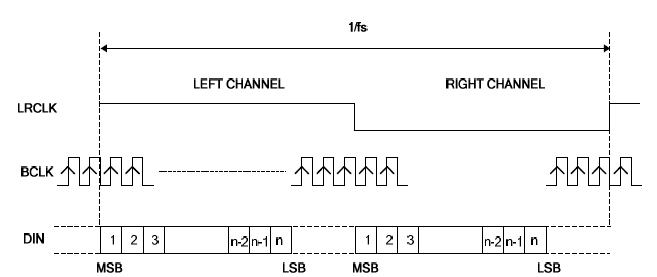

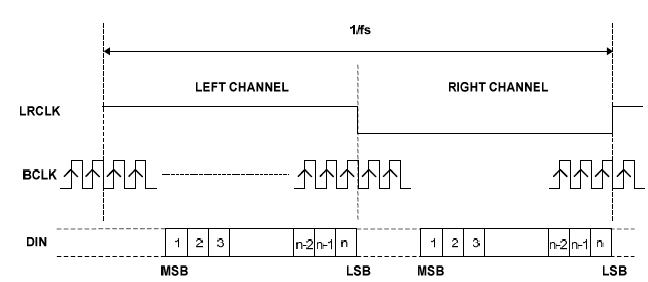

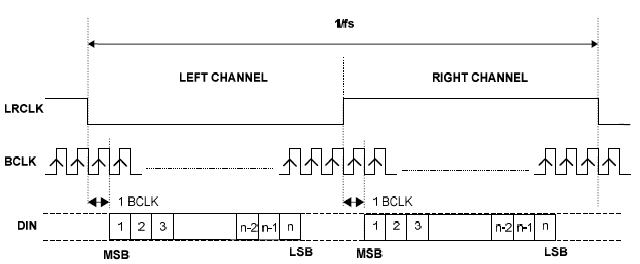

さて、いくつもあるフォーマットですが、何が異なるかといえば単にLRCKの位相とタイミングがずれているだけです。

この変更はシフトレジスターがあれば簡単に変更できます。

| 左詰フォーマット LEFT JUSTFIED |

|

| 右詰フォーマット RIGHT JUSTFIED |

|

| I2Sフォーマット I2S JUSTFIED (PHILIPS FORMAT) |

|

早速試してみましょう!

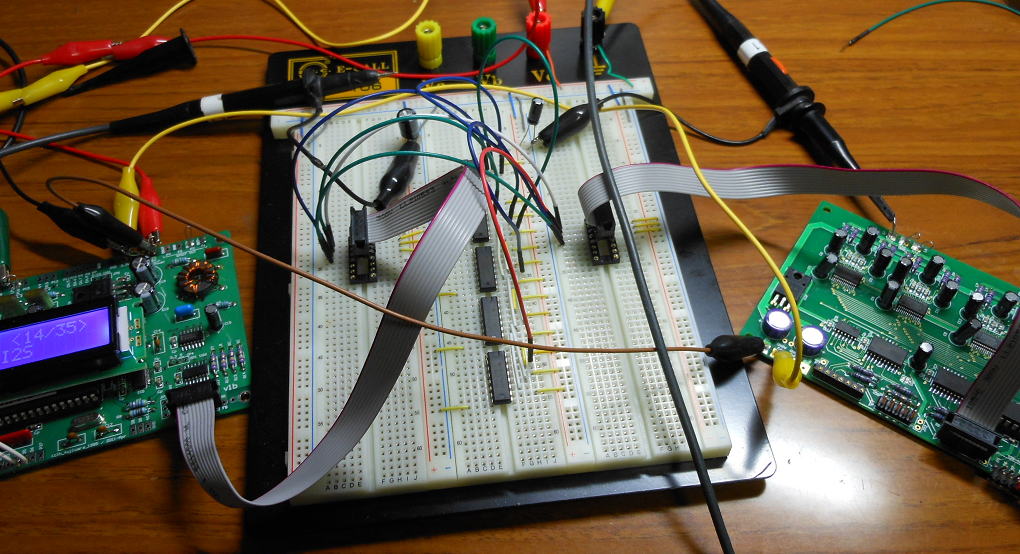

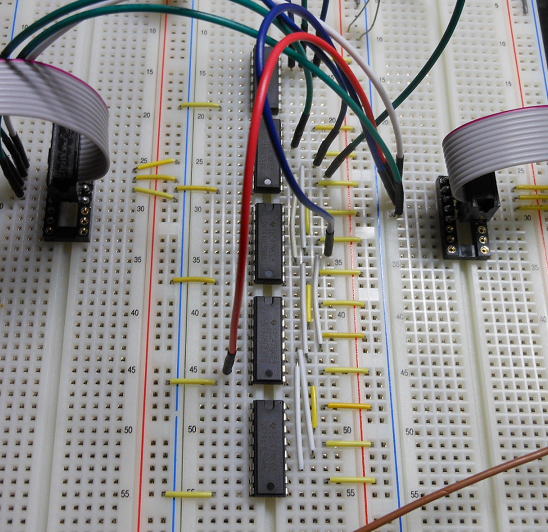

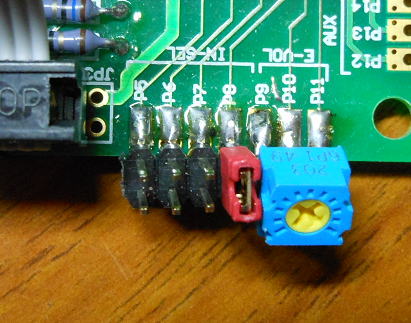

手元にDIPタイプのシフトレジスタがあったので、それを並べてブレッドボードで組み立ててみました。

構成は FFASRC→PCM変換回路→DAC1242-5(RJ24受け) です。

こんな構成です。

素子はシフトレジスタ4個とインバータ1個の計5個です。

FFASRCの設定は

FFASRCの出力はPC2707を出力を模擬して、16BitのI2Sフォーマットに設定します。

フォーマットはI2Sです。

ビット数は16です。

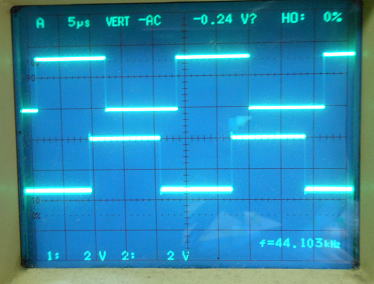

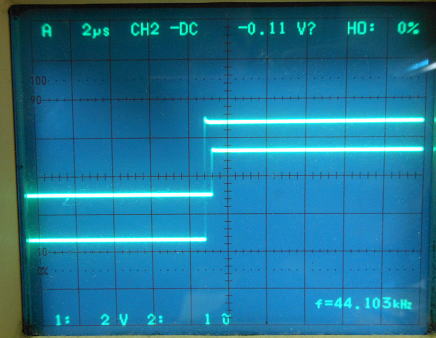

入力と出力のLRCKの位相を確認すると、ちゃんと出力の位相が早まっていることがわかります。

実際には入力の位相をかなり遅らせて出力しています。未来に信号を与えることはできませんからね。

入出力のLRクロックです。入出力で位相がずれているのがわかります。

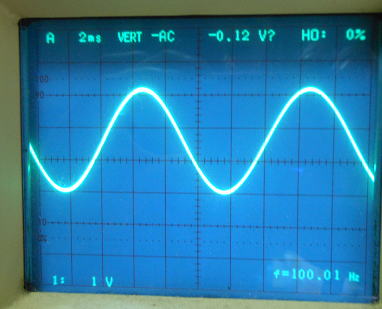

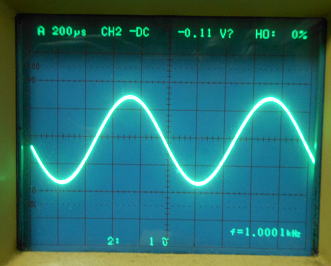

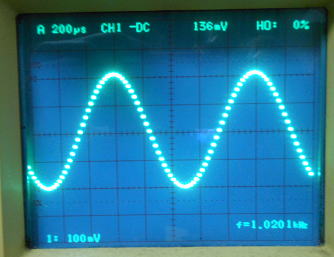

出力を確認してみましょう!

DAC1242-5の受け側が右詰24Bitに変更してます。

DAC1242-5の設定

問題なしですね!

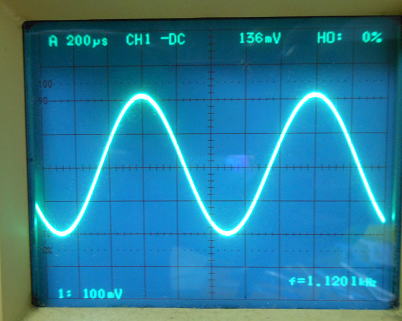

DAC1242-5の出力から正常な正弦波を得ることができました。

この変換回路でI2S→RJ24ができることが確認できました。

本当は、すべてのフォーマット間での変換ができるので便利な回路かもしれません。

無事アナログ出力も得られました。

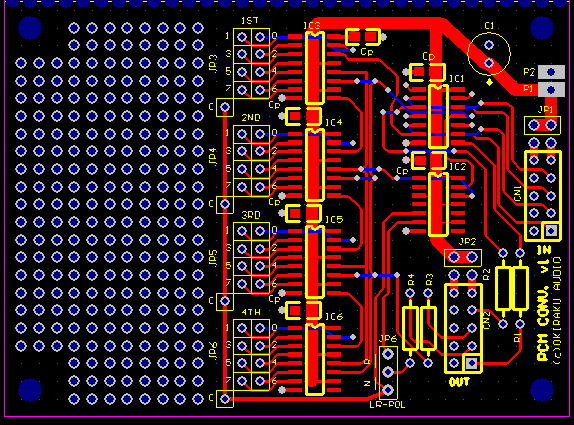

基板にするかな?

汎用的なPCMのフォーマット変換基板があると便利そうでしが、どうしましょう?

えい!

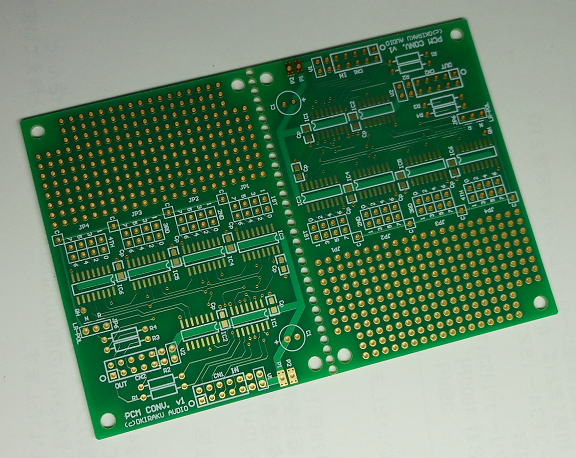

まずは描いてみました。

コネクタ位置はDAC2707と合わせるため、すこし変則的になっています。

ICはバッファーを1つ入れたので、計6個になりました。

基板にするとこんな感じです。

こんな感じで 2014.2.4

小さい変換基板だし、汎用的につかえそうなのでDAC2707と同じサイズでつくりました。

まずはこれで試作してみましょう!

こんな感じです。

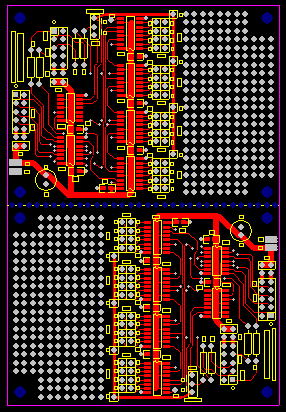

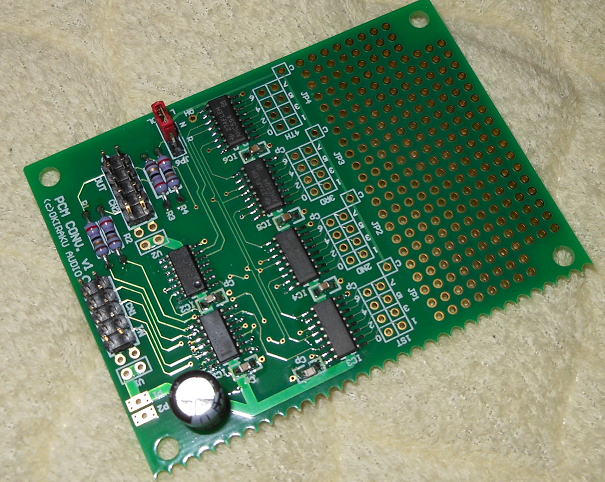

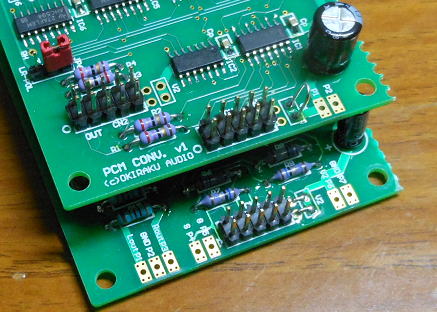

基板が出来上がりました。2014.2.11

DAC2707のサイズとあわせるために、2枚綴りになっています。

基板完成!

さっそく組み立てましょう。チップICが6個と抵抗4個、チップコンデンサ6個、コンデンサ1個、その他ジャンパーピン3個等

だけなので、10分もあれば完成します。もっとも部品を準備する時間がその倍くらいかかりますが(笑)。

もっと部品箱を整理しないといけないな〜っといつもおもいます。

部品を取り付け完成です。どうやったら写真がうまくとれるだろう?

動作確認!

FFASRCと接続して動作確認です。構成は

FFASRC→PC変換基板→DAC1242-5(RJ24受け)

です。

動作確認の様子です。

一番厳しい条件は192kHzでの動作ですが、問題なく動作しました。

192kHzにFFASRCを設定しました。

DAC1242-5の出力も確認です。

すこし細かく。

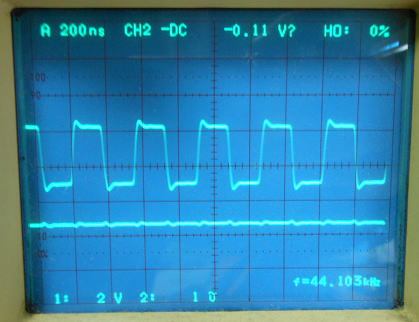

きちんとLRCKの位相が遅れているかどうか確認してみました。ちょうど1BCK分遅れる設定にして確認してみました。

44.1kHzだとBCKは44100/64=28224002Hz(2.8224MHz)になります。波長でいうば354nSになります。

下図の波形からちゃんとそれだけの位相遅れになっていることが確認できます。

LRクロックの位相ずれ(ちょうど1BCK分おくらした場合) BCK信号(波長は354nsです)。

ここで、すこしフォーマット変換の場合の設定値を整理しておきましょう!

| 元フォーマット | 変換フォーマット | 位相遅れ設定値 (×BCK) |

位相 | 備考 |

| I2S | RJ16(右詰16Bit) | 17(JP3-0) | 非反転N | DAC2707からの変換に適 |

| I2S | RJ24(右詰24Bit) | 25(JP4-0) | 非反転N | DAC2707からの変換に適 |

| RJ16 | RJ24 | 8(JP1-7) | 非反転N | |

| RJ24 | RJ16 | 24(JP3-7) | 反転R | |

| RJ16 | I2S | 15(JP2-6) | 反転R | |

| RJ24 | I2S | 7(JP1-6) | 反転R |

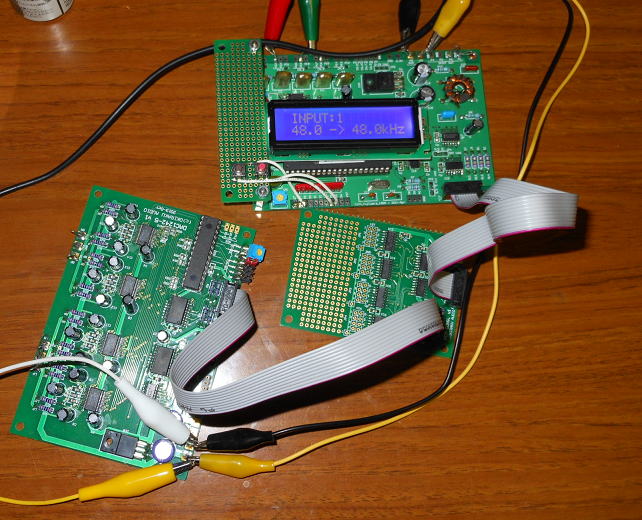

DAC2707とつないでみよう! 2014.2.13

最後の確認としてDAC2707と繋いでみましょう。DAC2707と本基板はコネクタ位置と電源端子位置が一致しているので、

2階建にすることが簡単ですが、すでにピンを立てていることもあり、10Pのフラットケーブルで繋ぎます。

DAC2707とピン配置はおなじです。

全体の動作確認の様子です。

接続は

DAC2707 → PCM変換基板 → NewDAI for DF1706 → Renew

DAC1704

になります。

動作確認の様子です。

問題なしですね。

Non OversampligモードでもDF1706モードでも両者とも動くことが確認できました。ちゃんとDAC2707のIISフォーマットが

右詰24Bitに変換されていることがわかります。

Non-OverSamplig modeで動作 Oversampling(DF1706)で動作。

これで動かす場合にはNew DAIのJP3はすべて外しています。右詰24ビットモードの設定になります。)

New DAIの設定です。

そろそろマニュアル書いてリリースしましょう。

(つづく)